面向基带处理的异构多核架构软硬件平台设计

2017-03-31曾定立丁国杰

曾定立,丁国杰

(1.重庆邮电大学 宽带无线移动互联网络实验室,重庆 400065;2.中国科学院计算技术研究所 无线通信技术研究中心)

面向基带处理的异构多核架构软硬件平台设计

曾定立1,丁国杰2

(1.重庆邮电大学 宽带无线移动互联网络实验室,重庆 400065;2.中国科学院计算技术研究所 无线通信技术研究中心)

通过研究现代通信系统集中化处理架构中基带处理单元(BBU)的特点,将异构多核处理器应用于BBU中,并提出将物理层算法与控制分离的观点。在ARM+DSP的异构多核中,ARM完成物理层控制,DSP完成物理层算法的功能,提升了BBU基带处理能力,并给出完整的BBU硬件架构以及功能实现。提出了一种应用于基带处理中的异构多核软件架构,从软件层面上实现了对底层硬件的虚拟化,引入了中间件的概念,屏蔽了ARM与DSP操作系统上的差异,并给出基于Linux的非对称系统(AMP)的构建及移植方法,包括异构多核的BootLoader、AMP系统的设计与移植。

基带处理单元;异构多核;ARM;DSP;中间件;BootLoader;AMP系统

引 言

移动通信系统向LTE演进过程中,各项指标和性能都在提高,造成基带处理器的负担急剧加重,因此,对基带处理单元(BBU)的处理速度提出了更高要求,研发出具有性能更强、灵活性更好的新型绿色基站迫在眉睫[1]。异构多核处理器具有集成度高、处理能力强的优势[2],将异构多核处理器应用于BBU中,能够显著降低系统成本和功耗,有利于开发出新一代绿色节能网络基础设施[3]。

德州仪器公司率先推出了包含ARM Cortex-A15和DSP处理器的异构多核KeyStone II架构芯片[4],将其应用于BBU中,可实现控制与运算分离,ARM通过与上层协议的交互实现对DSP的任务调度和控制,完成物理层控制的功能,而DSP无须额外的开销来实现物理层控制,使得DSP能够处理更大的数据量。

在新型绿色基站中,采用异构多核的处理架构具有明显的优势,但同时,也给软件开发人员带来了新的挑战,如何在异构处理器架构下为软件层屏蔽掉底层硬件的差异是本文要研究和攻克的难题,也是软件无线电基站虚拟化的关键技术所在。因此,针对新型基带处理硬件平台开发出一套能够屏蔽底层硬件细节、通用性强的基带处理软件平台具有非常重大的意义,该平台使得软件开发人员无需关心底层硬件细节,提高了软件的可移植性,是基带处理板中承接硬件和软件的桥梁。

1 基带处理单元架构设计

1.1 TI异构多核的KeyStone II架构介绍

TI公司推出的KeyStone II架构芯片包含了多个ARM Cortex-A15和TMS320C66x DSP处理器,该架构最多可支持32个RISC和C66xx DSP内核[5]。除了异构多核架构本身具有极强处理能力外,该架构还包含了多个协处理器,例如FFTC、TCP3d、BCP以及多核导航器等,芯片内部通过2 Tbps的TeraNet光交换网络互联,使得片上处理单元之间能够高速无阻塞地传输数据;并提供SRIO、以太网、PCIe、HyperLink等高速接口,使得片外数据能够高速传输[5]。本文应用在基带处理板上的KeyStone II架构系列芯片是TCI6638K2K,其包含4个ARM Cortex-A15核和8个C66xx DSP核,处理能力极强,其突出的性能有利于开发出高性能的“绿色”新型基站。

1.2 基带处理硬件架构设计

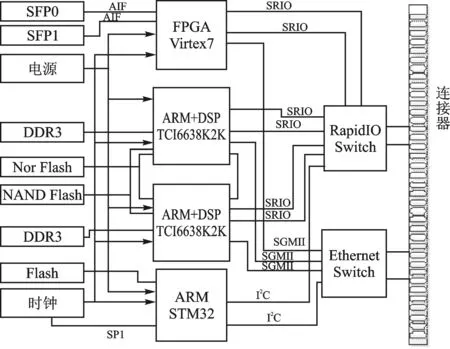

基带处理平台采用高性能异构多核ARM+DSP架构作为基带处理的核心,借助FPGA芯片强大的逻辑能力作为协处理单元,基站集群之间通过高速接口进行数据传输,如SerialRapidIO、以太网等相连,互相通信协作,ARM与DSP通过片内高达2 TB速率的光传输网络来进行交互。

基于ARM与DSP片内高速通信的优势,本文提出将物理层控制放在ARM上运行,实现对协议层原语的解析以及DSP实时任务的派发,ARM还完成片外数据传输和外围器件的控制功能,通过高速接口实现协议层数据的收发等,而DSP主要完成物理层运算的功能,这样DSP不再单独维护自身的任务队列,而且多个 DSP之间不再有任务交互接口[7],减轻了DSP的负载,而且片内的管道通信时延远小于片外的高速总线通信,速率却远高于高速总线。异构多核架构使得ARM和DSP专用处理器各尽其职,高效地利用了专用处理器的功能,与同构多核的DSP处理架构相比,具有更强的处理能力。

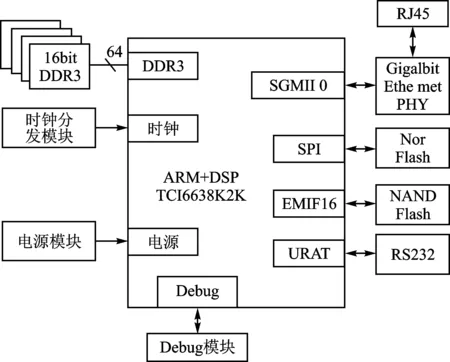

本项目中设计的基带处理板架构如图1所示,板卡之间的交互通过连接器连接到机箱或背板。

图1 基带处理板架构

在基带处理板架构中,ARM STM32对时钟分发模块进行管理和配置,为TCI6638K2K以及FPGA Virtex 7提供稳定的时钟输入,此外,STM32对SRIO Switch以及Ethernet Switch进行配置,保证Serial RapidIO(SRIO)和以太网能够正常通信。

异构多核的ARM+DSP是基带板的数据处理核心单元,TCI6638K2K分别通过SRIO和以太网高速接口与SRIO Switch和Ethernet Switch连接,通过交换芯片来实现TCI6638K2K以及FPGA之间的数据高速交互,此外,交换芯片又连接到连接器,通过机箱实现与其他基带板卡的数据传输。另外,FPGA由AIF2接口通过CPRI协议连接到中频板接收上行链路数据,再将CPRI协议转换为RapidIO协议或Ethernet协议,传输给TCI6638K2K进行数据处理。下行链路数据的传输则相反,TCI6638K2K将处理完成的数据通过RapidIO或Ethernet发送给FPGA,FPGA再将RapidIO协议或Ethernet协议转换为CPRI协议,通过光模块将数据传输到中频板,同时,FPGA还作为DSP的协处理器。在基带处理池中,可指定一块基带板作为主控板,通过FPGA的传输中转实现与中频信号的交互,再由主控板将数据通过SRIO或Ethernet高速接口传输到其他基带板中进行处理。

TCI6638K2K又通过高速以太网接口与协议处理单元相连,通过ARM来完成与上层信令和数据的交互,上层和物理层定义完整统一的API接口进行交互,上层向物理层发送请求,物理层向上层请求指示,上层将配置参数以及数据下发给物理层,物理层完成从逻辑信道到物理信道的映射,物理层将传输信道的错误反馈给高层,而DSP只需接收ARM传送的指令和数据,从而进行数据处理,无需增加额外的开销来完成物理层控制的功能。

2 异构多核架构的软件平台设计

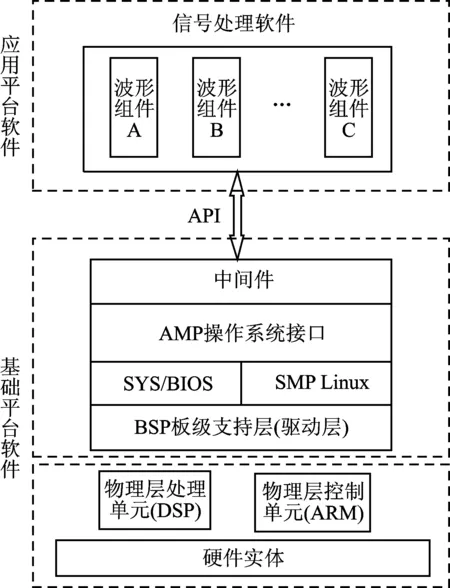

基于硬件虚拟化技术以及软件无线电虚拟化技术的思想,本文提出了一种在异构多核处理器架构中应用于基带信号处理的软件平台,其软件架构如图2所示。

图2 基带信号处理软件平台

驱动层提供了支持硬件抽象的板级支持包(BSP),封装了硬件操作细节的支撑库,该支撑库的抽象硬件接口为上层应用波形组件屏蔽了连接链路的异构,为操作系统提供统一的API,在操作系统层面上实现底层硬件的虚拟化。驱动层之上,DSP与ARM各自存在其操作系统SYS/BIOS与对称多核(SMP)Linux系统,操作系统接口为上层应用软件提供多任务调度,支持硬件设备驱动、内存、进程管理以及任务的实时调度。非对称多处理器系统(AMP)接口实现了ARM与DSP的交互,ARM可以通过虚拟I/O和远程处理器(remoteproc)架构实现对DSP的控制和管理。中间件是存在于AMP操作系统之上的软件层,是承接应用层软件与AMP操作系统接口的桥梁,在应用软件层面屏蔽了ARM与DSP系统的差异。

2.1 设计与移植

2.1.1 BootLoader的设计

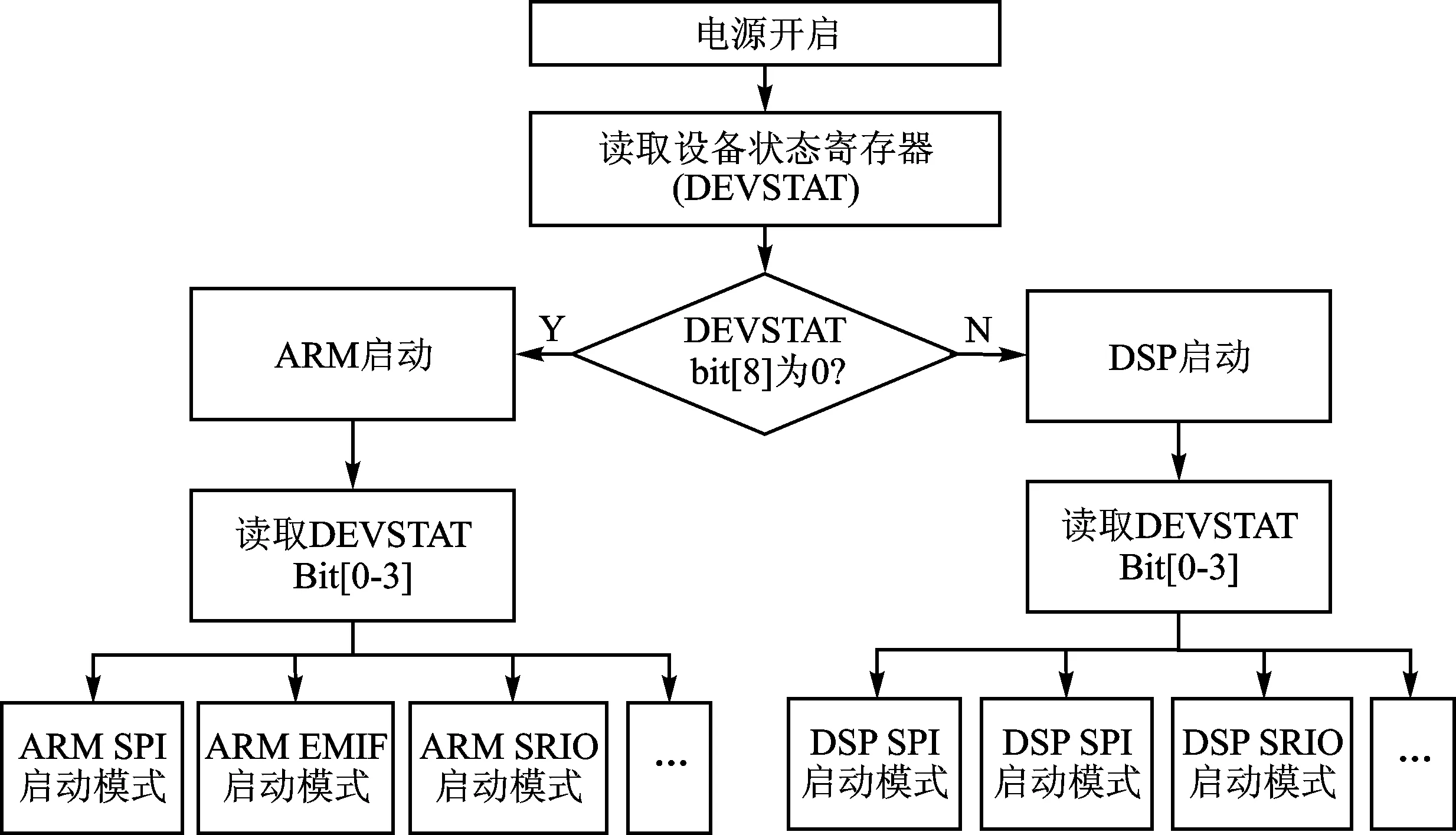

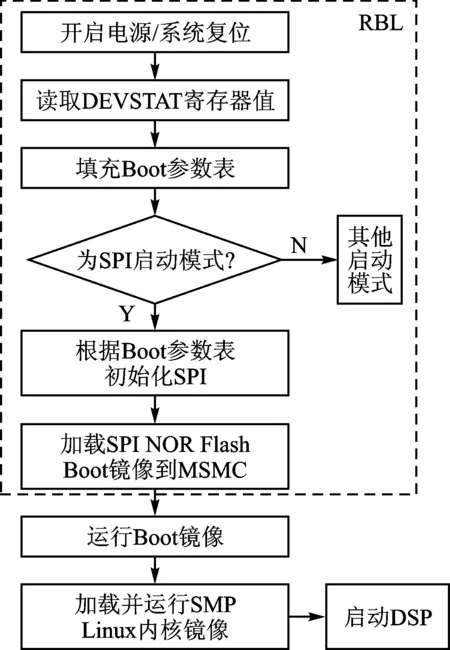

图3 RBL模式选择

BootLoader是SoC上电后运行的第一段代码,完成系统启动的准备工作,并最终实现引导AMP系统启动。为满足应用在不同场景下需要不同的启动模式,KeyStone II支持多种方式启动ARM和DSP。SoC内部固化集成了Boot Rom,电源开启后,固化在Boot Rom的程序将自动运行,这段程序被称为Rom BootLoader(RBL),RBL会扫描设备状态寄存器(DEVSTAT)对应的值,该寄存器的初值由SoC相应引脚的电平信号提供,通过DEVSTAT初值来决定SoC的启动模式,DEVSTAT各位对应的模式选择如图3所示。多核ARM与DSP在启动过程中表现为主从关系,启动模式主要可以分为两类:①DSP作为主控制处理器先行启动BIOS/SYS,再加载ARM核启动;②ARM作为主控制处理器先行启动Linux,再通过核间中断方式唤醒DSP。

考虑到软件固化的便利性,本文将BootLoader代码固化在SPI Flash中,而将占据内存较大的Linux内核及系统文件固化在NAND Flash中。ARM+DSP的系统架构如图4所示,TCI6638K2K通过SPI总线连接到NOR Flash,通过外部的FPGA将TCI6638K2K的Boot模式设置为SPI模式。

图4 ARM+DSP系统架构

ARM SPI Boot模式下启动过程如图5所示。

图5 ARM SPI Boot模式启动过程

当启动模式设置为ARM SPI Boot模式时,RBL根据DEVSTAT初值对SPI接口进行初始化,再通过SPI接口从NOR Flash的指定地址读取已经移植好的BootLoader,并加载到片上共享内存(MSMC)中,然后将控制权交由BootLoader程序。BootLoader完成初始化处理器以及必要的硬件、建立内存空间的映射等功能,并最终实现在ARM中加载启动SMP Linux系统,再通过Linux内核实现DSP的唤醒。

2.1.2 BootLoader的移植

U-boot中包含有读写Flash的命令,并且在U-boot启动后已经初始化了以太网接口,因此,固化U-boot和Linux程序只需要在U-boot启动后,设置好环境变量,执行固化命令就可以实现,U-boot的启动可以通过JTAG的方式加载到ARM核运行。

(1) 编译生成目标文件

在U-boot工程文件目录下运行Make命令,执行makefile配置文件和makefile文件,运行成功后将在工程文件夹下生成可烧写的u-boot.bin文件。

(2) 通过JTAG加载U-boot

用TI提供的CCS6.1软件通过仿真器连接到ARM核0,将生成的u-boot.bin文件拷贝到存放loadlin-evm-uboot.js脚本的文件夹下,并在该文件夹下打开控制台窗口,运行以下脚本:

loadJSFile"loadlin-evm-uboot.js"

u-boot.bin将会加载到MSMC SRAM中,在CCS中点击运行,则U-boot启动。

(3) 固化U-boot

U-boot已通过JTAG方式加载到MSMC中运行,在U-boot命令模式下,可通过以太网TFTP方式从主机中获取所需固化的u-boot.bin文件到MSMC中的指定地址0x0c30 0000:

tftp0x0c300000u-boot.bin

然后固化u-boot.bin到SPI NOR Flash对应的地址,将MSMC中地址为0x0c30 0000存放的u-boot.bin烧写到Flash的起始地址。

固化u-boot.bin,运行以下命令:

sf probe

sf erase 0x0000 0x100000

sf write 0x0c310000 0x10000

由于u-boot.bin文件的大小一般在500 KB,因此擦除Flash前512字节,并将MSMC中地址为0x0c31 0000存放的u-boot.bin烧写到Flash偏移量为0的地址。

2.2 AMP系统的构建与移植

2.2.1 AMP系统的构建

本文所设计的AMP系统采用SMP Linux与SYS/BIOS系统共存的方式,以Linux系统作为主控系统,通过remoteproc架构实现对DSP的管理和控制。由于ARM和DSP处理器构造上的差异,为更好地发挥ARM的控制功能以及DSP的运算功能,在同构多核的ARM上移植SMP Linux操作系统,使得用户不必关心SoC内部有多少个ARM核,ARM核间任务的调度以及内存的分配等将由Linux内核完成[7],而DSP对数据处理的实时性要求较高,因此DSP采用SYS/BIOS实时操作系统。同时,为了提高SMP操作系统的实时性,可对内核进行中断线程化、优化调度器等方法改进其实时性。

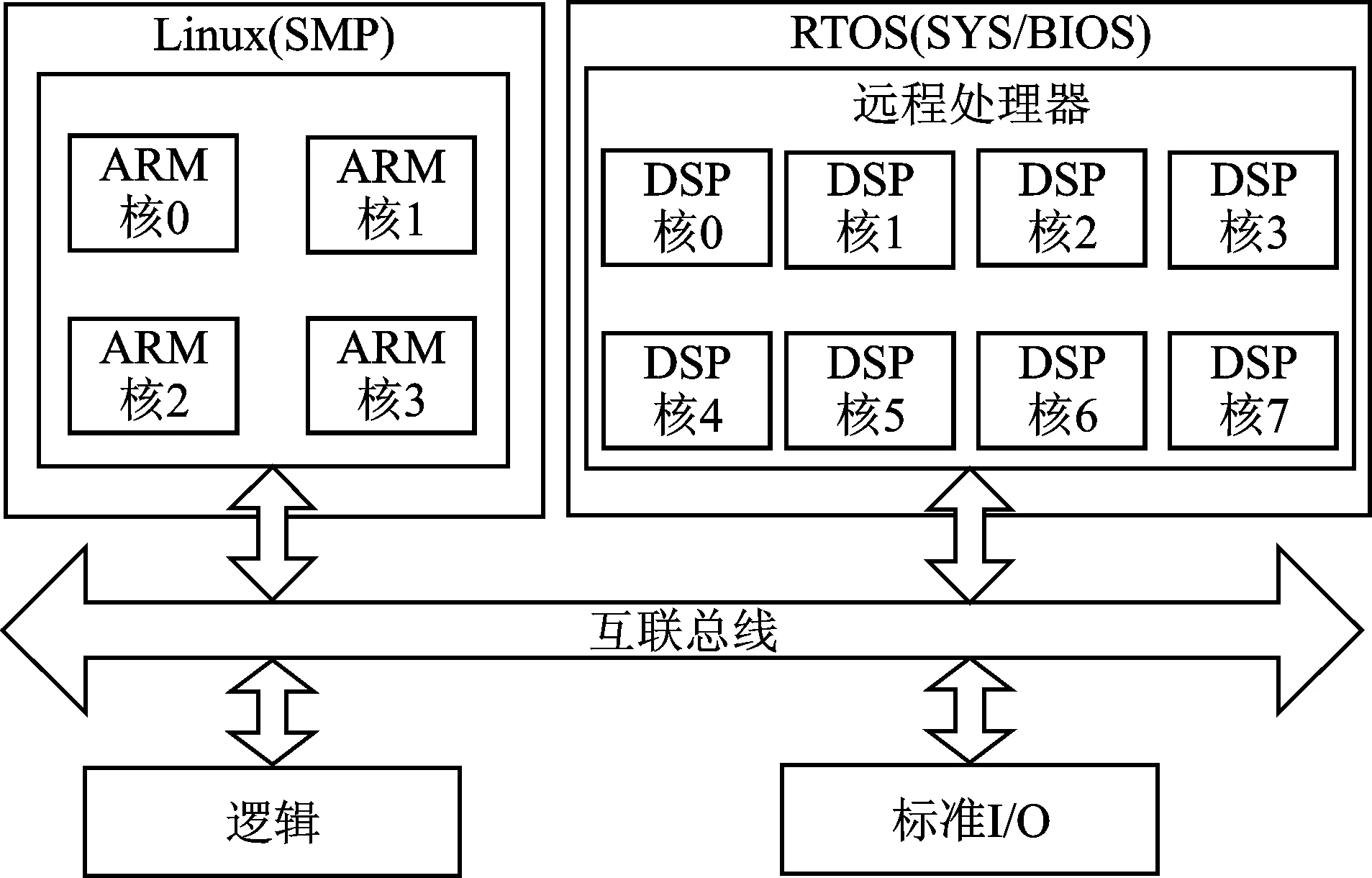

远程处理器(remoteproc)架构是Linux内核中用来启动或者停止各个异构的远程处理器[8],如图6所示,4个ARM核上运行SMP Linux系统,通过remoteproc架构将8个DSP核配置为远程处理器,该架构使得用户可以根据具体需求动态加载和运行DSP中的实时任务。

图6 远程处理器(remoteproc)架构

remoteproc架构中完成Linux核心与远程处理器的数据交互主要依靠虚拟I/O设备以及远程处理器消息(rpmsg)框架来实现,虚拟I/O设备定义了标准的I/O,而消息的传递通过rpmsg框架定义的互联总线来传输。

虚拟I/O设备定义了虚拟输入/输出设备(vdev),vdev可用于共享内存以及核间中断等方式通信,vdev定义并维护Linux传输队列,以便于Linux核心与RTOS数据交互,虚拟I/O设备以及队列初始化由内核完成,远程处理器只需注册vdev描述符,就可以操作队列。

远程处理器消息(rpmsg)框架是队列传输的消息软总线,处理器之间通过软总线创建可寻址端点,并且通过共享内存、核间中断以及多核导航等方式来进行信息交互。rpmsg框架能够控制信息的发送和接收,根据消息包中的目的地址将消息发送到相应的端点。

2.2.2 AMP系统的移植

由于Linux采用设备和驱动分离的架构模型,使得设备只描述设备信息,而驱动则是一个对于设备通用的软件,总线则负责匹配设备和驱动,驱动以标准途径拿到板级信息。设备和驱动分别由Device和Device Driver两个数据结构来描述,在过去,Linux内核中充满了描述板级信息的Device代码,这样使得Linux内核复杂又难以移植,因此,Linux发展到3.xx版本提出了设备树的概念,它是一种描述硬件配置的树形数据结构,其语法简单易读,Linux内核通过解析其语法来注册生成Device结构体,Device与Device Driver以一个兼容名称通过总线来匹配。因此,Linux 3.xx后驱动开发工程师的主要工作就是维护设备树。AMP系统的移植主要包括:

① 编译内核:在Linux源文件目录下执行配置命令和make命令,生成内核镜像文件uImage.bin。

② 构建根文件系统:根文件系统需包含系统启动时必要的目录,如/bin、/sbin、/etc、/dev、/lib 等。/bin 目录下存放的是系统所需的基本命令;/sbin存放系统管理程序和系统命令;/etc目录下包含系统的配置文件;/lib目录下存放驱动模块和共享库。根文件系统可以通过Busybox开发套件来生成。

③ 配置和编译设备树:根据板卡的外围硬件修改相应的设备树文件,在Linux内核代码中,设备树存放于arch/arm/boot/dts/目录下,以设备树源码文件(.dts)可读可编辑的文本形式存在,修改完成相应配置后,在Linux根目录下执行命令make k2hk.dtb,生成设备树文件k2hk.dtb。

④ 制作ubi文件:ubi文件对应的是UBI层上的管理系统文件,它建立于MTD层上,用逻辑卷(logic volume)来替代MTD分区,能动态创建、删除和改变大小。ubi文件的制作包括以下步骤:

(a) 新建并编辑一个ubinize.cfg文件(ubinize.cfg是一个配置文件):

mode=ubi

image=ubifs.img

vol_id=0

vol_size=113MiB

vol_type=dynamic

vol_name=boot

vol_flags=autoresize

mode配置的是文件格式,image配置的是ubifs镜像源文件,vol_id是逻辑卷在UBI中的ID号,vol_size是逻辑卷的大小。

(b) 应用mkfs.ubifs工具将设备树和内核文件生成ubifs文件,添加好环境变量后执行如下命令,将会生成k2hk.ubifs文件。

mkfs.ubifs-r boot-F-o k2hk.ubifs-m 2048-e 126976-c 41

再将ubinize.cfg与k2hk.ubifs放到同一文件夹下,执行如下命令将会生成最终可烧写到NAND Flash中的k2hk.ubi文件。

ubinize-ok2hk.ubi-m 2048-p 128KiB-s 2048-O 2048 ubinize.cfg

⑤ 烧写ubi文件到NAND Flash。

在移植完成U-boot后,可以利用U-boot模式下TFTP服务器通过以太网将k2hk.ubi文件从PC机中传输到板上的DDR内存中,再执行擦除以及固化命令,将内存中的k2hk.ubi固化到NAND Flash中。

2.3 中间件概述

中间件为应用层软件定义统一的标准接口,屏蔽了底层异构多核的差异,中间件能够识别物理层算法与物理层控制程序,并将任务派发给ARM或DSP,完成相应的处理,各组件不再与具体硬件模块绑定,使得应用层软件具有很高的可移植性,同时,中间件又为SYS/BIOS与SMP 操作系统的跨平台交互提供统一标准接口,例如TI公司为异构多核平台提供了一套核间通信(IPC)套件,实现DSP与ARM通过标准API来进行交互。

结 语

[1] Guangjie L,Senjie Z,Xuebin Y,et al.Architecture of GPP based,scalable,large-scale C-RAN BBU pool[C]//2012 IEEE Globecom Workshops,2012:267-272.

[2] 陈芳园,张冬松,王志英.异构多核处理器体系结构设计研究[J].计算机工程与科学,2011(12).

[3] Texas Instruments.Embracing LTE-A with KeyStoneSoCs,2012.

[4] Texas Instruments.德州仪器KeyStone II架构助力多内核技术发展[J].电子技术应用,2012,38(4):30.

[5] Texas Instruments.Multicore DSP+ ARM KeyStone II System-on-Chip (SoC),2013.

[6] 田飞,杨虹.基带芯片物理层控制方案的设计[J].现代电子技术,2014(3).

[7] Stotzer E,Jayaraj A,Ali M,et al.Openmp on the low-power TI KeyStone II arm/dsp system-on-chip[C]//International Workshop on OpenMP.Springer Berlin Heidelberg,2013:114-127.

[8] Baum F,Raghuraman A.Making Full use of Emerging ARM-based Heterogeneous Multicore SoCs[C]//8th European Congress on Embedded Real Time Software and Systems,2016.

曾定立(硕士研究生),主要研究方向为移动通信、嵌入式操作系统;丁国杰(硕士研究生),主要研究方向为移动通信、电子电路设计。

Heterogeneous Multicore Architecture Software and Hardware Platform for Baseband Processing

Zeng Dingli1,Ding Guojie2

(1.Wireless Broadband Interconnection Laboratory,Chongqing University of Posts and Telecommunications,Chongqing 400065,China;2.Wireless Communication Technology Research Center,Institute of Computing Technology,Chinese Academy of Science)

By studying the characteristics of baseband processing unit (BBU) in centralized processing architecture of modern communication system,a view of separating the physical algorithm and control and applying heterogeneous multi-core processor to BBU is proposed.In the heterogeneous multi-core of ARM+DSP,ARM completes the function of physical layer control,DSP completes the function of physical layer algorithm.It improves the BBU baseband processing capability.The complete BBU hardware architecture is given,which realizes the virtualization of the underlying hardware from the software level.The introduction of middleware shields the differences between ARM and DSP operating systems.It also provides the building and migration method of asymmetric system,including the design and transplantation of heterogeneous multi-core BootLoader and AMP system.

baseband processing unit;heterogeneous multicore;ARM;DSP;middleware;BootLoader;AMP system

TN929.5

A

�士然

2016-11-17)