一种采用数字修调技术的低温漂带隙基准设计

2017-03-23曹璐,刘宏,田彤

曹 璐,刘 宏,田 彤

(1.中科院 上海微系统与信息技术研究所,上海 200050;2.上海科技大学 信息学院,上海 200050)

一种采用数字修调技术的低温漂带隙基准设计

曹 璐1,2,刘 宏1,田 彤1

(1.中科院 上海微系统与信息技术研究所,上海 200050;2.上海科技大学 信息学院,上海 200050)

基于tsmc0.25μm CMOS工艺,设计了一个采用数字修调技术的低温漂高PSRR带隙基准源。针对带隙基准结构中不可避免的由于工艺偏差而导致输出基准电压温度特性较差的问题,通过引入额外的PTAT电流来改变流过PNP的电流,进而补偿由于工艺角变化引起的带隙基准温度系数的改变,实现低温漂基准电压源。仿真结果表明,5 V电源电压下,在-50~+150℃,基准电压温度系数为3ppm/℃,与无数字修调的带隙基准相比,温度系数减小了5 ppm/℃。低频时电源抑制比为-90 dB,整体功耗电流约为60 μA。

微电子学;带隙基准;数字修调;低温漂;温度系数

基准源广泛应用于模拟和混合集成电路设计中,例如数据转换器、PWM控制器、振荡器、运放和PLL等。随着电路越来越复杂、性能要求越来越高,高精度基准源已经成为很多模块的关键部分。传统的带隙基准由具有负温度系数的PN结二极管的正向电压VBE和具有正温度系数的热电压VT实现,工艺偏差、温度变化等因素都会影响带隙基准电压的精确性,加上对低压、低功耗、低失调的各种实际应用需求,在此基础上出现了很多改进电路[1-4]。

1 数字修调原理

文中针对工艺偏差的影响,避开了复杂的高阶补偿技术[3,5-8],也避开了传统的采用电阻trimming的较为复杂的电路基准源技术[9-10],设计了一种采用数字修调技术的低温漂带隙基准,结构框图如图1所示。

图1 改进的带隙基准结构框图

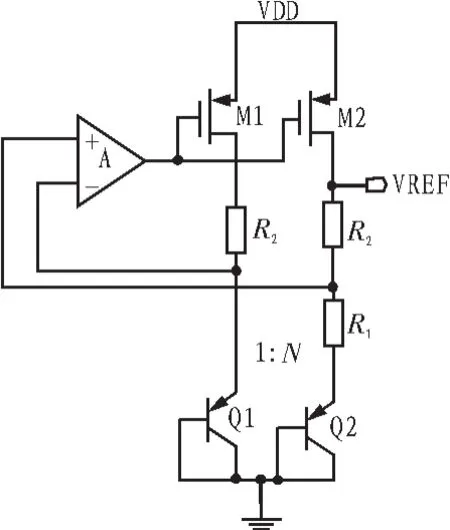

传统带隙基准如图2的电路所示,由两个发射极面积为1:N的双极管、一个运放和若干电阻构成。在标准CMOS工艺中,双极管采用寄生的纵向PNP管。

图2 传统带隙基准电路

根据电流电压公式[12-15],近似有:

当IC1=IC2=IC,IS2=NIS1=NIS时,联立有流过R1的电流

当R1存在偏差ε时,即R1′=R1(1+ε),有

不论IC1、IC2怎么变化,只要式子IC1=IC2成立,则式(5)成立。对于上述结构,输出基准电压为

由于电阻比例随工艺变化很小,所以可以认为正温度项系数不随工艺变化。根据(2)式,考虑当集电极电流变为IC+ΔIC、反向饱和电流由于工艺偏差变为IS+ΔIS时,有

引入修调系数k后,集电极电流变为

其中ΔIC=kIR′。将(5)、(8)代入(7)式有

2 数字修调带隙电路设计

2.1 数字修调设计

图3 主体电路图

2.2 运放电路设计

图4是带隙基准电路中采用的高增益运放[11]。左边是运放的偏置结构,由M1~M6和电阻R构成。中间是运放的放大级,采用折叠式共源共栅结构,由M7~M17组成,目的是提高运放的增益。后接一个补偿电容,由于放大级输出端阻抗足够大,所以无须米勒补偿形式,确定了主极点,保证使用该运放之后的带隙基准的相位裕度。最后一级是运放的输出级,由PMOS管M18和M19组成,M18采用的是PMOS管射随器,目的是不引入额外的极点,并将输出电压提高了一个阈值电压;M19采用二极管形式连接,使运放整个输出基本跟随电源电压变化,提高带隙基准电路的PSRR。

图4 运放电路设计

3 仿真结果与分析

仿真结果如图5所示。从(b)和(c)、(d)和(e)的对比中可以直观地发现修调后比修调前基准电压的温度特性明显要好。tt下修调前输出电压1.223 V,TC为8.2 ppm/℃;修调后输出1.226 V,TC为3 ppm/℃。ff下修调前输出电压1.229 V,TC为6.5 ppm/℃;修调后输出1.232 V,TC为2.4 ppm/℃。ss下输出1.22 V,TC为3.2 ppm/℃。如此低的温度系数,得益于电阻的选型为高精度低温度系数的P-poly电阻,同时也依赖于改进的数字校准电路的采用。

运放的PSRR仿真如图6所示。低频时PSRR达到-102 dB,在2.6 MHz时为最差-32 dB。

图5 电压基准温度系数仿真结果

图6 运放的PSRR仿真

4 结 论

电路采用tsmc0.25 μm CMOS工艺,使用Spectre仿真工具,在典型工艺模型下,电路工作电压为5 V,27℃时输出1.226 V,工作电流小于60 μA。5 V电源电压下,在37℃左右取得零温度系数。在-50~+150℃,基准电压温度系数可低至3 ppm/℃,与无数字修调的带隙基准相比,温度系数减小了3~5ppm/℃。室温下,低频时电源抑制比为-90 dB,电路静态电流约为60 μA。

[1]Mok P K T,Leung K N.Design considerations of recent advanced low-voltage low-temperaturecoefficient CMOS bandgap voltage reference[C]// Proceeding-s of the Custom Integrated Circuits Conference,2004:635.

[2]Tom K,Alvandpour A.Curvature compensated CMOS bandgap with sub 1V supply[C]//null.IEEE,2006:93-96.

[3]Andreou C M,Koudounas S,Georgiou J.A novel wide-temperature-range, 3.9 ppm/C CMOS bandgap reference circuit[J].Solid-State Circuits,IEEE Journal of,2012,47(2):574-581.

[4]Koushaeian L,Skafidas S.A 65nm CMOS lowpower,low-voltage bandgap reference with using self-biased composite cascodeopamp [C]//Low-Power Electronics and Design(ISLPED),2010 ACM/IEEE International Symposium on.IEEE,2010:95-98.

[5]张红南,曾健平,田涛.分段线性补偿型CMOS带隙基准电压源设计[J].计测技术,2006,26(1):35-38.

[6]王红义,来新泉,李玉山,等.采用二次曲线校正的CMOS带隙基准[J].电子器件,2007,30(4):1155-1158.

[7]杨鹏,吴志明,吕坚,等.一种二阶补偿的低压CMOS带隙基准电压源[J].微电子学,2007,37(6):891-894.

[8]Ge G,Zhang C,Hoogzaad G,et al.A single-trim CMOS bandgap reference with a inaccuracy of 0.15%from 40 C to 125 C[J].Solid-State Circuits,IEEE Journal of,2011,46(11):2693-2701.

[9]朱波.带数字自校正的 CMOS带隙基准电压源设计[D].成都:电子科技大学,2013.

[10]李永红.电源芯片中CMOS带隙基准源与微调的设计与实现[D].成都:电子科技大学,2005.

[11]Li W,Yao R,Guo L.A low power CMOS bandgap voltage reference with enhanced power supply rejection [C]//ASIC,2009.ASICON'09.IEEE 8th International Conference on.IEEE,2009:300-304.

[12]Razavi B,罗扎.Design of analog CMOS integrated circuits[M].北京:清华大学出版社有限公司,2001.

[13]Palumbo G.Voltage references:from diodes to precision high-orderbandgap circuits [Book Review][J].Circuits and Devices Magazine,IEEE,2002,18(5):45-45.

[14]Tsividis Y P.Accurate analysis of temperature effects in i/sub c/v/sub be/characteristics with application to bandgap reference sources[J].Solid-State Circuits,IEEEJournalof,1980,15(6):1076-1084.

[15]Meijer G,Schmale P C,Van Zalinge K.A new curvature-corrected bandgap reference[J].Solid-StateCircuits,IEEEJournalof,1982,17(6):1139-1143.

Design of a bandgap reference with low temperature-drift used digital trimming technology

CAO Lu1,2,LIU Hong1,TIAN Tong1

(1.Shanghai Institute of Microsystem and Technology,Chinese Academy of Sciences,Shanghai 200050,China;2.School of Information Science and Technology,Shanghai Tech University,Shanghai 200050,China)

In this paper,a bandgap reference with low temperature-drift and high PSRR used digital trimming technology is designed based on tsmc0.25 μm CMOS process.Aiming at the problem that it is inevitable to cause bad temperature activity because of process deviation in the bandgap architecture,an extra PTAT current is introduced into the PNP to compensate for the deviation of TC of VBEin different corners,thus achieving bandgap voltage reference with good TC behavior.Simulation results show that the bandgap has a temperature coefficient of 3ppm/℃from-50~150℃in 5 V supply,PSRR is-90 dB in low frequency and quiescent current is 60 μA.

microelectronics;bandgap reference;digital trimming;low temperature-drift;temperature coefficient

TN402

:A

:1674-6236(2017)05-0150-04

2016-03-07稿件编号:201603080

曹 璐(1991—),女,浙江金华人,硕士研究生。研究方向:模拟/射频集成电路及系统设计。