基于DM8168的小型机载视频记录仪设计

2017-03-21石园丁徐鑫涛吴寅华

石园丁,徐鑫涛,吴寅华,朱 威,3

(1.中国电子科技集团公司第五十二研究所,杭州 310012;2.浙江工业大学 信息工程学院,杭州 310023;3.浙江省嵌入式系统联合重点实验室,杭州 310023)

基于DM8168的小型机载视频记录仪设计

石园丁1,徐鑫涛2,吴寅华1,朱 威2,3

(1.中国电子科技集团公司第五十二研究所,杭州 310012;2.浙江工业大学 信息工程学院,杭州 310023;3.浙江省嵌入式系统联合重点实验室,杭州 310023)

针对飞行器搭载相机视频存储和传输的需求,设计了一种基于异构多核处理器DM8168的小型机载视频记录仪;首先,基于DM8168和FPGA处理器设计小型化低功耗的硬件系统;接着,基于McFW软件架构设计视频采集编码的数据流,充分发挥DM8168多核体系结构的优势,实现两路1080p60视频的采集,并且对每路视频分别进行主次码流的H.264编码;最后,采用GPMC总线,将视频码流传输到FPGA处理器,以实现本地视频存储和远程视频传输;该记录仪体积小、记录时间长、视频采集编码延时小、功耗低,能够很好地满足飞行器多路视频记录的需求。

DM8168;飞行器;视频记录仪;H.264;GPMC总线

0 引言

机载视频数据由于能够直观反映飞行器的飞行状况,在其日常飞行中发挥着十分重要的作用。机载视频记录仪在飞行过程中既可以实时记录飞行器外的航拍场景,又可以实时记录飞行器内部座舱各仪表的画面等信息,在无人机航拍、飞行训练评估、新型飞机的研制和试飞等方面具有十分重要的意义[1-2]。因此,机载视频记录仪已成为飞行试验中重要的仪器设备。

机载视频记录仪的记录方式已由早期的磁带式记录发展到了现在的数字式记录,极大提高了数据的存储性能和可靠性。但受飞行器空间、载重和供电等因素的限制,在满足系统需求的情况下,目前的机载视频记录仪的软硬件仍然需要进行高度集成化的设计,从而满足其在性能、体积、功耗以及安全等方面的需求[3]。本文综合考虑这些要素,所设计的小型机载视频记录仪具有较好的实际应用价值。

1 系统需求

根据军用和民用飞行器视频存储和传输的需求,本文小型机载视频记录仪的基本功能需求如下:可支持采集双路视频图像输入,一路为可见光相机输入,另一路由红外相机输入,视频分辨率和帧率最高需达到1080p60;对采集到的每路视频都需编码得到主次码流,主码流用于本地高清晰视频存储,存储时间长度需要达到5小时以上,大于目前绝大部分飞行器的飞行时间,次码流用于向地面站实时传送视频图像。

虽然与传统的黑匣子(飞行数据记录仪)记录的数据内容不同,但是其记录的视频同样是在发生重大事件时的重要数据,也需要在相对恶劣的环境下,正常稳定地工作。因此,机载视频记录仪在软硬件设计方面特别需要满足以下要求[4]:

1) 高可靠:硬件设计需要拥有较好的保护措施,减少振动、加速度、冲击的物理伤害以及电磁干扰的影响[2],具备抗火、耐压、耐温、耐冲击振动等特性;软件设计需要综合考虑软件系统架构和实现细节,保证软件能长期稳定运行。

2) 小型化低功耗:由于飞行器搭载重量和供电的限制,硬件设计需要选择系统集成度高、功耗低的芯片,特别是在视频编码芯片方面,尽量在一颗芯片上完成所有视频编码功能,减小电路板的体积;软件设计需要优化数据流,减少访问外部存储器的次数,并屏蔽不用的模块,以降低系统功耗。

3) 可扩展:硬件设计需要核心硬件芯片的处理能力有余量,软件设计需要有良好的代码结构,以满足后续视频实时分析等功能扩展的要求。

2 总体设计

本文机载视频记录仪的核心设计难点是在小型化低功耗的要求下对输入的两路1080p60视频进行高效压缩。为了保证视频压缩的效率,本文选择使用目前主流的视频编码标准H.264,它具有压缩比高、容错能力强和网络适应性好的特点。为了在保证记录仪性能的基础上尽可能让设备小型化和低功耗,本文在软硬件方案上进行了综合考虑,采用TI 公司(Texas Instruments)达芬奇系列的视频SoC处理器DM8168作为主芯片[5-6],负责视频编码等功能。该芯片包含一个主频高达1.2 GHz的ARM Cortex-A8内核、一个主频高达1 GHz的C674x浮/定点DSP内核、两个用于媒体控制Cortex-M3内核、三个高清视频图像协处理器(HDVICP2)、一个高清视频处理子系统(HDVPSS)等,还具有GPMC、EMAC等高性能外设接口。此外,本文还采用FPGA处理器来负责与外设进行数据交互,完成数字视频转换和视频码流存储等功能。这样的设计相比传统的视频记录设备在性能、功耗上有显著的提升,同时也简化了外围硬件电路。

本文机载视频记录仪的总体设计框架如图1所示。首先通过两个专业相机采集双路视频,FPGA将视频转换成YUV格式后,送入DM8168视频处理芯片。DM8168利用其强大的H.264算法硬件编码能力进行多路视频编码,将每路视频都编码出主次码流,然后通过GPMC接口将码流传回给FPGA。FPGA接收码流后将主码流保存到本地硬盘,并把次码流送到无线接收发送模块,通过该模块将次码流数据发送给射频无线通信设备,实现机载设备和地面站的远程无线视频通信。

图1 系统总体设计框架

3 硬件设计

本文视频记录仪内部的硬件原理如图2所示,由视频记录板和电源板构成,其中视频记录板由输入单元、处理单元和输出单元组成。视频记录仪外部输入的视频数据接口形式为LVDS接口,不能直接接入DM8168,因此需要对输入数据进行格式转换。考虑到记录仪小型化的要求,数据记录存储载体采用大容量、高密度MLC型 NandFlash。为了实现较高的数据记录速度,采用FPGA作为NandFlash的读写控制器。视频记录仪需要接收用户发送的记录、停止、转储、参数设置等指令,然后根据指令进行相应的动作,因此采用一片C8051单片机实现系统管理、用户接口等功能。

图2

3.1 输入单元

两路视频数据输入接口均采用可见光相机和红外相机常用的LVDS电平接口,输入格式满足Camera Link Base配置模式的要求。NS公司(National Semiconductor)的Channel Link芯片DS90CR286具有4路LVDS Channel,输出28bits的CMOS/TTL的并行数据,最大外部输入时钟为66MHz,数据吞吐量可高达1.848Gbit/s,完全满足输入视频数据带宽和Camera Link接口标准的要求。LVDS电平为电流驱动型电平,在LVDS数据接收端,差分信号的正、负之间必须跨接100Ω端接电阻。PCB布线时LVDS差分对需严格进行100Ω阻抗控制,减小因阻抗不匹配产生的信号完整性问题。每一对差分信号均进行等长约束,保证数据采集正确。此外,对DS90CR286芯片的电源管脚进行正确的滤波设计,以保证电源噪声Vp-p在100mV以内。

3.2 处理单元

处理单元主要由FPGA模块和DM8168模块构成。FPGA接收输入单元产生的两路28bit并行数据,按照DM8168模块视频输入接口要求,将输入的28bit数据进行格式转换,转变成高清视频16bit Y/Cb/Cr格式输出给DM8168模块。FPGA同时接收DM8168模块输出的压缩码流,一方面在单片机的控制下按照固定的包格式将压缩码流写入NandFlash中,另一方面通过同步422电路实时下传压缩码流。DM8168模块同时对输入的2路视频数据进行H.264压缩编码,压缩后的码流再通过GPMC接口传回FPGA模块。

3.3 输出单元

输出单元包括同步422转发电路和记录数据转储接口电路。FPGA采用2线同步串行的方式实时输出压缩码流,即一个CMOS电平的时钟线和一个CMOS电平的数据线。然后将时钟线和数据线的CMOS电平采用RS422芯片转换为RS422差分电平输出,这种输出方式通常称为同步422输出方式。转储电路就是提供将记录仪中存储的数据转移到地面设备的接口,便于后续对记录数据进行分析、回放等。本设计中采用LVDS发送芯片DS90CR285,可快速、可靠完成数据转储工作。

3.4 存储介质容量选择

系统设计要求连续视频记录时间不小于5小时。实际测试结果表明,当H.264视频压缩码流输出码率≥8 Mbps时,解码播放视频可获得较好画质。因此本设计中视频压缩输出码率设置为8 Mbps。同时记录2路视频压缩码流5小时所需的容量为:

8Mbps×2×5×60×60=36000 MB=36 GB

因此,选择2片容量为32 GB的NandFlash可满足记录时间要求。

3.5 小体积、低功耗设计

电路设计时,电阻和电容尽量采用0402封装的表贴器件,集成芯片选择BGA型小尺寸封装,采用多层PCB板设计,器件贴装密度较高。根据系统需求,选择满足要求的低功耗FPGA,DM8168采用核心电压动态调整技术节省功耗,对接口LVDS芯片进行节电模式控制,选择高效率电源转换芯片等。通过以上措施,保证了视频记录仪小体积、低功耗。

3.6 可靠性、隔振抗冲设计

可靠性设计主要采取以下几点措施:

1)按模块化思路、以及采用成熟的工艺和技术进行设计;

2)器件、零部件基本采用军品级、工业级产品;

3)对电路进行容差设计,采用数字电路作为电路的主体,减少使用模拟电路及锁相环,以避免温度变化对电路参数的影响;

4)对采购的元器件和零部件进行严格检验,并合理降额使用;

5)加强电磁兼容设计,避免设备因为受到外界干扰而无法工作的情况,电磁兼容重点解决机箱屏蔽问题,并对出入电源进行滤波处理;

6)对发热量较大的电源模块加强散热处理,大功率器件直接贴金属壁,避免热量的堆积而导致寿命缩短。

隔振抗冲设计主要采取以下几点措施:

1)机箱由高强度铝合金整体加工成型,再拼接一块上盖板而成;

2)视频记录板通过螺钉直接固定在机箱结构上,使之成为一个整体,避免形成悬臂梁结构,提高抗振性能;

3)机箱内电源板与视频记录板通过垫柱连接,确保两板间的接插件可靠连接;

4)与外部设备连接的插座直接与机箱壁固定,确保与外部设备可靠连接。

4 软件设计

4.1 软件开发环境

本文的软件基础开发环境采用TI的DVRRDK开发套件,该套件是TI针对达芬奇系列多核异构处理器设计的一套多通道视频应用框架,内部集成了很多用于视频应用开发的组件,并通过McFW软件框架[5]对组件进行调度。该软件包还提供了配套的U-boot、内核、文件系统以及交叉编译工具,可以较快地实现软件平台搭建。

4.2 软件处理流程

本软件处理流程如图3所示,主要用到了DM8168中的三个处理核。核心功能有采集和编码两部分,分别通过VPSS M3核和Video M3核管理[7]。VPSS M3核调度的HDVPSS子系统负责采集功能,主要利用了其中的VIP模块,采集双路YUV422P格式视频。Video M3核调度的HDVICP2子系统共三个加速器,负责H.264编码功能,输出主次码流。ARM子系统负责统一调度这两个M3核外,还会将码流通过GPMC总线送到FPGA。FPGA将主码流保存到本地存储设备,并通过无线图像传输模块将次码流发送到远程地面站。在H.264编码方面,主码流为了提高视频质量,采用帧级编码方式,设置较高码率,整体压缩比小,图像质量高;次码流为了提高无线图传容错性,采用片级编码,降低视频分辨率,设置较低码率,整体压缩比高,无线视频传输带宽低。

图3 软件处理流程

4.3 视频采集编码数据流设计

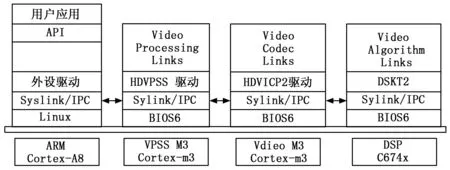

DM8168的软件开发是在McFW软件框架之上,其层次如图4所示。该框架将DM8168上的设备功能封装成不同的Links,不同Links之间彼此独立且能相互通信。核间通信利用Syslink/IPC核间通信机制实现,其通过共享内存交换数据的方式来保证效率[8]。DM8168的Cortex-A8核可以通过API统一管理所有Links。

图4 McFW软件框架层次图

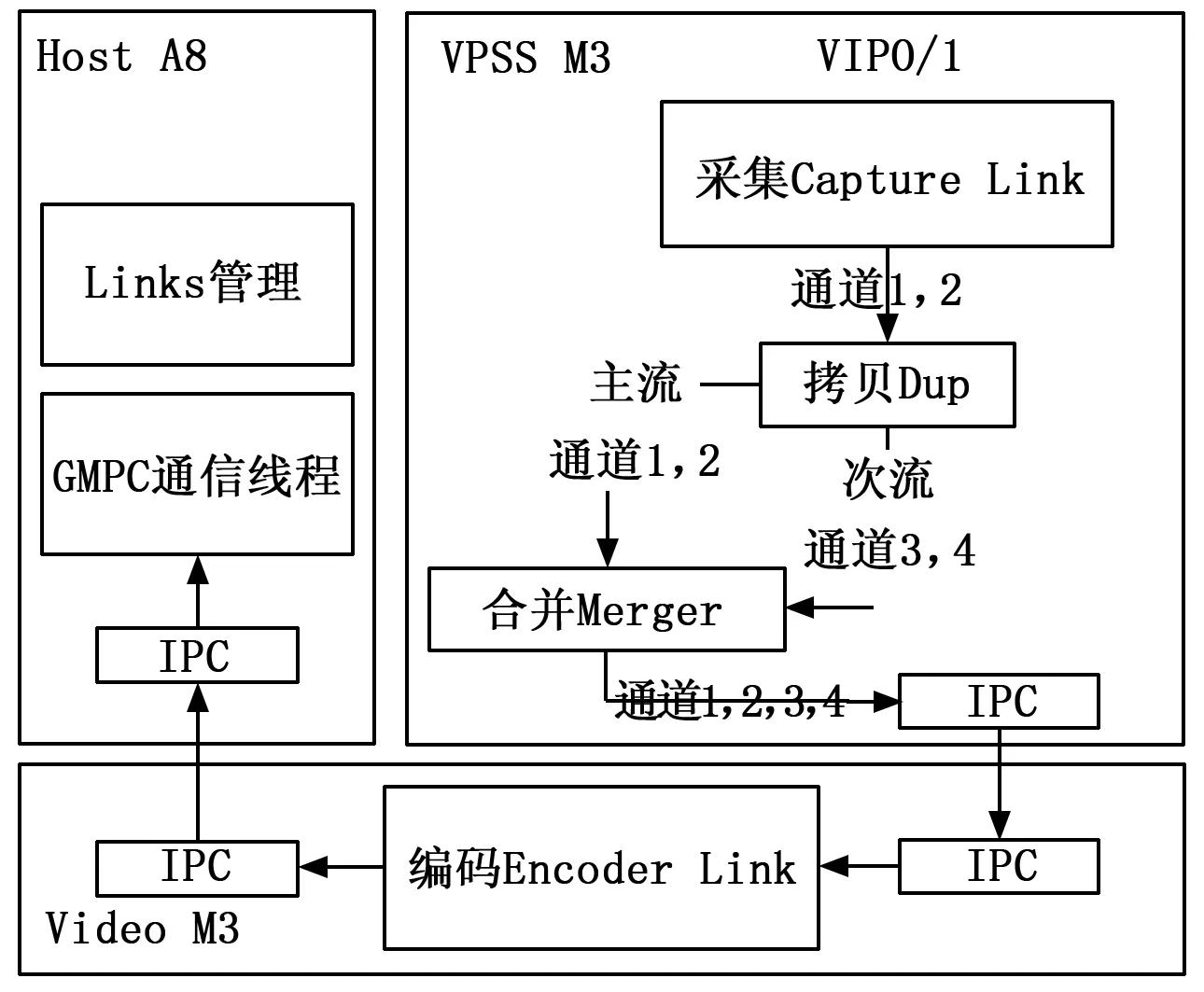

本文在McFW框架下,设计了一条数据链路来实现相关功能,数据链路图如图5所示。Capture Link通过HDVPSS驱动获取视频数据并加上FVID2格式的帧头。接着通过Dup Link形成主次视频两路队列,并利用Merger Link将该两路队列混合成一路有4个通道的视频流。然后Encoder Link进行H.264编码,输出主次码流。最后利用Cortex-A8的GPMC驱动,将码流送到FPGA。在这条数据链路中,通过IPC Link实现数据流在核间的通信。

图5 视频采集编码数据链路图

4.4 GPMC数据传输设计

FPGA是并行处理系统,能同时实现通信模块交互和本地存储任务,所以本文通过相比文献[9]中HPI接口更为合理的GPMC接口将数据传输到FPGA。为便于检索和查询,A8核通过GPMC接口在将码流发送到FPGA前,都会在码流每帧帧头前加入当前的拍摄时间、GPS地理坐标等信息。同时FPGA存储数据时,每隔一段时间(大约半小时)就会将数据保存路径切换到以时间为文件名的新文件里[10-11]。

GPMC,即通用存储控制器(General-Purpose Memory Controller),通过L3总线接口连接各种外部设备。ARM核上的Linux系统可以通过insmod命令加载GPMC驱动模块,并通过rmod命令进行卸载。该模块一旦加载,就可以通过文件函数进行读、写等操作。Linux中的GPMC驱动源代码在内核路径/arch/arm/mach-omap2/gpmc.c中。该文件已经把与GPMC相关的7个特殊寄存器的操作封装成了函数,我们只需要通过gpmc_cs_configure()调用相关函数就可以。FPGA在GPMC中属于NOR Flash设备,须将其配置为此设备,并设为异步模式,数据的搬运利用EDMA实现。在相关管脚配置方面,数据线带宽为16位,而地址线实际使用了低12位,范围0~0x1000,片选信号GPMC_CS1、CPMC_CS2都连接到FPGA。

5 实验结果与分析

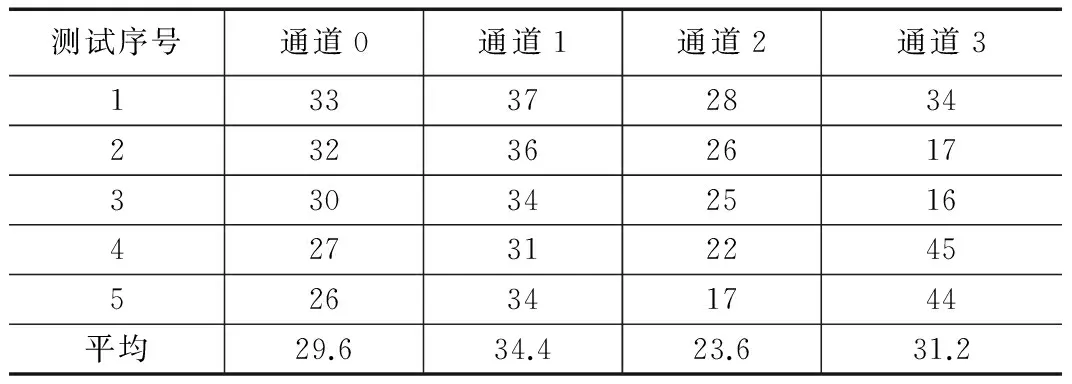

所设计的小型视频记录仪外形尺寸为(长×宽×高):150 mm×88 mm×47 mm,根据所选NandFlash的存储容量,两路主码流的视频记录时间大于5小时。本节首先测试视频记录仪在典型应用配置(即两路采集四路编码)下的采集编码延时。DM8168的两个视频输入口VIP0和VIP1同时采集视频,其中VIP0采集1080p (1920×1080) 30fps的视频,VIP1采集XVGA (1024×768) 30fps的视频,每路采集视频再分主次码流编码,总共4路编码通道,各通道的H.264编码配置如表1所示。在延时测试过程中,分别记录获得采集帧的时刻t1,以及该帧在发送码流之前的时刻t2,这两个时刻之差就是采集编码部分在整个软件系统中的延时,共测试5次,结果如表2所示。

表1 各通道配置

表2 采集编码延时 ms

从表1和表2中可以看出,虽然4个通道的采集编码延时存在波动,但延时都非常小,平均都在35 ms以下,完全满足视频记录仪低延时的设计需求。从表中还可以看出,由于具有相同的采集帧率,通道0与通道2的平均延时相近,通道1与通道3的平均延时相近;通道0因为分辨率和码率更大,系统处理的时间更多,其平均延时大于通道2;通道1因为分辨率和码率更高,并且编码档次更复杂,其平均延时也稍大于通道3。此外,通道0和通道2由于具有更快的帧率,系统调度效率更高,延时分别小于通道1和通道3。

接着我们在两路采集四路编码的典型配置下测试整机系统功耗。图5为系统测试平台连接示意图,测试环境为室内常温。调节直流稳压电源输出DC28V,视频信号源同时输出1080p和XVGA两种彩色视频。视频记录仪上电工作,当直流稳压电源输出电流不再增加时,表明视频记录仪处于稳定工作状态,此时功耗达到最大值,从直流稳压电源的输出显示面板上可以读取此时的输出电流为0.47 A。因此视频记录仪功耗为: 28 V×0.47 A=13.16 W。

图5 功耗测试连接示意图

6 结束语

机载视频记录仪在民用、军用飞行器上应用广泛,小型化和低功耗是其设计的一个难点。本文设计了一种基于DM8168的小型机载视频记录仪,该记录仪采用DM8168和FPGA设计硬件系统,采用McFW框架设计视频采集编码系统,充分发挥了DM8168多核并行处理的优势,采用GPMC总线设计从DM8168到FPGA的传输系统,实现码流数据的高速传输。所设计的小型视频记录仪体积小(150 mm×88 mm×47 mm)、记录时间长(大于5小时)、视频采集编码平均延时低(小于35 ms)、整机功耗低(约13 W)。本小型机载视频记录仪在无人机光电系统中得到了成功应用。在本文记录仪的基础上,我们下一步将利用视频编码过程中产生的编码信息来研究基于航拍感兴趣区域的视频编码,从而进一步提升视频记录仪的编码图像质量。

[1] 杨建新, 徐伟勤, 王玉刚. 机载记录视频信息化系统的设计与应用[J]. 计算机测量与控制, 2009, 17(7):1347-1349.

[2] 朱攀蓉, 姜红梅, 翟正军. 机载多路数字音视频记录系统的设计与实现[J]. 计算机工程与设计, 2006, 27(03):393-395,432.

[3] 程晓宇, 蔡 晔, 毕笃彦, 等. 基于龙芯PC104 Plus模块的机载视频记录系统[J]. 计算机工程, 2007, 33(02):189-190,193.

[4] Ruhul Amin Rana, Ri Li. Thermal protection from a finite period of heat exposure-Heat survival of flight data recorders [J]. Applied Thermal Engineering, 2015, 75(22):748-755.

[5] Texas Instruments. TMS320DM816x DaVinci video processors [DB/OL]. [2011-03/2015-03]. http://www.ti.com/lit/ds/sprs614f/sprs614f.pdf.

[6] Texas Instruments. TMS320DM816x DaVinci digital media processors technical reference manual [DB/OL]. [2011-03/2015-03]. http://www.ti.com/lit/ug /sprugx8c/sprugx8c.pdf.

[7] 刘 冰, 谷源涛. 基于DM8168的视频会议系统MCU设计与实现[J]. 计算机工程与设计. 2014, 35(10):3399-3403.

[8] Texas Instruments. SysLink UserGuide [DB/OL]. [2014-07/2016-08-05].http://processors.wiki.ti.com/index.php/SysLink_UserGuide.

[9] 付家才, 王海涛. 一种机载视频记录仪双处理器数据通信实现[J]. 计算机测量与控制, 2010, 18(7):1645-1647,1650.

[10] Younghun Kim, Dongkun Shin. Improving file system performance and reliability of car digital video recorders[J]. IEEE Transactions on Consumer Electronics, 2015, 61(2):222-229.

[11] 张立东, 程晓宇, 王社东, 等. 某型机载数字音视频记录系统的软件设计与开发[J]. 计算机工程, 2005, 31(6):213-215.

Design of Miniature Airborne Video Recorder Based on DM8168

Shi Yuanding1, Xu Xintao2, Wu Yinhua1, Zhu Wei2,3

(1.52th Research Institute, China Electronic Technology Corporation, Hangzhou 310012, China;2.College of Information Engineering, Zhejiang University of Technology, Hangzhou 310023, China;3.United Key Laboratory of Embedded System of Zhejiang Province, Hangzhou 310023, China)

A miniature airborne video recorder is designed based on heterogeneous multi-core processor DM8168 for the video storage and transmission of flying vehicle. First, DM8168 and FPGA processors are selected for the miniature and low-power hardware system. Second, the McFW structure based on the multi-core architecture of DM8168 is utilized to develop the capture and encoder of two channel 1080p60 video input, and each input is encoded into one H.264 main stream and another H.264 secondary stream. Finally, the video stream is send to FPGA by using GPMC bus for the local storage and the wireless transmission. Our video recorder is miniature, low power, large storage and low video delay, and it is very suitable for the multi-channel video processing of flying vehicle.

DM8168; flying vehicle; video recorder; H.264; GPMC bus

2016-08-26;

2016-06-21。

国家自然科学基金项目(61401398)。

石园丁(1977-),男,湖北黄冈人,硕士,工程师,主要从事嵌入式系统设计方向的研究。

朱 威(1982-),男,浙江丽水人,博士,副教授,主要从事视频编解码和图像处理方向的研究。

1671-4598(2017)02-0238-04

10.16526/j.cnki.11-4762/tp.2017.02.065

TP391

A