具备重构能力的三模冗余器载计算机研究

2017-03-21陈玉坤冯忠伟张声艳

陈玉坤,冯忠伟,张声艳,刘 冬

(中国运载火箭技术研究院 研究发展中心,北京 100076)

具备重构能力的三模冗余器载计算机研究

陈玉坤,冯忠伟,张声艳,刘 冬

(中国运载火箭技术研究院 研究发展中心,北京 100076)

器载计算机是航天器电气系统的重要组成部分,需要冗余技术来满足其高可靠性运行要求;为了保证航天器上计算机在出现异常故障时仍能正常工作,对传统三模容错结构、具有降级功能的三模容余结构的体系结构、算法原理、关键技术等内容进行了研究;综合使用多种检测机制确保可靠锁定故障机,基于故障机无法修复时再逐步降级使用的策略,以正常工作的当班机为基础,通过故障机在每个流程的开始读取刷新后的当班机指针和重要状态参数并在流程的结束向当班机发送同步请求的方式,提出了一种具备重构能力的三模冗余器载计算机设计方案,设计了三模冗余重构流程,使故障机具备自修复的能力;实践表明,该重构方法能有效地提高器载计算机系统的可靠性,对高可靠器载计算机设计与实现具有较好的工程参考意义。

三模;冗余;重构;计算机

0 引言

器载计算机控制航天器正常运行,因此,器载计算机的可靠性与安全性是航天器是否安全的重要保证。在空间轨道中,除空间站外,器载计算机一般不具备可维修性,一旦出现故障,极易造成航天器的在轨失效,从而给国家造成重大损失和恶劣影响。因此,器载计算机的冗余容错技术便成了亟待深入研究的课题。

1 三模冗余结构分析

三模冗余结构(TMR)系统可以采用三机也可以大于三机构成,但至少应该由三机构成。TMR结构系统采用三取二的策略实现系统的容错,三取二的系统是基于少数服从多数的原则,系统正常工作的前提是每一时刻系统中最多存在一个故障,即系统中只要有两个单机正确时就可以输出正确的结果。这种结构如图1所示。当系统中存在故障时,不进行隔离和重构,对于系统运行是透明的[1]。当系统存在两个或两个以上单机故障时,会失效。

图1 三模冗余系统结构

假设各单机的可靠度相等,用RM表示,表决器的可靠度用RV表示,则系统的可靠度为:

这种结构的关键是如何实现三取二,即表决器设计,其算法原理如图2所示。表决器的实现主要有两种方式,一是硬件实现的表决器,二是软件实现的表决器[2]。硬件表决器具有直观、快速的特点,但同时他本身是一个单点,若表决器输出出现问题则系统的输出错误。同时随着输出的路数增多,则表决器越来越复杂,可靠性也随之降低。对计算机性能的提高也产生影响。速度越高,则同步性也要求越高,实现起来也越困难。为了解决这个问题,可以采用软件表决硬件选通的方式,这种方式需要增加系统间的相互通信,以交换表决的信息,并且要有正确的状态表决决策输出选通电路[3]。软件表决解决了上述问题,但增加了系统中的时间开销,此外也需要解决同步的问题。

图2 三取二判决算法原理

2 具备降级功能的三模容错结构分析

TMR结构的容错在控制系统中得到广泛的应用。为了提高系统的可靠性和资源利用率,TMR结构的一种变形可以利用系统的容错策略实现具备降级功能的三模容错功能(以下简称TMR/S),其典型的应用即为返回式卫星的TMR/S容错结构。TMR/S结构是为了提高系统的实时可靠性而提出一种容错结构,其设计思路是正常工作时由三机表决,而出现故障时降为单机,从而提高系统的工作寿命。其主要结构特点是采用三机的冗余方式进行容错,通过仲裁和信息交换完成三机故障检测和判断,而最终一个功能正常的单机输出作为整个星载计算机系统的输出[4]。“神舟”载人飞船船载计算机也是基于这种容错体系结构开发的,这种结构提供了很高的实时可靠性,有力保证了任务的成功。

在TMR/S系统中包含三个具有相同硬件结构的单机同时运行功能完全相同的程序,每机采用相同的处理器。三机输入端为一对三的结构,输出端由硬件和软件组成仲裁管理控制单元,每次只允许其中一个计算机的输出信号向外输出[5]。这种容错体系结构如图3所示,除了三个硬件完全相同的冗余单机外,该结构主要有以下几个主要组成部分和关键技术:

图3 TMR/S三模容错结构

1)支持三机间的通信。通信采用串行方式,全双工发送和接收的方式。

2)支持系统的同步。同步分两个层次:一是宏观上的周期同步;二是微观上的同步。宏观同步利用系统的周期性控制特点,采用统一的时钟频率定时电路实现,该电路独立于三机,因此其可靠性与三机没有关系,时钟频率定时电路也采用冗余设计以保证其本身的可靠性;微观同步即周期内同步,目的是使三机中的本机不受另外两机影响。三机通信交互数据过程中,可能出现数据接收不完整或者接收超时,微观同步通过定时中断的方式在这种情况下采取一定措施来保证。

3)支持状态输出。每机根据本机的状态是正常还是不正常,输出状态送给仲裁管理控制单元,以决定当班机。

4)仲裁电路输出。这部分电路根据系统中各机的状态信号,并结合遥控指令,决定当班信号;并根据当班信号,决定哪个机器输出,此输出即为整个系统的输出。

仲裁管理控制单元是按照各单机工作情况或遥控指令控制三个单机中的一个单机输出,即三个单机输出的数据经过三取二表决后,发出本机工作正常信号,自主地根据三个单机的正常状态信号决定一个单机的输出,其他两个单机的输出均被封锁[6]。此外,遥控命令也可以控制某个单机输出,另外两个单机的输出被封锁。三机间数据交换由每一机上的微处理器负责实现,交换数据的物理链路采用串口实现。

这种容错体系结构采用软件表决、硬件实现的方式,它的突出特点是:抗瞬时故障能力强,同步性好;能保证在一个故障的情况下,系统正常工作,具有可靠性高、实时性好的特点。

3 具备重构能力的三模冗余器载计算机设计

从图3的TMR/S三模容错结构可以看出,由于三机具备对等同构容错的结构形式,且任意两机之间存在通信接口,为了充分利用系统资源,在一定条件下,出现故障时不仅仅降为单机,而是通过一定的策略实现故障机的恢复,从而实现系统重构。通过故障检测、故障定位、故障恢复等手段,变静态冗余为动态冗余,使系统重新恢复正常运行,进一步增加系统可靠性和使用寿命。

3.1 故障检测机制

三机(代号分别为:A机、B机、C机)的所有输入和输出信号均完全独立,故当其中一台发生故障时,故障单机接口上的错误不会影响其他两机,当班机仍可完成单机的全部功能,因此就接口和功能而言,系统上不存在单点失效的问题。为了可靠地检测出故障机,并且在出现故障的情况下,不影响单机的正常功能,通过自检、互检、他检三种检测模式来决定切权,以此来保障单机在出现故障时,三模冗余结构仍能正常工作,实现方式如下:

1)自检模式:所有的信号输出均通过软件进行标记,若发现自身输出异常,则发送异常反馈。处理器可以根据自身的错误状态判断,标识自身故障,控制自己不输出。同时,串口通信输出芯片的使能端通过硬件检测,若监测出芯片的使能端逻辑异常,则反馈故障信号给本机CPU,本机CPU通过交互缓存把故障信号发送给当班机的CPU,当班机的CPU对故障机进行控制断电。

2)互检模式:A机表决FPGA实时监测B机和C机表决FPGA以及自身的心跳信号;B机表决FPGA实时监测A机和C机表决FPGA以及自身的心跳信号;C机表决FPGA实时监测B机和A机表决FPGA以及自身的心跳信号,以此实现三个表决FPGA的状态互检。三个CPU通过各自的交互缓存获得其他两个CPU的工作状态和同步信息,以此实现三个CPU之间的互检。

3)他检模式:三个CPU将各自的数据和状态参数分别写进三个表决FPGA的双口RAM中,以供三个CPU分别从对应的表决FPGA读取三机的数据分别进行三取二表决,并把表决结果分别送给三个表决FPGA单元,三个表决FPGA再次进行三取二表决后,将最终结果反馈给三个CPU,以此来实现表决FPGA监测各个CPU的工作状态的他检。

若有一个表决FPGA未收到相应CPU的数据,则判断为CPU故障,表决FPGA单元将信息反馈给其余两个CPU,由其余两个CPU进行双机热备份降级工作。三机的CPU模块同时监测其他两机的供电状态信号,若发生供电异常,则认为一机已故障,进入双机模式的工作。

3.2 故障机重构方案

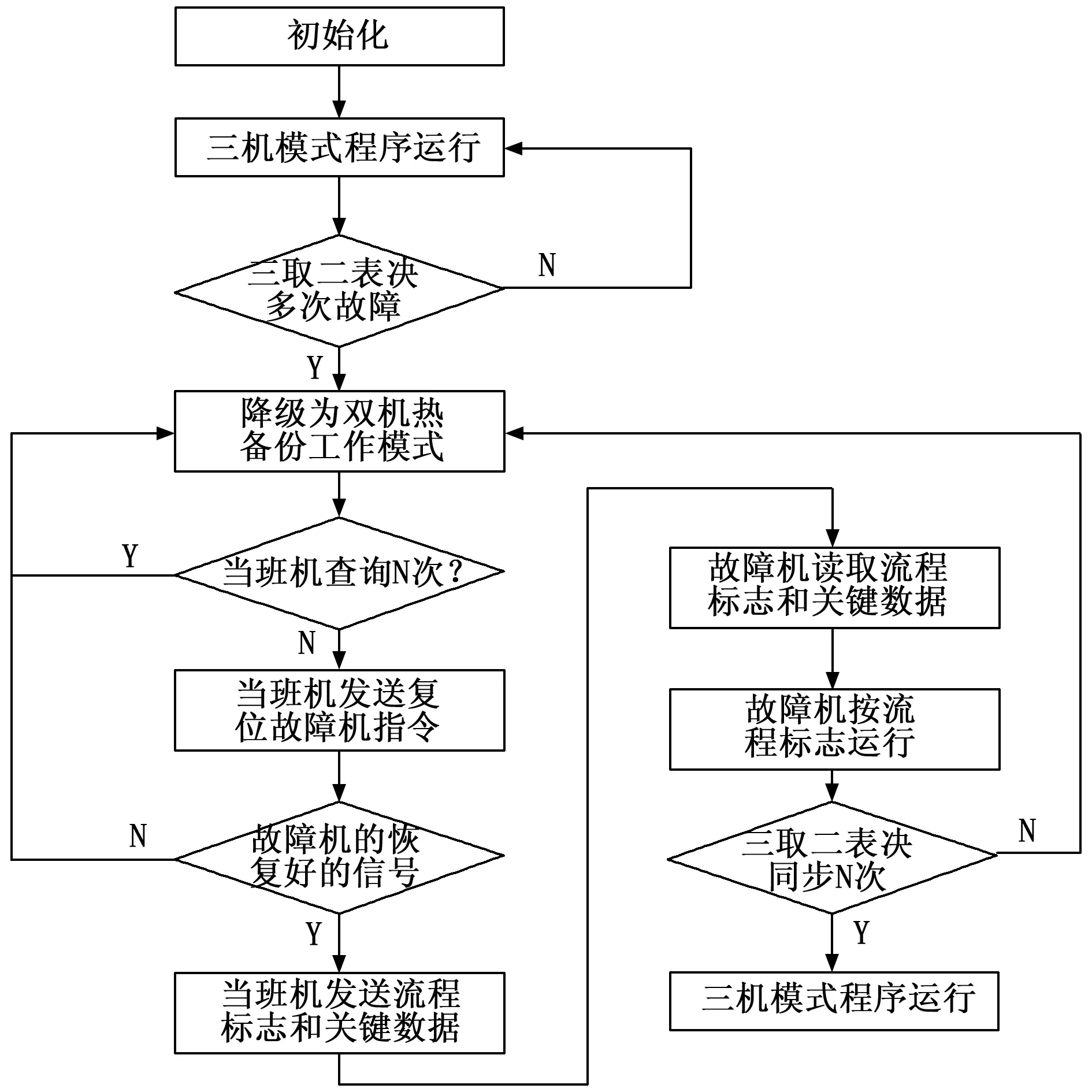

单机故障后的三机模式的重建:若三取二表决出一机软件故障,则正常的两机控制输出的同时,通过内总线上的复位引脚发送复位信号给故障单机,对故障单机的CPU进行复位处理;正常的两机降级为双机热备模式工作,设定为由其中一机当班输出。在随后的三机模式重构中,以该当班机为主,控制实现三机的重建。若出现故障的单机不可恢复,则故障单机全部的输出信号由CPU控制不输出,整机降级使用为双机热备份模式,即固定为其他两机中的一机输出,另一机热备份的模式。三机模式重构流程图如图4所示。

图4 三模冗余重构流程图

如图4所示,当三机的三取二表决多次出现一机硬件故障,则由当班机发送控制断电和重新上电指令,对故障机进行故障恢复;同时,当班机根据读取的断电状态控制进入双机热备份工作模式。故障机故障恢复后,实现三机模式重构的方式为:当班机在每个流程的开始将自身的PC指针和重要状态参数发送给故障机的表决FPGA;故障机在完成初始化后,开始读取当班机发送的参数,立即进入同步运行,并向其他两机的表决FPGA发送运算后的数据。多次(次数可根据需要设定)读取当班机的同步数据后,故障机在每个流程的结束通过“心跳监测”通道向当班机发送同步请求;当班机收到故障机的同步请求后,读取三机的数据,并对故障机的数据加标签,进行三取二表决,多次表决一致后,通过“心跳监测”信号发送故障恢复的三机同步信号,三机以双机模式的当班机为当班机恢复三机模式的运行。

在双机热备份期间,若当班机出现故障时,可以通过遥控方式、自主切换方式来实现器载计算机的当班机切换。当地面指控中心根据航天器的遥测数据能够判断出航天器当前工作计算机发生故障时,地面指控中心发送遥控切权指令,实现器载计算机的冗余切换;当采用遥控切换命令时,自主切换功能被封锁,当班机的输出切换根据遥控命令确定。为了封锁自主切换功能,通过遥控指令设置了遥控准/禁自主切换的时间窗口,当航天器处于准自主切换状态,才允许进行器载计算机的自主切换,否则不允许自主切换。在自主状态下当班机故障将执行备份机夺权指令,其自主赋权部分由积分电路完成,保证备份机在夺权时不能在一次或一条指令下完成,必须连续多次发出夺权指令,使积分电路的输出积累到一定的电平才能驱动继电器实现夺权,从而备份计算机成为当班机执行控制权。

3.3 试验结果与分析

在验证试验中,通过模拟设备对三模冗余容错计算机注入故障,分别就以下两种情况进行故障模拟:

1)三机中的A机在短暂断电指定时间后再次正常上电;

2)三机中的A机在断电后不再上电。

通过对三模冗余容错计算机的各机状态信号、心跳监测信号、输出信号及其系统输出数据监测,验证试验结果如下:

1)三机中的A机在断电期间,可以监测到三模冗余容错计算机没有中断当前的任务,仍正常工作;A机在上电后,A机经过与当班机的多次同步,可以实现重构并恢复为正常,具备在线修复能力,变静态冗余为动态冗余,最终工作于三机模式;

2)三机中的A机在断电后不再上电,即模拟出现永久故障,监测到三模冗余容错计算机仍正常工作,具备将故障单机从系统摘除的能力,并降级工作于双机备份工作模式,仍旧具备一定的冗余容错能力。

4 航天器高可靠容错计算机系统关键技术

4.1 余度管理技术

余度管理技术是对余度系统运行机制的筹划和对出现的问题的处理,是在已确定了的系统硬件/软件资源的余度配置等级的基础上提高系统可靠性的一项关键技术。余度管理技术包括通道之间的数据交换技术、信号的监控和表决以及故障检测与隔离技术等[7]。数据交换技术是信号监控和表决的前提条件;通过信号的监控和表决后就可以进行故障检测并对故障进行隔离。

4.2 高可信软件的构造与验证技术

在航天器计算机中,软件的作用越来越重要,保证软件的可信度和健壮性一直是容错技术研究的重要方面之一。因此研究提高现有软件容错技术应用的可靠性,构建软件的可信保障技术体系,同时利用形式化方法对空间软件进行验证,对可信性软件验证的集成环境进行开发。在航天器出现故障时,及时通过高可信软件的补偿、切换、隔离等措施,使航天器各部分功能的状态及执行结果更加可靠、可信。目前高可信软件容错技术主要有:回卷技术、软件陷阱、分布式恢复块、数据重表达技术等。

4.3 同步技术

同步技术是一个实时冗余容错计算机系统核心基础技术之一,是系统正确运行的前提。它用来消除系统中三个计算机模块之间因时钟、输入延迟等因素造成的异步度,使得系统中三个计算机模块在程序执行状态、周期定时及时间基准上达到相对一致的状态,使得三个计算机模块采集到相同的输入信号,在计算后同时将输出送给表决器进行表决输出,真正完成三模冗余功能。目前同步技术包括任务同步、中断同步、公共时钟、锁相同步、多级同步等多种方法。同步精度因具体实现不同而各有差异,多在几十微秒到几毫秒之间。

5 结束语

器载计算机的可靠性与安全性是航天器能否安全的重要保证,本文详细阐述了三模容错、具备降级功能的三模容错体系结构,提出了一种具备故障重构能力的三模冗余器载计算机设计方法,给出了动态重建的流程。实践表明,具备故障重构能力的三机能有效地提高器载计算机系统的可靠性,对空间恶劣环境条件下高可靠器载计算机设计与实现具有较好的工程参考意义。

[1] 杨孟飞,华更新,冯彦君,等.航天器控制计算机容错技术[M].北京:国防工业出版社,2014.

[2] 韩月涛,潘伟萍,杨 帆,等.基于FPGA的三模冗余UART电路设计[J].电子测量技术,2011(3):57-60.

[3] 徐 奡,夏德天,郑久寿,等.高升力系统控制计算机容错技术研究[J].微电子学与计算机,2015(6): 36-40.

[4] 肖爱斌, 胡明明, 任宪朝, 等.四模冗余拜占庭容错计算机可靠性分析[J].空间控制技术与应用,2014 (3): 42-46.

[5] 张 超,赵 伟,刘 峥.基于FPGA的三模冗余容错技术研究[J].现代电子技术,2011 (5):167-171.

[6] 姚 睿,王友仁,于盛林,等.具有在线修复能力的强容错三模冗余系统设计及实验研究[J].电子学报,2010(1):177-183.

[7] 高丽娜,杨宝奎.容错飞控计算机体系结构研究[J].战术导弹技术,2013(5):107-110.

[8] 徐文芳,刘宏伟,舒燕君,等.三模冗余容错系统管理板[J].清华大学学报,2011,51(S1):1434-1439.

Research on Reconfigurable Triple-module Redundancy Space On-board Computer

Chen Yukun,Feng Zhongwei,Zhang Shengyan,Liu Dong

(Research and Development Center, China Academy of Launch Vehicle Technology, Beijing 100076, China)

On-board computer system is the crucial component in spacecraft electronic system,and redundancy techniques can provide high reliability for on-board computer running. To ensure computer still work normally under fault condition, system architecture, principle and key technology of traditional and degraded triple-module redundancy computer are introduced. Some methods are adopted in order to reliably detect fault computer, on-board computer will work degradedly only which can not be renovated. Fault computer reads current computer’s pointer and crucial data at the beginning of every course, and sends synchronization require to current computer at the end of the course, then presents a design scheme of reconfigurable triple-module redundancy space on-board computer and designs reconfigurable flow. The scheme can make the fault computer has the ability of recovery. Practice indicates that the reconfigurable scheme can effectively improve the reliability of space on-board computer system, and the paper has engineering application value for design and implementation of space on-board computer system with high reliability.

triple-module; redundance; reconfigurable; computer

2016-09-21;

2016-10-18。

陈玉坤(1979-),男,河南卫辉人,博士,高级工程师,主要从事测控通信系统、数据管理系统方向的研究。

1671-4598(2017)02-0201-03DOI:10.16526/j.cnki.11-4762/tp

TP

A