一种应用于10位SAR ADC的高精度比较器电路设计

2017-03-10徐韦佳田俊杰李延标

徐韦佳,施 琴,田俊杰,李延标

(解放军理工大学 理学院,江苏 南京 211101)

一种应用于10位SAR ADC的高精度比较器电路设计

徐韦佳,施 琴,田俊杰,李延标

(解放军理工大学 理学院,江苏 南京 211101)

提出一种应用于10位逐次逼近型模数转换器(SAR ADC)的高精度比较器,具有精度高、功耗低的特点。该比较器采用差分结构的前置放大电路,提高输入信号的精度,其自身隔离效果减小了锁存器的回踢噪声和失调电压。动态锁存电路采用两级正反馈,有效提高比较器的响应速度。输出缓冲级电路增强输出级的驱动能力,调整输出波形。该比较器电路采用SMIC 65 nm CMOS工艺技术实现,使用Cadence公司Spectre系列软件对进行仿真,设置工作电压2.5 V,采样频率2 MHz,仿真结果表明,比较器的分辨率是0.542 5 mV,精度达到11位,失调电压为1.405 μV,静态功耗为63 μW,已成功应用于10位SAR ADC。

SAR ADC;高精度;比较器

0 引言

随着集成电路的发展,数字通信得到了广泛应用,模数转换器(Analog-to-Digital Converter, ADC)作为实现模数转换的关键器件,得到了快速发展[1]。在诸多不同结构的ADC类型中,逐次逼近型ADC(Successive Approximation Analog-to-Digital Converter, SAR ADC)具有面积小、功耗低、精度相对较高、输出数据无延迟的特点,广泛应用在消费电子、医疗设备、工业控制等诸多领域。而高精度比较器作为高性能SAR ADC的核心器件,其精度对ADC的性能起着至关重要的作用。因此,要实现高性能ADC,比较器的精度是关键。

当前对比较器的研究主要包括多级开环比较器、开关电容比较器、动态锁存再生比较器等。多级开环比较器具有较高的速度和精度,但是由于受到多级放大器的带宽限制,速度难以提升[2];开关电容比较器可以采用失调消除技术消除失调电压,提高精度,但是存在较为严重的电荷注入和时钟馈通效应,增加了设计难度;动态锁存比较器的响应速度快,但是回踢噪声和失调电压都比较大,不适用于高精度系统。因此,本文提出一种应用于10位SAR ADC的高精度比较器,采用前置差分预放大电路、两级正反馈Latch锁存判断电路和输出缓冲电路的结构,工作在2 MHz时钟频率下,失调电压低、回踢噪声小,精度达到11位,具有高精度、低功耗的特点,可以实现10位高性能SAR ADC的模数转换。

1 比较器结构的选取

比较器主要分为放大器结构的静态比较器和通过时钟触发工作的动态比较器。前者主要用于传统的连续时间电路,而后者广泛应用于开关电容电路。忽略漏电流的因素,动态比较器由于速度快、静态功耗几乎为零,多用于ADC系统中。然而,动态比较器由于较大的失调电压和回踢噪声,限制了分辨率的提高。

Latch锁存器作为动态比较器中的重要组成部分,沟道长度越短,输入信号越大,锁存器响应越快[3]。因此,为了提高响应速度,在锁存器前,前置一级差分放大电路,预先放大待比较信号,能够提高Latch的响应速度[3]。同时,差分结构可以去除误差信号成分,有效减少由直流失调电压、开关的时钟馈通效应、电荷注入效应而引起的误差。由于预放大电路内部和输出端加载隔离电路,使得其输出信号多次衰减后到达信号的输入端,能够有效减小回踢噪声对预放大电路输入端信号的影响。预放大锁存器的失调电压与正反馈锁存器相比较,有实质性降低。正反馈锁存器的失调电压通过预放大级,对输入管的贡献大幅度下降。因此,预放大锁存器的失调电压主要取决于预放大电路的失调。

一般传统的放大器的单位增益带宽为常数[4]。为了满足高精度的要求,前置预放大器的设计原则是高增益小带宽,然而过高的精度会降低比较器的速度[5]。因此,要为前置预放大电路选取合适的增益。

综上所述,如图1所示,Vip和Vin分别是差分对的两个输入信号,采用前置差分预放大电路作为比较器信号输入端,兼顾精度和速度的要求,其隔离电路减小了Latch正反馈产生的回踢噪声以及失调电压;Δu1和Δu2作为锁存电路的输入,Latch锁存电路采用二级正反馈来提高比较器的响应速度,小尺寸的MOS管可以减小传输延时;锁存器输出的高低电平VA和VB输入给缓冲级,输出级采用反相器级联,调整波形,减小延时,增加驱动能力,最终输出Vout1和Vout2两个高低电平。

图1 比较器电路结构原理图

2 比较器具体电路设计

2.1 前置差分预放大电路

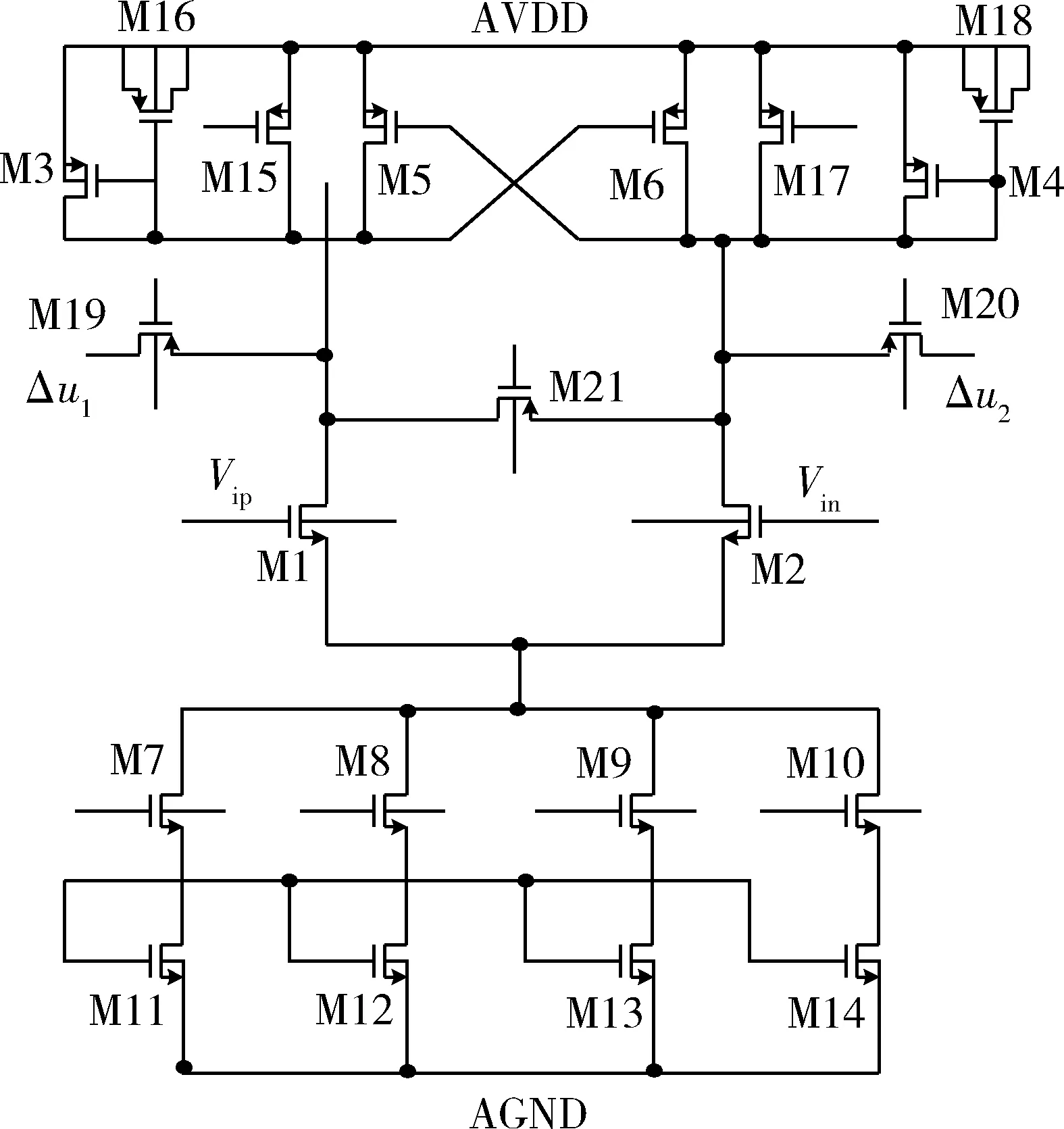

比较器的第一级采用的是前置差分预放大电路,如图2所示。NMOS管M1和M2分别作为差分放大器的信号输入端,Vip和Vin是两个待比较的输入信号。晶体管M15、M17和M21具有复位功能,当时钟信号为低电平时,将当前输出清为零。PMOS管M16和M18充当滤波电容,提高预放大电路的精度。尾电流由开关信号控制,当开关信号为低电平时,尾电流被关闭,比较器处于低功耗模式[6]。

图2 前置差分预放大电路

预放大器电路通过放大两个差分输入信号Vip和Vin,从而提高比较器的精度,降低比较器的设计难度。PMOS管M5和M6组成PMOS锁存电路。这是因为比较器需要具有锁存功能的放大电路。当信号输入,经过前置差分放大器的放大后,输入信号被锁存,并成为输出结果。此时,下一级的锁存电路不工作。在时钟信号的作用下,前置差分放大器停止工作,下一级的锁存电路在接收到上一级放大电路的输出结果后开始工作,并最终输出结果。

该前置放大电路有两条反馈路径。第一条反馈路径是晶体管M1和M2形成的电流负反馈。第二条反馈是晶体管M5、M6的栅漏极连接的电压正反馈。当正反馈系数小于负反馈系数时,整个电路将呈现负反馈,同时也失去了迟滞效应(如果实现反馈补偿,则成为传统的运算放大器)。否则,整个电路会呈现正反馈,产生迟滞效应,能够有效地过滤掉输入噪声[4]。这时:

如果β5/β3<1,则传输函数中没有延时;

如果β5/β3>1,则迟滞出现。

其中,β=(W/L)·K_(n·p)。

通过设置M3的宽长比大于M5,将该结构作为比较器的输入级,起放大作用,而非迟滞作用。

为了减少比较器设计的难度,在预放大级必须有一个大的增益。但是宽的带宽和大的增益是矛盾的,它们之间必须有一个折衷。

前置放大器级的增益可以表示为:

A=-gmM1R=-gmM1(gmM3-gmM5)

(1)

单位增益带宽表示为:

GBW=gmM1/C

(2)

gmM1,gmM3,gmM5分别是晶体管M1、M3和M5的跨导,C是前置差分放大电路的等效输出电容。由方程(1)、(2)可知,通过调整M1和M2的器件尺寸,可以使前置放大器获得适当的增益和带宽。

2.2 两级正反馈锁存电路

图3 两级正反馈锁存电路

比较器的第二级采用的是两级正反馈Latch锁存电路,如图3所示。PMOS管M26和M27构成PMOS锁存器,NMOS管M24和M25构成NMOS锁存器。两级锁存加速了正反馈响应,使得输入信号Δu1和Δu2快速进行比较,形成高、低水平输出。

锁存阶段有两种工作模式,分别是复位和再生[7]。在复位模式,尾电流源M32关闭以降低功耗,此时开关M30和M31导通,使锁存器输出VA、VB两个高电平。开关M28和M29导通,使上一次输出迅速复位,准备接下来的比较。在再生模式,开关M30、M31、M28和M29都截止。M26和M27的漏极电压拉至电源电压AVDD,加大锁存器中的电流差,并且提高增益。通过两个正反馈回路,输入的电压差Δu1和Δu2进行迅速比较,比较结果保持在锁存器中,直到重新开始复位模式。

在这个设计中,两个正反馈回路的结构,使锁存阶段有较大的增益、更快的再生和复位速度。锁存器的常数时间主要取决于通道长度。因此,采用了两对小尺寸的交叉耦合晶体管。通过调整输入对管的宽度,以确保载流子的流动性[8-9]。增加晶体管M22、M23的宽长比,这样在再生模式,就会有足够的电流来驱动锁存器迅速建立,减少响应时间。

2.3 输出缓冲级电路

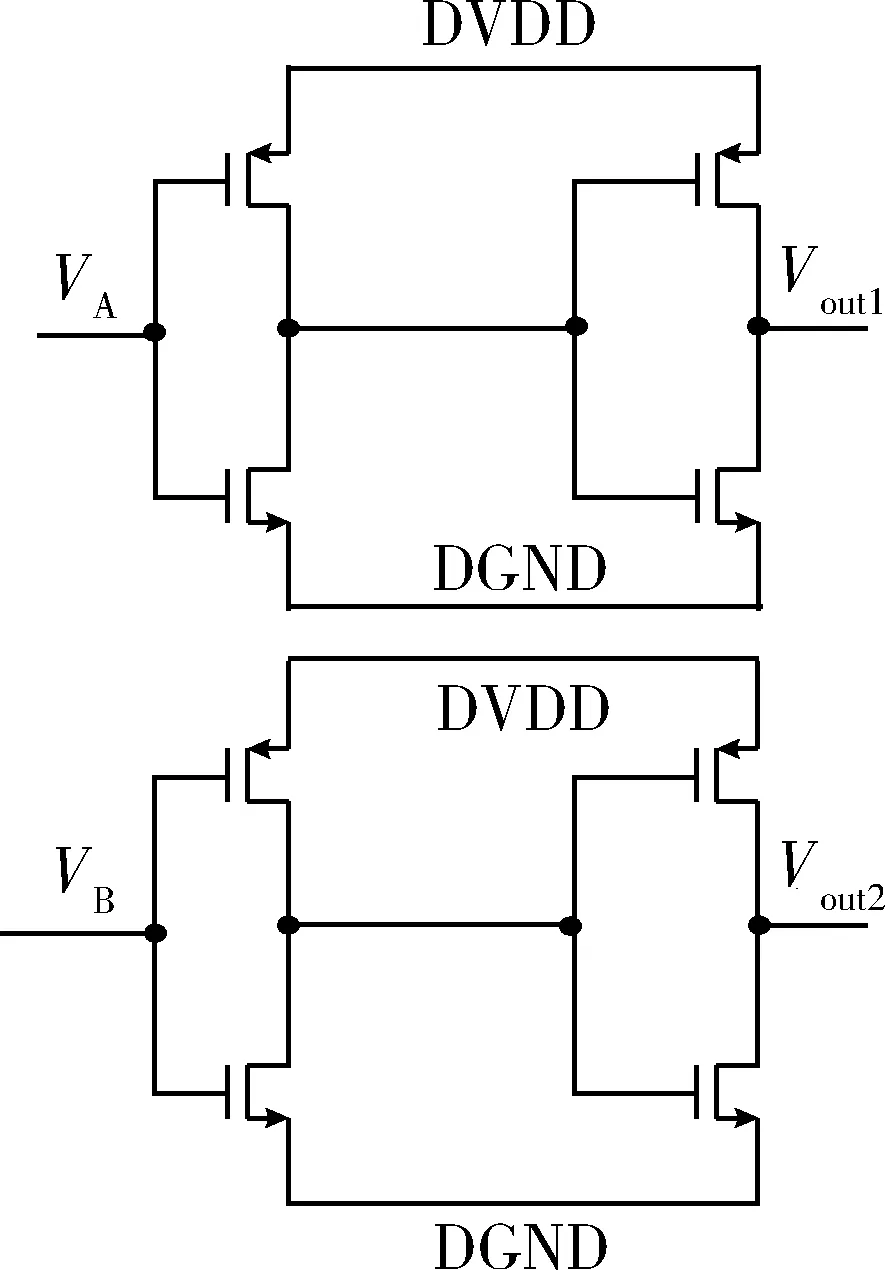

图4 输出缓冲级电路

比较器的第三级是输出缓冲级电路,如图4所示。输出缓冲级电路将锁存器输出的高低电平转换成逻辑电平,用于匹配数字电路。输出缓冲级由两级反相器组成。由于前一级输出电平未达到标准电平或波形不理想,两个反相器级联可以用于波形整形。同时增加了驱动能力,并降低了传输延迟。

3 电路仿真与分析

在SMIC 65 nm CMOS工艺下,设置电源电压为2.5 V,采样率为2 MHz,使用Cadence公司Spectre系列软件对设计的电路进行仿真。

3.1 前置差分预放大电路仿真

图5 前置差分放大器的频率特性曲线

图5是前置差分放大器的频率特性曲线。设置共模电平为1.25 V,输入差分信号分别为0.5 V和 -0.5 V。仿真结果表明,前置放大器的电压增益为19.55 dB,-3 dB带宽约738.9 MHz。

3.2 锁存器瞬态响应仿真

图6是锁存器瞬态响应的仿真结果。共模电压为1.25 V,复位信号频率为20 MHz,当锁存器的输入差分电压为1.085 mV时,锁存器的输出翻转,此时比较器的输入电压差为0.542 5 mV。因此,比较器的最小可分辨电压为0.542 5 mV,精度达到11位,符合对±0.5 LSB的分辨率要求(0.976 6 mV)[10]。

图6 锁存器瞬态响应

图7 Monte-Carlo方法模拟失调电压

3.3 比较器失调电压仿真

图7是比较器失调电压的仿真结果,采用Monte-Carlo方法进行模拟。仿真结果表明,该比较器的失调电压约为1.405 μV,满足设计要求。

比较器仿真结果如表1所示。

表1 比较器性能参数仿真结果

4 结论

本文提出了一种应用于10位SAR ADC的高精度CMOS动态闩锁电压比较器,工作于2 MHz采样时钟频率,2.5 V电源电压,采用SMIC 65 nm工艺实现。采用前置差分预放大电路、两级动态Latch正反馈锁存电路、输出缓冲级电路的设计,达到了要求的性能指标。仿真结果表明,该比较器的输入失调电压为1.405 μV,最小分辨电压为0.542 5 mV,精度达到了11位,静态功耗63 A6CCW,具有较高的分辨率和较低的功耗。目前,该比较器已成功应用于10位SAR ADC中。

[1] 毕查德·拉扎维(美). 模拟CMOS集成电路设计[M]. 陈贵烂,译.西安: 西安交通大学出版社, 2003.

[2] 郭永恒, 陆铁军, 王宗民. 一种高速高精度比较器的设计[J]. 微电子学与计算机, 2011, 28(1): 50-53.

[3] Tong Xingyuan, Zhu Zhangming, Yang Yintang. An offset cancellation technique in a switched-capacitor comparator for SAR ADCs[J]. IEEE Journal of Semiconductors, 2012,33(1):015011-1-015011-5.

[4] ALLEN P E, HOLBERG D R. COMS analog circuit design, Second Edition[M]. 北京: 电子工业出版社, 2002.

[5] 陈幼青, 何明华. 应用于14bit SAR ADC的高精度比较器的设计[J]. 微电子学与计算机, 2011, 28(6): 109-112.

[6] SHIKATA A, SEKIMOTO R, KURODA T, et al.A 0.5V 1.1 MS/sec 6.3fJ/Conversion-Step SAR-ADC with tri-level comparator in 40nm CMOS[J]. IEEE VLSI Circuits (VLSIC),2011,47(4):1022-1030.

[7] HERATH M M J, CHAN P K. A dynamic comparator with analog offset calibretion for biomedical SAR ADC applications[C]. IEEE 2011 International Symposium on Intergrated Circuits (ISIC), 2011:309-312.

[8] Yin Yongsheng, Jiang Xiangyang, Deng Honghui. The first stage of a SHA-less 12-bit 200-Ms/s pipeline ADC in 130-nm CMOS[C]. IEEE Anti-Counterfeiting, Security and Identification (ASID), 2013:25-27.

[9] 李建中, 魏同立. 一种CMOS动态闩锁电压比较器的优化设计[J]. 电路与系统学报, 2005, 10(2): 48-52.

[10] 吴晓波, 吴蓉, 严晓浪. 一种高精度动态CMOS比较器的设计与研制[J]. 电路与系统学报, 2007, 12(4): 119-123.

Designing a high precision comparator for 10-bit SAR ADC

Xu Weijia,Shi Qin,Tian Junjie,Li Yanbiao

(Institute of Science, PLA University of Science and Technology, Nanjing 211101, China)

A high precision comparator applied to a 10-bit successive approximation analog-to-digital converter (SAR ADC) is presented in this paper. It has the characteristics of high precision and low power dissipation. The differential structure of the preamplifier circuit improves the accuracy of the input signal, and its isolation effect reduces the effect of kickback noise and latch offset voltage. Two level dynamic latch circuit effectively improves the speed of comparator. Output buffer circuit increases the drive ability of the output stage and adjusts the output waveform. SMIC 65 nm CMOS process technology is used to realize the comparator circuit. Cadence series software Spectre is used to design the circuit simulation at the voltage supply of 2.5 V and sampling frequency of 2 MHz. The simulation results show that the resolution of the precision comparator is 0.542 5 mV, accuracy is 11 bit, offset voltage is 1.405 μV and static power dissipation is 63 μW.

SAR ADC; high precision; comparator

TN432

A

10.19358/j.issn.1674- 7720.2017.04.010

徐韦佳,施琴,田俊杰,等.一种应用于10位SAR ADC的高精度比较器电路设计[J].微型机与应用,2017,36(4):32-35.

2016-08-31)

徐韦佳(1989-),女,硕士研究生,助教,主要研究方向:集成电路设计。

施琴(1971-),女,硕士,副教授,主要研究方向:集成电路与系统。

田俊杰(1966-),男,硕士,副教授,主要研究方向:现代电子技术。