实时修正对时服务器秒脉冲的硬件实现方法

2017-03-02郑拓夫闫志辉

郑拓夫,杨 超,闫志辉

(许继集团有限公司电气技术中心,河南 许昌 461000)

实时修正对时服务器秒脉冲的硬件实现方法

郑拓夫,杨 超,闫志辉

(许继集团有限公司电气技术中心,河南 许昌 461000)

为满足新一代智能变电站技术规范的要求,使变电站安全稳定运行,并为时间同步装置提供稳定可靠的秒脉冲,提出了一种完全通过硬件实现的秒脉冲修正方法。该方法基于数字锁相环技术,对现有对时服务器的秒脉冲修正技术进行了优化。在FPGA内部以恒温晶振为激励,通过修正策略实时修正晶振分频秒脉冲的相位,使其与基准信号之间的相位差趋于零,且将每次修正的步长增量控制在纳秒级别。该方法在时间同步装置中得以应用,不但简化了现有修正方法的逻辑电路,而且提高了输出信号的精度和稳定度,可保证整个变电站系统的安全稳定运行。

智能变电站; GPS; FPGA; 数字锁相环技术; 秒脉冲; 实时修正; 恒温晶振

0 引言

根据新一代智能变电站技术规范要求,时钟同步装置需同时接收全球定位系统(global positioning system,GPS)和北斗卫星导航系统两种基准信号[1],以及IRIG-B码等同步信号。在运行过程中,时钟源信号切换或守时至同步状态时,秒脉冲(pulse per second,PPS)输出稳定,跳变不超过0.5 μs,对于异常抖动需纠错、拟合;在锁定及守时状态下,PPS输出跳变不超过0.1 μs[1]。

过程层合并单元、间隔层保护测控等装置,其数据采集方式极其依赖外部同步输入信号[2-3],如秒脉冲或者IRIG-B[4]。一旦外部输入丢失或者抖动就会造成采样数据的不同步,进而影响保护装置的判据,甚至可能引起拒动或者误动,并导致测控装置和电度表等设备计算错误[3]。

因此,时钟同步装置提供稳定可靠的秒脉冲输出,是满足规范要求以及消除变电站稳定运行隐患的必要手段。

现有的利用高精度晶振对授时基准源信号实时修正法[5-6],其补偿方案计算较复杂,样本数据量较大,对CPU的计算能力有较高要求,且精度不高(0.1 μs)。基于数字锁相环技术的秒脉冲产生方法[7],其逻辑电路较为复杂,硬件开销较大,需要CPU配合才能实现。

本文基于以上技术并加以改进,对现有对时服务器的秒脉冲修正技术加以优化。在FPGA内部,以恒温晶振为激励,通过修正策略实时修正晶振分频秒脉冲的相位,使其与基准信号之间的相位差趋于零;且将每次修正的步长增量控制在纳秒级别,从而简化现有修正方法的电路逻辑,提高输出信号的精度和稳定度。

1 原理概述

GPS和北斗授时源等基准信号与协调世界时间(coordinated universal time ,UTC)基准存在一定的随机误差,且服从正态分布[8-9],但其累计误差几乎为零,可忽略不计。

恒温晶振具有很高的频率稳定度,尤其在内部温度上升到一定范围后,其工作频率几乎稳定不变,所以通过恒温晶振分频得到的秒脉冲的随机误差可忽略不计。但是随着时间的增加,其累计误差也会增大[7-10]。基于该理论的实时修正秒脉冲法,以授时源基准信号为参考,实时修正晶振分频秒脉冲的累积误差,从而使输出的秒脉冲信号稳定、可靠。

本文对该修正方法进行了优化,采用恒温晶振与FPGA相结合的方法,在FPGA内部实现整个修正过程。FPGA内部延时小、运行速度快,逻辑实现具有高实时性和高稳定性;恒温晶振在FPGA内部可倍频为百兆频率,也保证了纳秒级别秒脉冲的精度。整个修正方法以FPGA内部高稳定度的计数器为实现基础,获得晶振分频秒脉冲与基准信号的相位差与频率差,并依据一定的修正策略实时修正晶振分频秒脉冲的输出步长,且每次输出的跳变都可达到纳秒级别,完全满足规范的要求。

2 方案设计

2.1 秒脉冲的产生

本文提出的方法通过基准信号选择、守时和秒脉冲修正三个功能模块配合实现。系统结构如图1所示。

图1 系统结构图

基准信号选择模块功能简单,负责对所有授时源输入信号依次进行质量分析,以选择并输出当前质量最优的基准同步秒脉冲信号。最优基准秒脉冲信号的选择策略,是按照优先级依次查询各个输入信号的同步状态(次序为:GPS、北斗、IRIG-B、其他同步信号、守时信号),选择当前优先级最高的同步输入源作为基准信号。

守时模块完成装置在所有授时源失步状态下的自守时功能[10],也可认为是基准信号选择模块的一个输入源。该功能在对时服务器中已得到广泛应用,且在许多文献中均有阐述,本文不再赘述。

秒脉冲修正模块是整个方法实现的核心,它的主要功能是,利用恒温晶振产生分频秒脉冲,并将其反馈回该模块输入源与SynPPS进行相位比较,然后根据修正策略实时修正相位偏差,最终消除基准源切换或状态切换过程中存在的抖动隐患。

2.2 秒脉冲时标的获取

在秒脉冲修正模块产生一种高精度和高稳定度的计数器,即在恒温晶振时钟的每个上升沿,自动加一,直至溢出翻转或者在秒脉冲上升沿清零并重新计数。

该类型计数器近似一个走时稳定的工作时钟,可作为标称秒脉冲之间相位关系的坐标轴。在每一个秒脉冲的上升沿时刻截取当前计数器的值,作为当前时刻的时标,从而对秒脉冲之间的相位差、步长差以及秒脉冲的输出时刻进行量化。

本方案产生了两个该类型计数器Osc_Tick和Syn_Tick。 Osc_Tick稳定走时,直至溢出翻转,用来获得每一个秒脉冲间隔计数,以及控制其输出步长和输出时刻; Syn_Tick稳定走时,在SynPPS的每一个上升沿清零,用来标称PPS与SynPPS之间的相位关系。

2.3 秒脉冲的修正

秒脉冲修正的实质是步长修正。根据秒脉冲上升沿的相位关系以及秒脉冲间隔计数的数学关系,修正步长。修正的最终手段是增加或者减少输出秒脉冲的计数间隔,即每秒的步长。

2.3.1 间隔获取

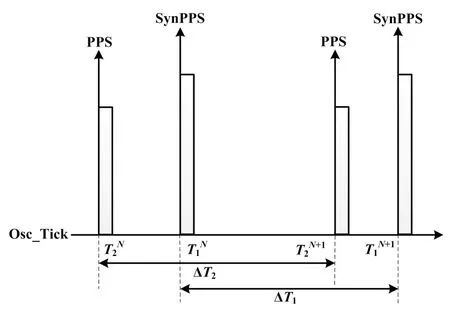

通过Osc_Tick可获得秒脉冲上升沿的时标(T1为SynPPS的时标,T2为PPS的时标),秒脉冲间隔示意如图2所示。

图2 秒脉冲间隔示意图

SynPPS的秒脉冲间隔可根据前后两秒上升沿的时标差得到,如式(1)所示:

(1)

同理,PPS的秒脉冲间隔ΔT2如式(2)所示:

(2)

2.3.2 相位比较

授时源切换后, SynPPS与PPS的相位关系如图3所示。图3中,θ为PPS与SynPPS的相位差。

图3 SynPPS与PPS相位关系图

Syn_Tick在SynPPS的上升沿清零,即T1时刻,Syn_Tick=0,则PPS上升沿时刻T2换算成Syn_Tick时标后,应为θ。

如图3(a)所示,PPS落在Syn_Tick坐标轴的前半周期(设ΔT1为整周期)时,表示PPS滞后SynPPS。将其转换为数学表达式,即θ需满足式(3)。

(3)

相反,PPS落在Syn_Tick坐标轴的后半周期,即θ满足式(4)时,可认为PPS超前SynPPS,如图3(b)所示。

(4)

由于SynPPS存在一定随机误差,每一秒的间隔计数无法保持一致[6],因此PPS的每次间隔调整,都不能保证其下一秒输出与SynPPS完全等相位。新一代智能变电站技术规范要求,输出秒脉冲上升沿的时间准确度δ≤1 μs[1],即可认为,当θ满足式(5)时,两者同相位。

(5)

2.3.3 步长调整

(6)

(7)

PPS经过修正后,与SynPPS逐步达成同相位关系,但若此刻PPS的间隔计数ΔT2与SynPPS的间隔计数ΔT1之差α(两者之差的绝对值,如式(8)所示)较大,则即使此刻两者实现了相位同步,最终也会因间隔计数ΔT2的超调或者欠调而导致PPS跟随失败。

α=|ΔT2-ΔT1|

(8)

3 方案实现

PPS修正过程如图4所示。

图4 PPS修正过程示意图

图4(a)表示时钟同步装置在授时源全部失步进入守时状态后,输出秒脉冲PPS上升沿滞后基准秒脉冲SynPPS 3.5 μs左右的情况。重新恢复授时源同步状态后,若直接跟随其输出,会存在一个大约3.5 μs的抖动。该结果不符合规范要求。

根据以上修正策略,将参数设置为δ=0.1 μs、ω=10 ns、α=20 ns,实时修正PPS的输出步长,渐进跟随SynPPS,直至达到相位一致。灰色部分为同步恢复后,PPS不断自我修正并最终达到与SynPPS相位一致的过程。在整个修正过程中,输出秒脉冲稳定可靠,每次步长增量保持在10 ns,完全满足规范要求。

图4(b)是 PPS超前SynPPS的状况下,外部授时源恢复同步状态后,两者相位趋于恢复一致的过程。

4 结束语

本文基于数字锁相环技术,对现有实时修正输出秒脉冲的方法加以改进,在不借助软件手段的条件下,完全通过FPGA硬件逻辑的高实时性以及恒温晶振的高稳定性得以实现。参考外部授时源的基准信号,实时修正FPGA内部产生的晶振分频秒脉冲,使两者相位最终达到一致。整个修正策略以FPGA内部产生的计数器为基础,准确量化了秒脉冲与基准信号之间的相位关系和频率关系,同时也将输出信号的精度控制在了纳秒级别,完全符合规范的要求。

该硬件实现方法简化了现有对时服务器的秒脉冲修正逻辑,降低了相应的硬件开销,提升了装置输出的稳定度、精度和应用价值,并且已在新一代对时服务器中得到了示范应用,完全满足了新一代智能变电站设计规范对时钟同步装置的性能要求。

[1] 国家电网.220kV新一代智能变电站二次系统通用技术规范[S].2013:51-53.

[2] 徐雁,吴勇飞,肖霞.采用FPGA & DSP实现电子式互感器合并单元[J].高电压技术,2008,34(2):275-279.

[3] 马超,李立京,李传.Sagnac型光纤电流互感器数据同步的研究[J].电力系统保护与控制,2012,40(8):38-43.

[4] 江涛,孙昕.GPS 与IRIG-B 在电网授时系统中的应用[J].继电器,2007,35(S1):333-335.

[5] 曾祥君,尹项根.GPS时钟在线监测与修正方法[J].中国电机工程学报,2002,22(12):41-46.

[6] 曾祥君,尹相根,林干等.晶振信号同步GPS信号产生高精度时钟的方法及实现[J].电力系统自动化,2003,27(8):49-53,89.

[7] 李泽文,姚建刚,曾祥君,等.基于数字锁相原理的GPS高精度同步时钟产生新方法[J].电力系统自动化,2009,33(18):82-86.

[8] 周水斌,田志国,赵应兵,等.满足IEC61850要求的站用时钟服务器[J].电力系统保护与控制,2010,38(7):56-58.

[9] LEWANDOWSKI W,PETIT G,THOMADS C.Precision and accuracy of GPS time transfer[J].IEEE Transaction on Instrumentation and Measurement,1993,42(2):474-479.

[10]黄翔,江道灼.GPS同步时钟的高精度守时方案[J].电力系统自动化,2010,34(18):74-77.

Hardware Implementation Method for Amending PPS of Time Synch Server in Real Time

ZHENG Tuofu,YANG Chao,YAN Zhihui

(Electric Technology Center, XJ Group Corporation,Xuchang 461000,China)

In order to meet the requirements of the technical specifications for new generation of smart substations,make the substations run more safe and stable,and to provide stable and reliable second pulse for time synchronization device,a hardware implementation method for amending pulse per second(PPS) is proposed.The method is based on digital phase locked loop technology,and optimizes the existing amending technologies for time sync server.Inside FPGA,with the thermostatic crystal oscillator as excitation,through the amending strategy,the phase of the crystal frequency division second pulse is corrected in real time,thus the phase difference from the reference signal tends to zero,and the step size of increment for each amendment is in nanosecond level.The method is applied in time synch device,it simplifies the logical circuit of existing method,and improves the accuracy and stability of output signal; this ensures safe and stable operation of the whole substation.

Smart substation; GPS; FPGA; Digital phase locked loop technique; Pulse per second(PPS); Real-time amendment; Oscillator

郑拓夫(1985—),男,硕士,工程师,主要从事智能变电站过程层设备、站用对时服务器等产品的研发。E-mail:15237443589@139.com。

TH86;TP29

A

10.16086/j.cnki.issn 1000-0380.201702023

修改稿收到日期:2016-08-27