基于新型电容阵列切换方式的10位低功耗SAR ADC

2017-03-01孙甜甜

孙甜甜

(西安邮电大学 电子工程学院,陕西 西安710121)

基于新型电容阵列切换方式的10位低功耗SAR ADC

孙甜甜

(西安邮电大学 电子工程学院,陕西 西安710121)

文中提出了一种10位低功耗逐次逼近(Successive-Approximation-Register,SAR)模/数转换器(Analog-to-Digital Converter,ADC),内部数/模转换网络采用一种新型的电容阵列开关切换方式,通过分段电容阵列、时序初始化和子参考电压来降低能耗,相比传统结构电容阵列的转换能耗减小了97.6%,单位电容数量减小了87%。整个ADC采用65 nm CMOS工艺进行设计,当采样频率为50 KS/s,输入正弦波信号频率为1.5 kHz左右时,ADC的有效位数(Effective Number of Bits,ENOB)为9.91位,总功耗低于450 nW,面积为136 μm×176 μm,非常适合植入式生物医疗电子的应用。

模/数转换器;逐次逼近;新型电容开关切换技术;分段电容;低功耗

目前集成电路特征尺寸已经减小到纳米级,片上系统 (System-on-Chip,SoC)的集成度也大幅提高。逐次逼近 (Successive-Approximation-Register,SAR)模/数转换器 (Analog-to-Digital Converter,ADC)凭借结构简单、面积小、功耗低等优势,广泛应用于无线植入式生物医疗电子器件、无线传感网络等低功耗领域[1-2]。最近几年,关于SAR ADC中低能耗D/A转换网络的研究日益增多[3-15],其中,文献[3]通过拆分最高有效位(Most-Significant-Bit,MSB)对应的电容来节约能耗,文献[4]中提出了一种单调向下的电容阵列切换方案,有效减小了转换能耗,文献[5]通过利用子基准电压Vcm来降低能耗,文献[6]通过将Vcm与单调切换技术相结合来进一步优化电容阵列的转换能耗,文献[7]和[8]在转换最高3位时均没有能量消耗,文献[9]采用多基准电压和时序初始化的方式来降低电容阵列的能耗。然而,文献[3-6]中提出的方法在面积、能耗方面还有优化空间,文献[6-8]中的方法,虽然功耗较小,但时序逻辑比较复杂,文献[9]中虽然减小了电容阵列的能耗,但子基准产生电路会消耗一定量静态功耗。综合以上,针对逐次逼近ADC的低功耗电容阵列切换方式,还有待进一步深入研究。

文中在传统电容阵列切换方式的基础上提出了一种新型低功耗电容阵列切换方式,通过分段电容阵列结构、时序初始化以及低功耗多基准电压产生电路相结合,有效降低了ADC的功耗。

1 SAR ADC整体电路设计

文中提出的10-bit SAR ADC系统结构主要包括采样/保持开关、DAC电容阵列、比较器和逻辑控制电路,如图1所示,其中,Vip与Vin为差分输入信号,Vref为参考电压,Vp和Vn为电容阵列开关控制信号,D9~D0为数字输出。整个SAR ADC采用“二进制搜索”的原理进行逐次逼近转换。模拟差分输入信号经过采样后进入DAC电容阵列,比较器对DAC电容阵列的输入进行比较,逻辑控制电路根据比较器的结果产生相应的信号控制DAC电容阵列开关的连接,从而进行电荷再分配,电容阵列输出新的电压再送至比较器进行比较,周而复始,最终产生全部的10-bit数字信号。

图1 基于新型电容阵列切换方式的SAR ADC系统结构

文中10-bit SAR ADC主要模块电路的具体设计如下:

1)DAC电容阵列采取新型的电容阵列切换方式,基于分段电容阵列结构,重点改进了冗余电容结构,与已有的D/A转换结构相比,有效的降低了功耗和面积。

2)采样/保持电路采用自举开关[4],具有近似恒定的导通电阻,与传统的MOS开关以及CMOS开关相比,能够提高ADC的线性度。

3)采用动态比较器电路[4],不仅比较速度较快,而且功耗低。

4)逻辑控制部分采用简化的电路结构[11],与传统触发器逻辑控制电路相比,晶体管数目显著减小,逻辑电路的速度、功耗及面积都能得到优化。

2 新型电容阵列切换方式

文中提出了一种改进的电容阵列切换方式,从图1可以看出,电容阵列中的电容C7~C1成2的倍数递减,即C7=26C,C1=C,其中C为单位电容。冗余电容基于分段结构实现,如图2所示。在采用分段电容的形式下,整个冗余电容阵列的有效电容值仍为C,因此避免了传统分段电容阵列中出现非整数的耦合电容。由于新结构中冗余电容多出两路分支,所以可以通过两个参考电压Vref和0产生相应的子参考电压,不仅降低了功耗,还大大降低了MSB电容的值,进而减小了单位电容数目和芯片面积。

图2 冗余电容等效电路图

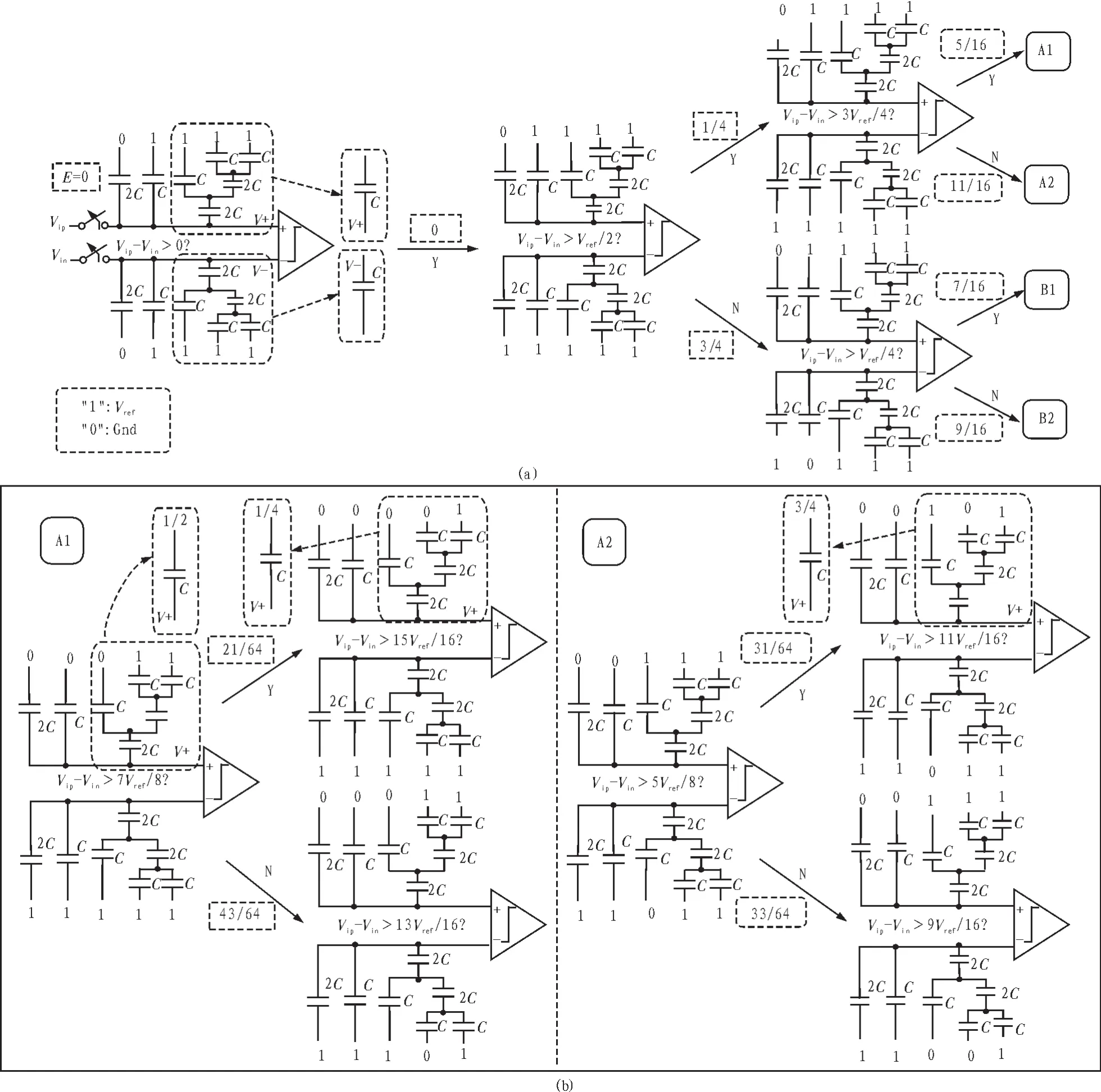

图3 所示的是一个以2-bit差分电容阵列实现5-bit的A/D转换的电容阵列切换方式,在采样阶段,采样开关闭合,差分电容阵列的上极板分别连接Vip和Vin,同时下极板接初始序列“0 1 1 1 1”。其中,“0”表示电容下极板接地,“1”表示电容下极板接Vref。当采样开关断开,输入电压被电容阵列保持,比较器进行第一次比较产生MSB。在产生MSB的过程中电容阵列消耗任何能量。在MSB确定之后,低电平端的MSB电容接至Vref,其余电容均保持不变,比较器进行新的比较产生第二位数字输出,此后的切换方式与文献[4]中的单调转换方式一致。

图3(b)文中提出方案中最后两位的产生过程。从图3(a)中的A1、A2可以看出,需要额外的子参考电压(Vref/2、Vref/4和3Vref/4)来实现后续的转换。文中采取改进的冗余电容结构产生相应的子参考电压,每个分段子阵列只产生一位,因此,分段电容阵列中的两个耦合电容值均为2C,相比传统的2-bit分段电容阵列中的耦合电容(4C/3),在工艺实现上具有更高的准确性。

图3 5-bit ADC的切换方式和能耗示意图

3 设计结果分析

基于Matlab工具,对采用各种电容阵列切换方式的10-bit SAR ADC进行了建模验证。表1对电容阵列的转换能耗以及单位电容数目进行了对比。与传统结构相比,文中所提出的方案减少了97.6%的平均能耗和87%的单位电容数目。

表1 10-bit SAR ADC能耗面积对比

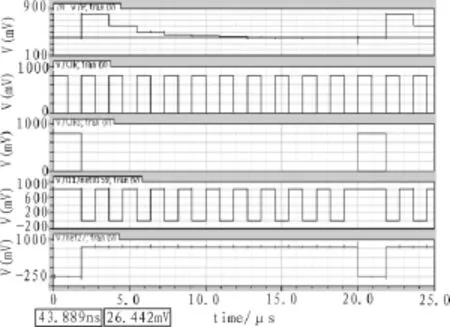

整体电路的仿真结果如图4所示,从上到下信号依次为比较器差分端输入信号,时钟信号Clk,采样信号Clks,逻辑电路使能信号Valid与比较器使能信号EN。在第一个时钟周期采样后,还需要10个周期来产生每一位的数字输出,因此完成一次10位的A/D转换,需要11个时钟周期。SAR ADC核心电路版图如图5所示,面积为136 μm×176 μm。

图4 SAR ADC整体仿真图

图5 SAR ADC版图

在输入为1.513 6 kHz正弦波时,总功耗为447.46 nW,图6(a)所示的是1024点FFT的仿真结果,其中,SNR=61.68 dB,SNDR=61.42 dB,ENOB=9.91 bit。当输入正弦波频率(24.951 kHz)接近奈奎斯特频率时,SNR=61.37 dB,SNDR=61.17 dB,ENOB=9.87 bit,如图6(b)所示。

图6 SAR ADC动态仿真结果

4 结 论

文中提出了一种应用于SAR ADC的新型电容阵列,并基于65 nm CMOS设计了一个10-bit低功耗SAR ADC。通过采用时序初始化、电容拆分以及低功耗子基准电压产生相结合,与传统电容阵列相比,本文提出的新型电容阵列切换方式平均能耗降低了97.6%,单位电容个数减少了87%。整体ADC的功耗小于450 nW,非常适合植入式、穿戴式生物电子学芯片等低功耗系统的应用。文中后续的研究内容是优化电路结构,降低ADC功耗,同时在版图布局布线方面进行优化,进一步减小芯片面积。

[1]Huang G Y,Chang S J,Liu C C,et al.A 1-μW 10-bit 200-kS/s SAR ADC with a bypass window for biomedical applications[J].IEEE Journal of Solid-State Circuits,2012,47(11):2783-2795.

[2]Yuan C,Lam Y Y H.A 281-nW 43.3 fJ/conversionstep 8-ENOB 25-kS/s asynchronous SAR ADC in 65nm CMOS for biomedical applications[C].IEEE International Symposium on Circuits and Systems. Beijing,2013:622-625.

[3]Ginsburg B P,Chandrakasan A P.An energy-efficient charge recycling approach for a SAR converter with capacitive DAC[C].IEEE Int.Symp.Circuits and Systems,2005,43:184-187.

[4]Liu C C,Chang S J,Huang G Y,et al.A 10-bit 50-MS/s SAR ADC with a monotonic capacitorswitching procedure[J].IEEE J.Solid-State Circuits,2010,45(4):731-740.

[5]Zhu Y,Chan C H,Chio U F,et al.A 10-bit 100-MS/s reference-free SAR ADC in 90nm CMOS[J]. IEEEJ.Solid-StateCircuits,2010,45(6):1111-1121.

[6]Zhu Z,Xiao Y,Song X L.Vcm-based monotonic capacitor switching scheme for SAR ADC [J]. Electronics Letters,2013,49(5):327-329.

[7]Tong X,Ghovanloo M.Energy-efficient switching scheme in SAR ADC for biomedical electronics[J]. Electronics Letters,2015,51(9):676-678.

[8]Tong X,Zhang Y.98.8%switching energy reduction in SAR ADC for bioelectronics application[J]. Electronics Letters,2015,51(14):1052-1054.

[9]Tong X,Zhang W,Li F.Low-energy and areaefficient switching scheme for SAR A/D converter [J].Analog Integrated Circuits and Signal Processing,2014,80(1):153-157.

[10]Tong X,Zhu Z,Yang Y.Analysis and modeling of an improved dual-array D/A network for SAR A/D converter [J].Analog Integrated Circuits and Signal Processing,2012,70(3):417-420.

[11]Zhu Z,Liang Y.A 0.6-V 38-nW 9.4-ENOB 20-kS/s SAR ADC in 0.18-CMOS for medical implant devices[J].IEEE Transactions on Circuits and Systems I:Regular Papers,2015,62(9):2167-2176.

[12]Wang H,Zhu Z.Energy-efficient and referencefree monotonic capacitor switching scheme with fewest switches for SAR ADC[J].IEICE Electron. Express,2015,12(7):20141202.

[13]Tong X,Zhu Z,Yang Y,et al.D/A conversion networks for high-resolution SAR A/D converters [J].Electronics Letters,2011,47(3):169-171.

[14]Yuan C,Lam Y.Low-energy and area-efficient Trilevel switching scheme for SAR ADC [J].Electronics Letters,2012,48(9):482-483.

[15]Harpe P,Dolmans G,Philips K,et al.A 0.7 V 7-to-10 bit 0-to-2 MS/s flexible SAR ADC for ultra low-power wireless sensor nodes[C].Proc.ESSCIRC,2012:373-376.

A 10-bit low power SAR ADC with an improved capacitive switching scheme

SUN Tian-tian

(School of Electrical Engineering,Xi'an Univ.of Posts&Telecommunications,Xi'an 710121,China)

A 10-bit low power SAR(Successive-Approximation-Register,SAR)ADC(Analog-to-Digital Converter,ADC)is proposed in this paper.The internal digital-to-analog conversion is designed with an improved capacitive switching scheme.By using split-capacitor array,sequence initialization and subreference voltage,the switching energy is reduced by 97.6%and the number of the unit capacitor is reduced by 87%,compared with the traditional structure.The 10-bit ADC is designed based on a 65nm CMOS process.When 1.5 kHz fully-differential input signals are sampled at 50 KS/s sampling rate,the ENOB of the ADC is 9.91.The power consumption of this ADC is less than 450nW,and the area is 136 μm×176 μm,making this proposed ADC very suitable to implantable bioelectronics.

analog-to-digital converter;successive-approximation-register;improved switching scheme;split-capacitor;low-power

TP302

:A

:1674-6236(2017)02-0080-05

2016-01-30稿件编号:201601289

陕西省教育厅科研计划项目资助(12JK0542)

孙甜甜(1991—),女,山西运城人,硕士。研究方向:混合信号集成电路设计。