可实时编程的高频信号源设计

2017-02-17北方工业大学电子信息工程学院雷丁阳周传宝

北方工业大学电子信息工程学院 张 袁 雷丁阳 冯 宇 周传宝

可实时编程的高频信号源设计

北方工业大学电子信息工程学院 张 袁 雷丁阳 冯 宇 周传宝

本设计主要是利用单片机控制可编程时钟芯片CDCE906来进行高频信号源的设计。单片机本身没有I2C接口,但其可以利用I2C技术用软件模拟出I2C总线的工作时序,将控制数据发送到CDCE906的I2C接口,控制CDCE906实时发送时钟信号,由于高频信号会发生幅度衰减,所以通过OPA690对信号进行放大,进而达到所需目的。

CDCE906;单片机;OPA690;I2C接口

1 信号发生器硬件电路设计

1.1 硬件电路部分

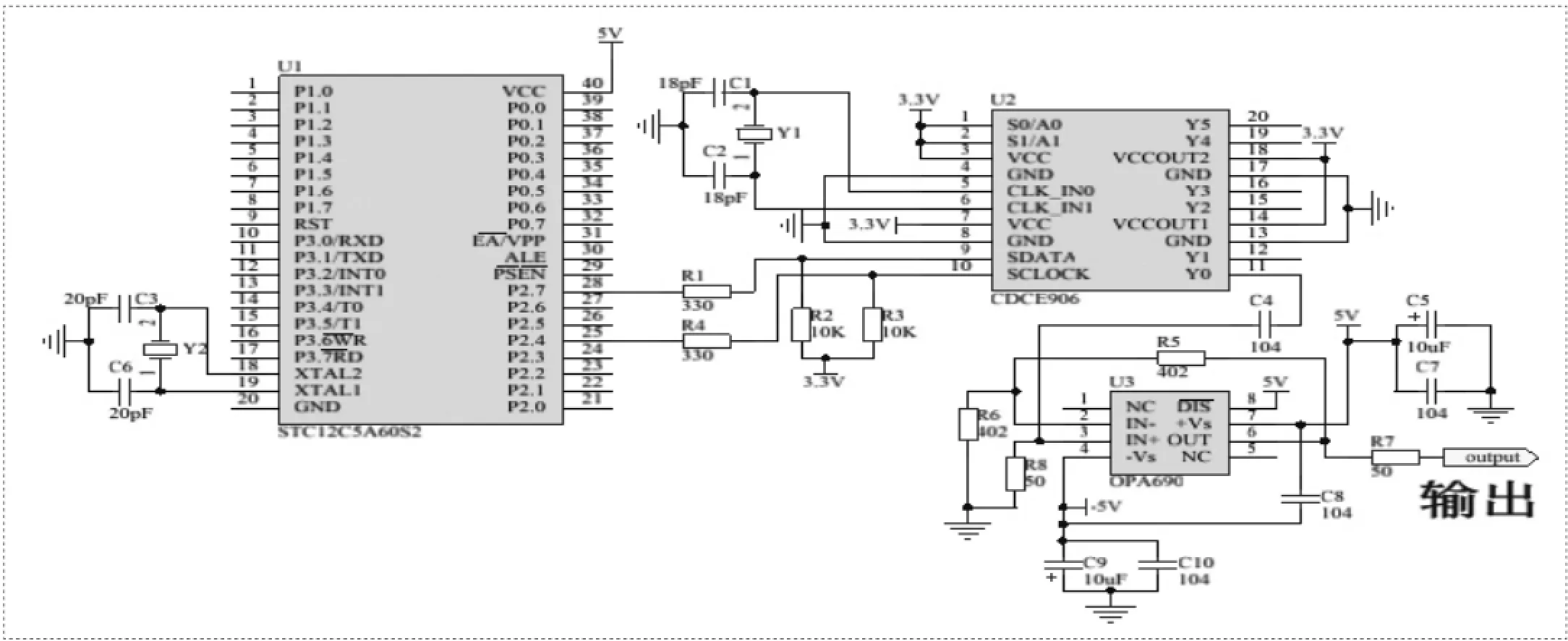

STC12C5A60S2通过软件模拟I2C接口控制CDCE906产生频率信号的硬件电路原理图如图1所示。STC12C5A60S2为5V单片机,CDCE906的供电电压是3.3V,单片机在于CDCE906通信时在总线SDA和SCL上分别串联了一个330欧的电阻以防止CDCE906被烧坏。单片机的晶振为11.0592MHZ、CDCE906的晶振为10MHZ。当频率信号从Y0输出时,是一个中值为1.5V的方波信号,经电容C6滤除直流分量后经OPA690放大,OPA690的放大倍数为2倍。

1.2 CDCE906简介

可实时编程时钟芯片CDCE906是德州仪器推出的一款高稳定性时钟乘法器,可提供60ps的低周期抖动和系统扩频时钟(SSC)技术。该器件内部拥有3个锁相环(PLL),可以通过单个时钟源实现6路输出。设计人员可对器件的3个电路内锁相环(PLL)组件进行实时编程,每路最高输出频率可达167MHZ。CDCE906的另一个性能提升在于其可实时编程的扩频时钟(SSC),不仅可以降低系统的电磁干扰,还可以减小对金属外壳的依赖。

CDCE906可以接收的晶振频率范围为8MHZ到54MHZ,也可通过LVCMOS或者差分输入时钟,本设计采用的是外部晶振提供时钟信号。设计人员可通过S1、S0、SDATA和SCLOCK 四个管脚对其进行控制。

1.3 OPA690简介

OPA690是一种具有禁用功能的宽带增益电压反馈运算放大器,其使用一个新的高转换率输入,一个新的输出级芯片结构使输出高电流占用较小的空间,这些技术结合起来提供了优秀的单电源运放。其还具有高转换速率(1800V/us)、高输出电流(190mA)、高输出功率能力、单位增益可达500MHZ、灵活的电源供电范围(单电源电压范围为5V到12V,双电源电压范围为±2.5V到± 5V)等特性。

2 软件控制指令设计

2.1 I2C总线说明

图1 信号发生器硬件电路

CDCE906通信采用的是I2C总线协议,最高传送速率可达400kpbs。I2C总线为同步传输总线,它仅用两条线就能实现主从设备简单双向通信,其中SDATA为串行数据线,负责串行数据的双向传输,而另一条线则是串行时钟线,负责发送同步时钟信号。I2C总线一般工作在主从工作模式下,即单片机为主设备,其它挂接在I2C总线上的器件为从设备。主设备负责产生时钟信号、发出启动命令、传输数据、停止通信等等,从设备则完成各种通信任务。STC12C5A60S2本身没有集成I2C总线接口模块,但单片机只要通过软件正确的模拟出I2C总线的工作时序,单片机就能与拥有I2C接口的器件或设备进行通信。

2.2 CDCE906控制指令说明

CDCE906拥有两种写操作方式,方便不同的用户需求:一种是字节写(Byte Write)操作,另一种是块写(Block Write)操作。CDCE906所有字节都有缺省值,只需改动其中少数几个地址,不连续的字节就能获得所需结果。如果想要修改多数字节,建议使用块写方式,块写方式更为方便。本设计使用的是字节写方式对相应字节进行修改。

CDCE906的通信协议中S为启始条件,Slave Address为将要写入芯片的地址,通过S1、S0管脚控制芯片的地址,就可以实现单片机对相应的CDCE906芯片进行读写操作。Wr为单片机对芯片进行读写操作,当Wr=1时表示对其进行读操作,当Wr=0时表示对其进行写操作。A表示应答信号,当单片对其进行写操作时,写入时CDCE906会返回一个低电平,未写入则返回高电平。CommandCode的最高位(即第8位)为块读写、字节读写操作选择位,当其为0时为块读写操作,当其为1时为字节读写操作。CommandCode的低7位为读写字节的偏移地址。在对CDCE906进行写操作时,都是按照从低字节到高字节的顺序进行的。写完之后CDCE906会返回一个应答信号表示是否写入成功。

CDCE906的S1、S0管脚为控制管脚,在缺省条件下S1控制CDCE906输出是否被禁止,S0控制CDCE906是否处于休眠状态,二者均为低电平有效。当CDCE906的第10B的最低四位全为1时,S1、S0就成为地址选择引脚,此时S1、S0的状态要Slave Address的最低两位相对应。本设计只对单个CDCE906进行读写操作,所以第10B的第四位使用默认缺省值0000,Slave Address使用缺省值1101001。将S1、S0管脚始终置高,如图1所示,S1、S0均接3.3V。

2.3 CDCE906频率的计算

在给定晶振频率(f)后,CDCE906的输出频率可以通过公式计算得到:

其中M、N是PLL的乘法器/除法器的值;P是锁相环输出的分频因子。M的值要尽可能的小以优化抖动性能,M要小于等于N(N/M>=1)。M、N、P的取值范围为1~511、0~4095、1~127。

2.4 控制程序设计

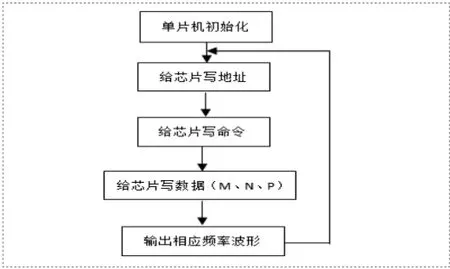

单片机控制CDCE906输出相应频率的程序流程图如图2所示。单片机通过改变CDCE906内部的M、N、P的值就可以得到不同频率的方波信号。

图2 单片机控制CDCE906芯片的程序流程图

3 结束语

将编写好的程序通过串口下载到单片机上,再给单片机和CDCE906供电,通过示波器可以看到输出稳定的方波信号。再通过单片机改变CDCE906内部的M、N、P的值,又可以得到不同的频率信号。也可以将M、P设置为定值,通过改变N的值可使CDCE906输出扫频信号,信号源可应用于多种场合。

[1]陈宏希.学练一本通:51单片机应用技术[M].北京:电子工业出版社,2013.

[2]王子剑,徐钊,房咪咪,等.基于电驻波的锚杆长度测量仪设计[J].煤矿安全,2012,43(9):111-113.

[3]徐钊,房咪咪,周红伟,等.基于电驻波的锚杆长度无损测量方法[J].工矿自动化,2013,39(9):112-115.

[4]赵博,李林,姬红兵.CDCE906倍频性能分析[A].西安电子科技大学,2011.

[5]杨立永,杨日杰,董云龙.基于CDCE949的可控频率源设计与实现[J].电子设计工程,vol.9,no.5,2011.

致谢:本论文由“2016年度北京市大学生科学研究与创业行动计划”支持。