DE1-SoC开发平台上的图像采集系统设计*

2017-02-09邓海涛吴捷李建辉潘国成陈耀文

邓海涛,吴捷,李建辉,潘国成,陈耀文

(1.汕头大学 工学院,汕头 515063;2.汕头华汕电子器件有限公司)

DE1-SoC开发平台上的图像采集系统设计*

邓海涛1,吴捷1,李建辉2,潘国成1,陈耀文1

(1.汕头大学 工学院,汕头 515063;2.汕头华汕电子器件有限公司)

本文详细介绍了基于Altera片上系统FPGA的嵌入式系统的设计方法,包括基于Qsys的系统硬件设计和基于片上系统EDS嵌入式软件设计。该设计采用Altera公司提供的soc_training image镜像内核文件,写入外存SD卡中,进行启动Linux操作系统,在QSYS中构建所需的硬件模块,在EDS开发套件平台上编写应用软件程序,最后通过板级验证实现系统功能。该系统通过FPGA的Video-in接口,实现了图像的捕捉功能,并存入到外设SD卡。

嵌入式设计;FPGA;硬核处理器;图像采集

引 言

数字图像技术广泛地应用到很多领域,如远程监控、航天航空、生物医学工程、机器人视觉、视屏和多媒体系统等。伴随着EDA技术[1]的飞快发展,各种新型的超大规模集成电路芯片也开始不断涌向市场。为了适应国内外市场的发展,2013年Altera公司推出了的SoC FPGA芯片,该芯片系列在原有的基础上内嵌了强大功能的ARM Cortex-A9处理器[2],不仅可以在单片的FPGA实现传统的硬件描述语言逻辑设计,还可以实现基于ARM处理器的嵌入式系统软件开发。

1 系统总体设计

1.1 开发环境

本设计采用Altera公司的集成开发环境Quartus II和嵌入式设计套件Altera SoC EDS,完成了图像采集系统的硬件和软件的设计。在Quartus II软件的开发平台下,设计者可以完成设计输入、分析映射、综合优化、时序分析、布局布线、期间引脚分配、FPGA逻辑功能仿真验证和目标程序下载等功能。Quautus II内嵌了Qsys嵌入式硬件系统开发工具,可实现基于Nios II软核[3]或ARM 硬核处理器的嵌入式系统开发。Altera SoC EDS包含了开发(debug)工具、实现应用工具程序、运行软件等,可以实现基于Altera SoC硬件平台的应用软件开发。

1.2 系统总体设计方案

基于Altera 片上系统FPGA的图像采集系统[4]主要由208C监控摄像头、Altera公司SoC FPGA Cyclone V系列芯片、SDRAM存储器和硬核处理器(HPS)以及处理器工作所需的外部存储器(包括DDR3 SDRAM和SD卡)构成,其总体设计方案如图1所示。其中,SoC FPGA芯片是整个系统的控制核心,主要功能是:内部的硬核ARM处理器通过H2F_LW_AXI总线和F2H_AXI总线控制Qsys硬件系统内部的视屏解码器、VIP套装视屏处理核,核收到处理器相关寄存器指令后控制FPGA内部的HDL逻辑代码工作,包括图像捕获和停止、图像的串转并(Color Plane Sequence)、图像的去隔行(Deinterlacer)、图像的重采样(Chroma Resampler)、图像的存储和提取。整个采集系统的设计包括Qsys硬件系统设计和硬件处理器系统(HPS)的软件设计。

图1 系统总体设计框架

2 系统FPGA实现

2.1 硬件平台简介

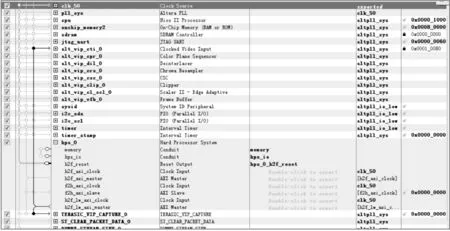

图2 Qsys系统总体硬件配置

本设计采用的硬件平台是Altera公司的基于SoC FPGA进行嵌入式软硬件协同设计系统开发的DE1-SoC开发板。DE1-SoC开发板采用的是Altera公司开发的基于ARM的用户可定制芯片系统Cyclone V SoC[5]FPGA芯片,该芯片集成了硬核处理器(HPS)、FPGA[6]和数字信号处理(DSP)[7-8]功能。HPS是基于ARM Cortex-A9的双核处理器,具有丰富的外设和存储器接口(DDR2/3)等。两者能够相互独立工作,也可以通过高性能的AXI总线桥接实现高速宽带的数据通信,HPS总线通过HPS至FPGA桥接访问FPGA架构中的总线机器外设,同时,FPGA总线也能通过FPGA至HPS桥接访问FPGA架构中的总线机器外设,可让使用者在该平台上实现具有更佳性能和灵活性的FPGA系统设计。

208C监控摄像头具有30万像素的图像传感器,该传感器具有640×480有效像素,支持RGB格式的图像数据输出,支持图像抓拍模式,并且可通过Qsys里的I2C[9]总线模块完成其内部寄存器的参数设置,以实现视频解码,操作简单,而且成本低。

2.2 硬件设计

基于Altera公司SoC FPGA的嵌入式系统硬件设计,首先要基于Qsys规划系统所需要的外设,包括HPS和FPGA各自的接口。HPS外设只需要根据DE1-SoC硬件属性进行设定即可,FPGA的外设首先通过IP模块的方式添加,然后建立各个模块间的连接(包括时钟、复位、总线),最后产生硬件与软件开发各自所需的档案。硬件开发和传统的FPGA设计流程相同,首先使用Quartus II加入Qsys以及用户逻辑,然后设定引脚分配,最后编译产生xx.sof文件。

基于SoC FPGA的图像采集系统的硬件流程如下:

① 在Quartus II软件下启动Qsys设计工具,并添加相应的系统外设,包括HPS硬核处理器、时钟锁相环、I2C、On-chip memory、VIP套装视屏处理核(Clocked Video Input、Color Plane Sequence、Deinterlacer、Chroma Resampler、CSC、Clipper、Frame Buffer)、视频图像捕获(VIP_Capture、Clear_Packet_Data、Dummy_Stream_Sink)、定时器、CPU、系统ID IP核。

② 建立系统各个模块之间的连接,包括时钟、复位、HPS、CPU控制总线,以及各模块之间的输入输出。Qsys下的总体硬件配置如图2所示。

③ 产生Qsys硬件配置系统文件,并键入到Quartus工程中进行编译。

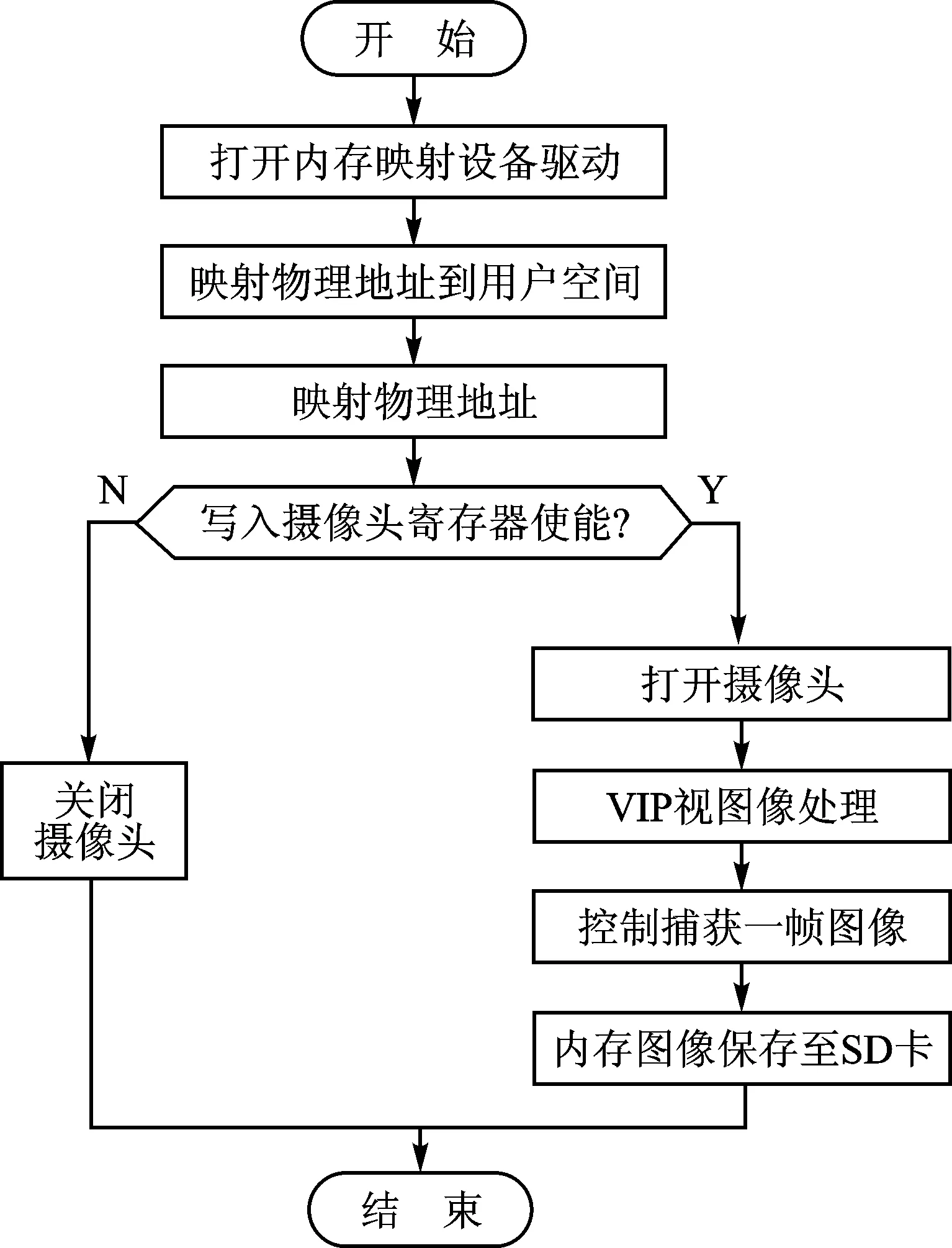

2.3 软件设计

嵌入式系统软件设计主要是基于C语言的SoC EDS软件设计。该设计通过操作相应寄存器控制监控摄像头的捕捉与停止、图像格式的转换以及图像数据的读取和存储。主要实现以下3个功能:一是控制打开监控摄像头,并完成视频解码、图像格式转换、缓存;二是控制VIP_Capture的工作并获取具体状态;三是等待VIP_Capture完成数据传输后,从内存中读取出来并存储为bmp格式的图片。具体软件程序开发流程如图3所示。

图3 嵌入式系统软件程序流程图

具体操作实现代码如下:

fd = open( "/dev/mem",(O_RDWR|O_SYNC ) ) )==-1) //打开内存映射设备驱动

lw_axi_virtual_base = mmap(NULL, HW_REGS_SPAN, (PROT_READ|PROT_WRITE), MAP_SHARED, fd, HW_REGS_BASE); //物理地址映射到Linux上的虚拟地址

m_vip_cti_base=lw_axi_virtual_base + ((unsigned long)(ALT_LWFPGASLVS_OFST+FPGA_VIP_CTI_BASE)&(unsigned long)( HW_REGS_MASK));//摄像头寄存器控制地址

h2p_vip_capture_addr= lw_axi_virtual_base+((unsigned long )(ALT_LWFPGASLVS_OFST + ALT_VIP_CAPTURE_BASE)&(unsigned long)( HW_REGS_MASK));//捕获帧地址

3 结果验证与分析

图4 程序运行终端

最后,对已开发系统进行板级测试。首先给DE1-SoC开发板上电,将编译好的整个硬件系统目标程序(XX.sof))文件烧录到FPGA的配置芯片,将AV监控摄像头插入到开发板的Video-in接口,同时启动将存放有可带Linux操作系统的SD卡。系统启动完成后,打开调试电脑中的终端,在终端输入命令,运行脚本文件./test.h。如图4所示,首先加载内核模块文件并创建文件节点,然后会显示捕获状态,并打印出所得图片的大小。系统运行结束后,读卡器打开SD卡,查看监控摄像头捕捉到的一帧图像。经验证,SD卡保存的示例图片如图5所示,可见该系统实现了图像的捕捉功能。

图5 捕捉示例图

结 语

[1] 谭会生.EDA技术及应用[M].西安:西安电子科技大学出版社,2011.

[2] 陈新泽,杨斌.ARM Cortox-A9的NEON技术研究及应用[J].单片机与嵌入式系统应用,2013,13(10):46-49.

[3] 龚向东,刘春平,黄虹斌,等.一种基于Nios软核的嵌入式图像采集处理系统设计[J].电子测量技术,2010(2):75-49.

[4] 王德胜,康令州.基于FPGA的实时图像采集与预处理[J].电视技术, 2011, 35(3): 32-35.

[5] 杨定定,施慧彬.基于AXI总线的MicroBlaze双核SoPC系统设计[J].电子产品世界,2012,19(1):92-94.

[6] 陈木.浅谈FPGA技术的优势及其应用[J].电子世界, 2015(13):199-200.

[7] 杨波.DSP技术的发展及应用[J].城市建设理论研究, 2014(13).

[8] 沈戈,高德远,樊晓桠.数字信号处理器(DSP)结构设计及发展趋势[J].计算机工程与应用,2003,39(7):4-6.

[9] 王水鱼,王欣.基于FPGA实现OmniVision图像传感器的SCCB总线协议[J].微型机与应用,2015(20):31-32,35.

邓海涛(硕士),研究方向为嵌入式软硬件协同设计;吴捷(学士),研究方向为图像处理与模式识别;李建辉(学士),研究方向为数字信号处理与识别;陈耀文(教授),研究方向为医学信号处理。

Image Acquisition System Based on DE1-SoC Platform

Deng Haitao1,Wu Jie1,Li Jianhui2,Pan Guocheng1,Chen Yaowen1

(1.Engineering College,Shantou Universtity,Shantou 515063,China;2.Shantou Huashan Electronic Devices Co.,Ltd.)

In the paper,the embedded system design method based on Altera’s SoC FPGA is introduced,including the system hardware design based on Qsys and embedded software design based on SoC EDS development suite.The soc_training image kernel image file is used to write to the external SD card,then the Linux operating system is started.The required hardware module is added in Qsys and the application software is added in EDS development kit platform. Finally,the system function is realized through the board level verification.The system realizes the function of image capture by FPGA Video-in interface,and deposited it in the SD card.

embedded design;FPGA;hard-core processor;image acquisition

汕头市科技计划项目(A201400150);汕头大学学术创新团队项目(ITC12002)。

TP391.4

A

�迪娜

2016-07-20)