KeyStone架构的多核DSP中断路由机制及其实现方法

2017-02-09沙海珍魏利卓

沙海珍,魏利卓

(1.重庆邮电大学 通信与信息工程学院,重庆 400065;2.中国电子信息产业集团有限公司第六研究所)

沙海珍1,魏利卓2

(1.重庆邮电大学 通信与信息工程学院,重庆 400065;2.中国电子信息产业集团有限公司第六研究所)

在KeyStone多核DSP应用系统中,中断的使用是不可或缺的一部分,处理中断的能力也是衡量一个芯片性能的重要因素之一。本文以TI公司推出的高性能TMS320C6670四核DSP为基础,讲述了基于KeyStone架构的多核DSP的中断路由机制,并以TMS320C6670集成的SRIO高速接口的LSU中断和DOORBELL中断为例,通过调用TMS320C6670的SYS/BIOS提供的CSL库函数,分别给出了两者的实现方法。

DSP;中断;TMS320C6670;SRIO

引 言

TI公司推出的TMS320C6670(以下简称C6670)四核DSP采用先进的KeyStone多内核架构,集成了HyperLink、PCIe、SRIO以及其他外设,可实现内核与存储器存取的直接通信,能够充分发挥多内核性能。它在电源方面采用TI Green Power技术,使其具有很好的电源效率。此外,C6670在计算方面采用定点+浮点架构,支持将浮点算法方便地移植到多核平台上[1]。基于以上这些优点,C6670在数字控制领域已经有着非常广泛的应用,成为电子工业领域不可替代的高性能产品。

中断处理是一个芯片必须具备的能力,尤其在DSP系统中是必不可少的重要环节,它对输入输出处理、多道程序和分时操作、实时处理和人机交互等方面都起着重要的作用。中断由外设请求和CPU响应两个过程组成。首先,某一外设向CPU发出请求信号,请求CPU暂停当前程序而去处理中断服务子程序ISR。其次,当CPU接收到这个请求信号后,便对当前执行的主程序进行现场标记并暂停其运行,自动转移到请求设备的中断服务子程序中去。当中断服务程序结束后,CPU就回到之前标记的主程序之处继续执行。

1 KeyStone多核DSP的中断系统架构

C6670的中断控制系统由两部分组成:芯片中断处理控制器(Chip Interrupt Controller,CIC)和核中断控制器(Interrupt Controller,INTC),架构图略——编者注。外部设备产生的中断由CIC和INTC共同作用,以实现CPU响应中断的目的。其中,CIC位于内核外部,主要负责将外部中断映射到CorePac、EDMA和HyperLink内部的主机中断信号。CorePac中断控制器则位于核内部,负责将主机中断信号转为CPU可处理的12个可屏蔽中断信号。

1.1 CorePac中断路由

在C6670中,EDMA3控制器以及4个CorePac都可以直接接收中断,但是无论是CorePac还是EDMA3控制器,其能直接接收的中断输入是有限的。KeyStone CorePac能够直接接收的中断输入为1个可屏蔽的硬件Exception、12个可屏蔽的硬件Interrupt(INT4~INT15)、1个不可屏蔽的NMI信号以及1个复位信号[2]。Exception其实也为Interrupt,区别在于Exception常常伴随的是错误信息的发生。其中Exception、NMI、Reset信号都是芯片保留的中断输入,用户能够自行配置的中断输入实际为12个(INT4~INT15),在这12个可屏蔽中断输入中,INT4的优先级最高,INT15的优先级最低。

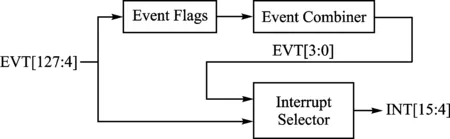

然而,作为一个复杂的DSP芯片,如果其能处理的中断源仅为15个,是远远无法满足复杂程序需求的。所以为了能够处理更多的中断源,KeyStone结构的DSP CorePac内部集成了一个中断控制器INTC,其作用是将更多的中断源(对于KeyStone架构DSP来说,是128个System Event)路由到这12个可屏蔽中断输入中去。

CorePac中集成了Interrupt Selector,使得编程人员可以将这128个System Event中的任何一个路由到INT4~INT15中的任何一个,从而完成事件响应。例如,C6670的第85号System Event为GPINT11事件,如果把第85号事件路由到CorePac的第7个可屏蔽中断输入(INT7),那么当DSP的第11个GPIO引脚的事件发生以后,且当前没有更高优先级的中断发生(比INT7更高优先级的中断),则DSP的CorePac会跳转到中断向量表,进一步去执行中断处理函数。

CorePac的INTC中还集成了一个Event Combiner控制器,起到事件合成的作用。这128个System Event中的第4~127个System Event都是来自芯片内部或者外部的Event,都是有实际物理意义的,而使用Event Combiner则可以将第4~31号System Event中的若干个合成为Event #0,或者将第32~63号System Event中的若干个合成为Event #1,或者将第64~95号System Event中的若干个合成为Event #2,或者将第96~127号System Event中的若干个合成为Event #3。如图1所示,则等效的System Event有128个。

图1 Event Combiner目的图

对于合成的System Event,是“或”的关系。即如果使用了Event Combiner将第7、13、35号System Event合成为Event #0,那么只要7、13、35中的任何一个事件发生,就等效为Event #0事件发生。

整个CorePac中,128个System Event到12个可屏蔽中断(INT4~INT15)的结构框图见图2。

图2 INTC内部中断路由结构图

1.2 CIC中断路由

KeyStone DSP核心CorePac能够处理128个System Event(其中实际有直接物理意义的为124个,Event 0~3为合成的结果,共计128个),绝大部分是芯片内部DMA、QMSS等模块产生的事件,这128个事件仍然无法满足程序的需求。因为DSP芯片诸多外设产生的事件同样需要得到及时地处理,比如SRIO、PCIE等外设,而每个外设产生的事件往往不止一个,比如SRIO事件也分为包发送成功事件、包发送失败事件、Doorbell接收事件等。所以,如果希望在这些大量的外设事件发生后,CorePac能够去执行相应的中断处理函数,那么这些事件也是需要路由到CorePac的12个可屏蔽中断输入(INT4~INT15)中去的。但是,这些外设事件是不能够像128个System Event那样直接路由到INT4~INT15中去的[3]。而CIC在外设事件到CorePac之间的路由起到了桥梁的作用。需要注意的是,CIC/Cpintc不是CorePac的INTC,其是在CorePac外部的,CorePac的INTC是在CorePac内部的。

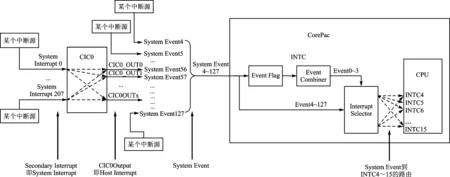

由图1可知,C6670内部有3个CIC,即CIC0~CIC2。其中CIC0负责外设事件到CorePac的路由,CIC1~CIC2负责外设事件到EDMA3或者HyperLink控制器之间的路由。这里只讨论CIC0的功能,而CIC1~CIC2的路由机制一致,与CIC0的区别仅仅为目的地不同。

CIC0的输入称为System Interrupt,输出为CIC0_OUTx(称为Host Interrupt)。CIC0能够接收的System Interrupt有208个,CIC0的目的即为把这208个System Interrupt路由到其CIC0_OUTx去。如果若干个System Interrupt通过CIC0路由到了某一个Host Interrupt,那么这若干个System Interrupt为“或”的关系。而Host Interrupt与CorePac的 INTC的System Event是一一对应的。例如,Host Interrupt中的CIC0_OUT0对应的是System Event 56,或者CIC0_OUT(64+0+10×n)对应的是System Event22,其中n为核号。

2 KeyStone DSP中断路由路径

总的来说,KeyStone DSP中断路由路径有两种,如图3所示。第一,System Event经过Event Combiner后,再通过Interrupt Selector路由到INTCx,或者System Event不经过Event Combiner,直接通过Interrupt Selector路由到INTCx。第二,System Interrupt经过CIC0路由到某个Host Interrupt,而Host Interrupt是对应到System Event的,之后再将该System Event经过Event Combiner、Inter-

rupt Selector路由到INTCx,或者直接将该System Event经过Interrupt Selector路由到INTCx。

Primary Interrput直接对应于某个System Event。例如GPINT4对应System Event #78,输入CorePac INT。用户可以选择是否经过Event Combiner,如果经过Event Combiner,则合成为Event2,再经过Interrupt Selector路由到INTCx;如果不经过Event Combiner,则直接将System Event #78经过Interrupt selector路由到INTCx。

Secondary Interrupt也称为System Interrupt,先经过CIC0路由到CIC0的某个输出(Host Interrupt),比如可以将CIC0的第122号输入INTDST10,经过CIC0路由到CIC0_OUT7。而每个Host Interrupt是直接对应某个System Event的,例如CIC0_OUT7对应的是System Event #63。如果经过Event Combiner,则合成为Event1,再经过Interrupt Selector路由到INTCx;如果不经过Event Combiner,则直接将System Event #63路由到INTCx。

图3 System Interrupt到INTCx的路由路径

3 KeyStone DSP的SRIO中断

SRIO模块能够输出若干种不同的中断,这些中断属于System Interrupt。如果当SRIO中断到来后,想让DSP及时地去处理相应的中断函数,则需要将该中断经过某个路径路由到INTCx中去。

SRIO的主要中断有两种:一种为包发送中断,该中断可以通知DSP,SRIO模块已经发送了一个协议包;另一种为Doorbell中断,为SRIO模块接收远程器件发送来的Doorbell包,并做相应的处理。其中, SRIO模块中的LSU寄存器负责的是DIO协议包的发送,则DIO协议包的发送中断可以称为LSU中断[4]。无论是LSU中断还是Doorbell中断,都是SRIO内部的Peripheral Interrupt,需要路由到System Interrupt。System Interrupt是从SRIO外设输出到CIC0输入端口的信号。

KeyStone DSP的SRIO模块共有24个System Interrupt,称为INTDST0~23。其中INTDST0~15为通用System Interrupt,可以连接LSU或者Doorbell Peripheral Interrupt,再输入到CIC0;而INTDST16~INTDST23只连接Doorbell Peripheral Interrupt,且为System Event,是直接输入到CorePac的。

3.1 SRIO LSU中断路径的实现

SRIO模块内部会产生40个LSU中断,其中有32个中断由寄存器LSU0_ICSR控制,另外8个由寄存器LSU1_ICSR控制。这里以寄存器LSU0_ICSR的最低位ICS0代表的SRCID0 Transaction Complete without errors中断信号为例,说明LSU中断路由的实现,路由路径如图4所示。首先将LSU产生的“SRCID0 Transaction Complete without errors”路由到INTDST1,然后将INTDST1对应的中断处理函数myDioTxCompletionIsr插入到CpIntc_dispatch表中,接着在CIC0内部,将INTDST1路由到Host Interrupt #8,获取Host Interrupt #8对应的System Event ID,此处为74,将System Event #74经过Event Combiner送入Interrupt Selector,并将CpIntc_dispatch

插入到EventCombiner_dispatch中去。在程序的SYS/BIOS cfg文件loopbackDioIsr.cfg中,定义了以下代码:

ECM.eventGroupHwiNum[0] = 7;

ECM.eventGroupHwiNum[1] = 8;

ECM.eventGroupHwiNum[2] = 9;

ECM.eventGroupHwiNum[3] = 10;

即可将System Event #2路由到INTC9。

图4 LSU中断路由路径

如此,则当“SRCID0 Transaction Complete without errors”发生时,CPU能够响应。首先去处理EventCombiner_dispatch表,而CpIntc_dispatch表已经插入了Event Combiner_dispacth表,则接着去处理CpIntc_dispatch表。而中断处理函数myDioTxCompletionIsr插入到了CpIntc_dispatch表,则myDioTxCompletionIsr就会被执行。

3.2 SRIO Doorbell中断路径的实现

根据RapidIO协议可知,Doorbell包中携带16位的Doorbell Info。对于协议本身来说,这16位数据是没有含义的,而对于KeyStone DSP来说,这16位的Doorbell Info即为Doorbell中断源。

KeyStone DSP定义了Doorbell Info的第0~3位代表位信息,第5~6位代表Reg信息,其他位为保留位,无含义。例如,如果KeyStone DSP接收到的Doorbell中Info Field为0b 0000 0000 0100 1010,即表示Reg=2且Bit=10中断,对应的是Doorbell[2]_ICSR.ICS10标志位被置1。也就是说,如果Doorbell[n]_ICSR.ICSx位被硬件置1,则表明接收到的Doorbell Info[3:0]=x,doorbell Info[6:5]=n。KeyStone SRIO模块能够产生的Peripheral Interrupt共4×16=64种,每种对应一个特定的Doorbell Info值。

如前所述,Peripheral Interrupt是需要路由到System Interrupt(INTDST0~INTDST23)上去的。而寄存器Doorbelln_ICRR和Doorbelln_ICRR2定义了Reg=n且Bit=x的Doorbell Info Peripheral Interrupt被路由到INTDSTy上去。

一旦能够将某个特定的Doorbell Info路由到某个INTDSTy上之后,剩下的步骤就是将INTDSTy再经过某个路径路由到INTCz上去,就能实现当DSP接收到该Doorbell Info时,中断能够被处理。

KeyStone SRIO模块的Doorbell中断的路由路径有4种,分别为经过CIC0和Event Combiner、经过CIC0但不经过Event Combiner、不经过CIC0但经过Event Combiner、不经过CIC0和Event Combiner。

下面说明Doorbell不经过CIC0和Event Combiner实现中断的路由路径,如图5所示。

首先,将Reg=0且Bit=任意的Doorbell Info中断路由到INTDST16。部分代码如下:

CSL_SRIO_SetDoorbellRoute(hSrio, 0);

for (i = 0; i < 16; i++){

CSL_SRIO_RouteDoorbellInterrupts(hSrio, 0, i, 0);

CSL_SRIO_RouteDoorbellInterrupts(hSrio, 1, i, 1);

CSL_SRIO_RouteDoorbellInterrupts(hSrio, 2, i, 2);

CSL_SRIO_RouteDoorbellInterrupts(hSrio, 3, i, 3);

}

然后,直接将INTDST16对应的System Event #20直接路由到INTC7上,关键代码如下:

Hwi_Params hwiParams;

Hwi_Handle myHwi;

Error_Block eb;

Hwi_Params_init(&hwiParams);

Error_init(&eb);

hwiParams.arg = (UArg)hDrvManagedSrioDrv;

hwiParams.eventId = 20;

myHwi = Hwi_create(7, (CpIntc_FuncPtr)myDoorbellCompletionIsr, &hwiParams, &eb);

结 语

本文以四核DSP TMS320C6670为例,详细地介绍了基于KeyStone架构的多核DSP的中断系统的组成、中断的路由机制及其不同的实现方法,并简要介绍了其高速串行接口SRIO的两种中断:LSU中断和Doorbll中断的路由路径。本文软件程序设计没有采用直接对寄存器进行操作,而是借助SYS/BIOS平台中硬件中断Hwi的创建来进行中断的实现,通过调用CSL的库函数,省去了直接对寄存器操作的繁杂过程,在很大程度上提高了编码的效率及正确性。

[1] 牛金海.TMS320C66x KeyStone架构多核DSP入门与实例精解[M].上海:上海交通大学出版社,2014:58-62.

[2] Texas Instruments.TMS320C66x CorePac User's Guide,2013.

[3] Texas Instrument.Keystone Architecture Chip Interrupt Controller(CIC) User's Guide,2012.

[4] 吴文德.基于TI6678平台的SYS/BIOS应用技术研究[D].北京:中国科学院大学,2015.

[5] Texas Instrument.Multicore Programming Guide Multicore Programming and Applications/DSP Systems,2012.

[6] Texas Instruments.TMS320C66x DSP CPU and Instruction Set Reference Guide,2010.

沙海珍(硕士研究生),主要研究方向为宽带无线移动互联网络;魏利卓(硕士研究生),主要研究方向为嵌入式软件开发。

图8 文件上传结果

结 语

参考文献

[1] 汪小燕,连晓平,董燕,等.基于TFTP协议的嵌入式系统开发方法设计与实现[J].华中科技大学学报:自然科学版,2006,34(12):56-58.

[2] 熊传玉,徐尤华.Android系统下基于JSON的天气预报应用的实现[J].微型电脑应用,2016,32(1):8-10.

[3] 谢永悠.简单文件传送协议(TFTP)的C语言实现[J].电子元器件应用,2010,12(3):55-58.

[4] 沈炜,王晓聪.基于Qt的嵌入式图形界面的研究和应用[J].工业控制计算机,2016,29(1):101-104.

柯玉山(硕士研究生),主要研究方向嵌入式系统应用、无线传感器网络;陈阿辉(硕士研究生),主要研究方向为雷达测距系统;邱菁(硕士研究生),主要研究方向为雷达测距算法。

(责任编辑:薛士然 收稿日期:2016-08-05)

Sha Haizhen1,Wei Lizhuo2

(1.Communication and Information Engineering,Chongqing University of Posts and Telecommunications,Chongqing 400065,China;2.China Institute of Electronic Information Industry Group Co.,Ltd.6)

In the system of KeyStone multi-core DSP’s application,the use of interrupts is an indispensable section,and the ability to handle the interrupt is an important factor of measuring the performance of a chip.In the paper,based on the TMS320C6670 with four cores, the routing path of interrupts on KeyStone multi-core DSP is introduced in detail.Taking the high-speed interface SRIO’s LSU interrupt and DOORBELL interrupt as the example,the realization methods are given respectively through calling CSL library functions provided by SYS/BIOS of TMS320C6670.

DSP;interrupt;TMS320C6670;SRIO

TP601

A

�士然

2016-08-09)