一种基于嵌入式磁旋存储芯片的固态硬盘控制器芯片架构

2017-01-19李炜

李 炜

(中电海康集团有限公司,浙江 杭州 311121)

一种基于嵌入式磁旋存储芯片的固态硬盘控制器芯片架构

李 炜

(中电海康集团有限公司,浙江 杭州 311121)

传统企业级固态硬盘存储芯片采用外接DRAM(Dynamic Random Access Memory)颗粒的方式来存储闪存地址转换映射表,不仅成本高,占用面积大,还需要设计复杂的掉电保护流程和额外的备电保持电容。利用新型磁旋存储芯片的掉电非易失特性,以及密度高、速度快、功耗低、数据保持时间长、可擦写次数无限等特点,提出了一种基于嵌入式磁旋存储芯片的固态硬盘控制器架构方案,能够大大简化控制器芯片的掉电异常流程和备电设计,节省固态硬盘内部的备电电容成本,有效支撑固态硬盘的容量提升。

磁旋存储芯片;固态硬盘;芯片架构;嵌入式

0 引言

随着大数据和云计算的发展,大量的数据需要进行存储,另一方面,随着NAND闪存(NAND Flash)工艺的进步和良率的提升,固态硬盘(Solid State Disk,SSD)的成本已经下降至接近企业级机械硬盘(Hard Disk Drive)相当的水平,SSD在服务器、数据中心以及存储系统中的应用越来越广泛。

传统的企业级SSD控制器大多采用基于DRAM方案的数据和表项存储方案,不仅设计难度大,掉电异常流程复杂,而且在SSD盘内需要占用大量的空间用来摆放备电钽电容,既增加了成本又制约了盘内利用空间,无法做到SSD的容量提升。

本文将嵌入式磁旋存储芯片(Spin-Transfer-Torque Magnetic Random Access Memory, STT-MRAM)应用于SSD控制器芯片架构设计中,能够简化掉电异常流程,节省SSD盘内备电电容,并可以提升硬盘容量达30%以上。

1 当前固态硬盘控制器架构方案简介

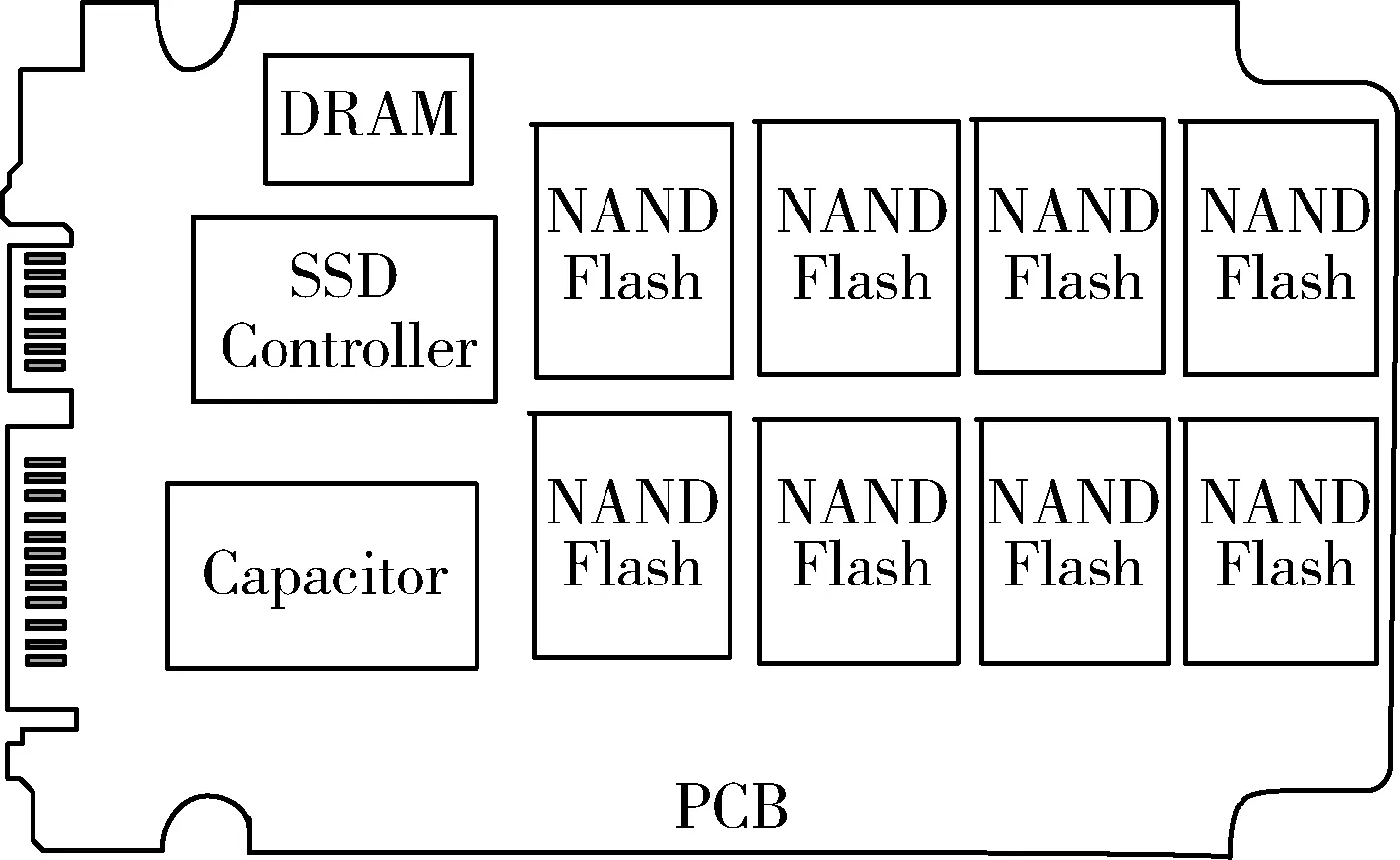

图1为当前主流企业级固态硬盘架构方案示意图。

图1 主流SSD控制器芯片架构图

当前的固态硬盘控制器芯片分为前端主机接口模块、系统管理模块、后端Flash接口模块几个主要的部分。

前端主机接口模块主要负责接收和处理主机侧下发的读写命令并将数据接收下来存到DRAM中。企业级SSD中,由于对性能要求高,前端主机接口基本上选用基于NVMe(Non-Volatile Memory Express)协议的第三代PCIe(PCI Express)的接口,除此之外,SAS(Serial Attached SCSI)12 G和SATA(Serial ATA)接口也是当前SSD前端主机接口的主流协议。

系统管理模块是SSD控制器芯片的最核心单元,包括闪存地址映射表(Flash Translate Layer,FTL)管理、元数据管理、日志管理、流程控制等。其中FTL表项管理是其中最重要的部分。

FTL主要处理主机下发的逻辑地址(Logic Block Address,LBA)到介质颗粒里存储的物理地址(Physical Block Address, PBA)之间的映射表,是让闪存完全模拟传统硬盘操作的软件层,有了FTL层闪存设备才能使用,FTL层的效率直接影响设备的性能表现。

系统管理模块的作用主要包括下面几点:FTL表项管理;垃圾回收的处理;增量空间的供给;冷/热数据的交换处理;Plane、芯片、通道间的并行处理;任务请求的排序;缓冲区的管理;坏块的管理;磨损平衡的处理;掉电恢复的处理;ECC的处理。

NAND Flash Interface主要负责处理NAND Flash颗粒的数据与命令交换。NFI负责把主机侧的读写命令转化成兼容ONFI和Toggle的标准NAND接口协议,并在NAND颗粒与控制器数据缓存之间做数据的读写交互。

在SSD盘片的PCB板上,除了控制器芯片和大量的NAND Flash颗粒之外,还包括下列几个主要组成部分:

(1)外挂DRAM颗粒在SSD盘片的作用主要有两个方面:作为读写数据的缓存及存取FTL映射表。为了满足此设计需求,控制器芯片设计中为了适配DDR协议,需要开发DDR Controller与DDR PHY进行适配,PCB上还要预留额外空间进行DRAM颗粒的排布以及高速信号布局布线。

(2)Electrical Capacity(备电电容)的作用是为了在意外掉电的情况下,能够及时地把DRAM颗粒中存储的FTL表项在备电电容电量的支撑下,安全及时地下刷至非易失性介质(NAND Flash),防止FTL表项丢失引发的数据丢失情况。

传统SSD控制器芯片架构的不足在于以下几点:

(1)由于企业级业内常用的方案是用外接DRAM颗粒来存储FTL表项,因此在芯片内部需要额外的DDRPHY和DDR 控制器进行适配,开发DDR控制器和DDR PHY的难度相当大,而从EDA vendor处进行IP 授权的费用又相当昂贵,因此会增大设计开发成本。

(2)盘片内部空间限制,如图2所示为标准2.5英寸SSD的印制电路板(PCB)示意图。从国内某著名公司生产的企业级SSD盘片剖解可以看出,SSD硬盘的PCB板大约80%的空间是布满了闪存介质颗粒,另外20%的空间摆放SSD控制器芯片、DRAM颗粒及备电电容等。

图2 SSD盘片内部示意图

(3)企业级SSD对于数据可靠性的要求极高,其设计时必须考虑在各种异常情况下(如异常掉电)能够把控制器内部的最核心内容—FTL表安全可靠地存储到非易失性介质中。在常规企业级SSD控制器芯片架构中,DRAM内部存储着FTL表项,因此在遭遇掉电异常时,需要把DRAM内部的FTL表下刷至NAND Flash中。简而言之,就是要在备电电容支撑电量的这一小段时间内,控制器能够将FTL表项的数据以写操作的形式存储到NAND Flash中。因此在备电设计上,一是需要消耗数量巨大的贴片式钽电容来提供备电能量,导致PCB上的可用空间会进一步缩小,二是备电涉及到数据的异常处理流程,会提高硬件以及固件设计的复杂度。

2 磁旋存储芯片(STT-MRAM)的特点

在众多新型非易失性存储介质中,磁旋存储芯片(STT-MRAM)能够良好地与CMOS半导体工艺相兼容,利用较少的金属层即可以做到存储单元的高密度集成。同时由于其接近于静态随机存储器(Static Random Access Memory, SRAM)的读写速度,极低的静态和动态功耗,具备掉电不易失的特性,接近于无限的擦写次数,高温下长时间的数据保持能力以及抗强磁场辐射等特性,是作为企业级SSD控制器中数据缓存和FTL表项存储的天生优良介质[1]。

当前,众多半导体设计大厂都将MRAM芯片作为下一代非易失性存储介质的研发重点,除了台积电、三星和东芝一直在持续推进STT-MRAM的研发之外,美国的EVERSPIN公司已经发布了256 MB的量产测试芯片。随着工艺的进步和良率的提升,STT-MRAM在存储细分领域中的应用将会越来越广泛[2]。

将嵌入式STT-MRAM应用在SSD控制器芯片架构设计中,充分利用其掉电不易失数据的特性,能够节省大量的备电设计和备电流程,极大地简化SSD的控制器架构设计。另外,由于节省了贴片式钽电容,在PCB板上能够留取更大的空间来支撑更多的NAND Flash颗粒的放置,达成更大的容量。除此之外,简化了控制器芯片内部的DDR接口相关IP设计,利用嵌入式STT-MRAM的内部总线接口(SRAM-like),既简化了设计难度又能够减少板上走线的信号延时,避免对接口高速信号的影响。

3 基于嵌入式磁旋存储的SSD控制器架构方案

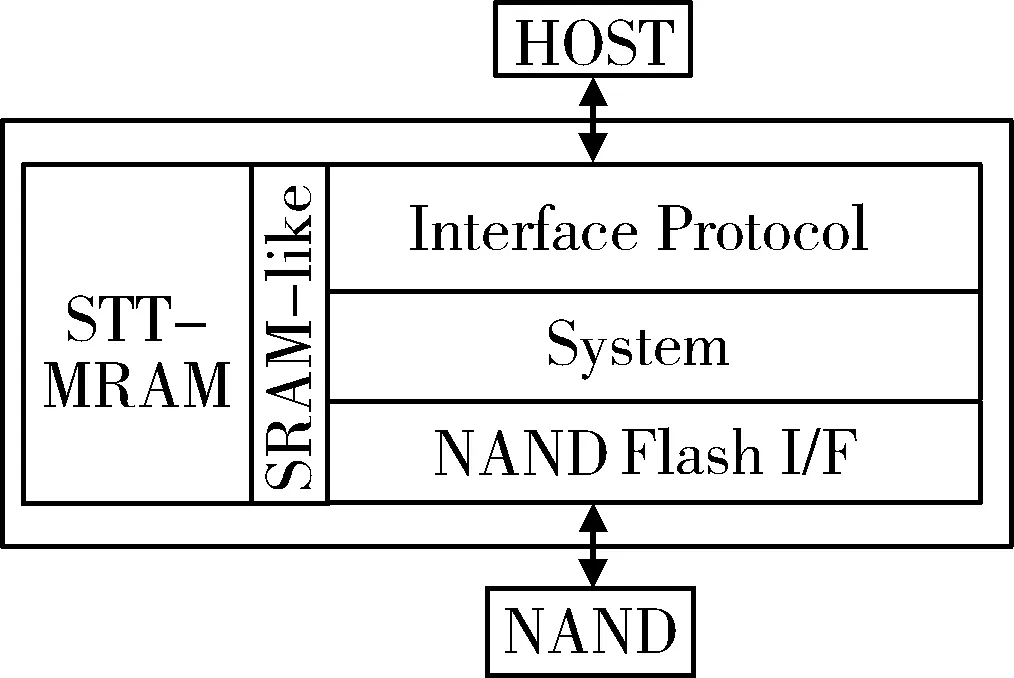

图3为应用嵌入式STT-MRAM之后的SSD控制器芯片架构示意图。

图3 基于嵌入式STT-MRAM的SSD控制器芯片架构图

本方案的技术特征在于:

(1)移除SSD控制器芯片内部的DDR控制器和DDR PHY,直接以类SRAM(SRAM-like)的接口形式将嵌入式STT-MRAM集成在控制器芯片内部。

SRAM-like的总线接口信号包括片选CS、写使能WE、读使能RE、输出使能信号OE、复位RST、时钟CLK、地址线A[31:0]、数据输入线DIN[31:0]及数据输出线DOUT[31:0]。采用内部总线接口与控制器内部模块进行交互,能够极大地减少信号线传输延时以及外部接口协议带来的额外开销,进一步提升控制器的性能。

(2)STT-MRAM的主要作用在于:接收前端主机接口下发的数据,作为与后端Flash接口的数据缓存;存储闪存地址转换层表项;存储元数据,如有效页个数、坏块管理信息、固件、启动代码、稀疏校验矩阵等。

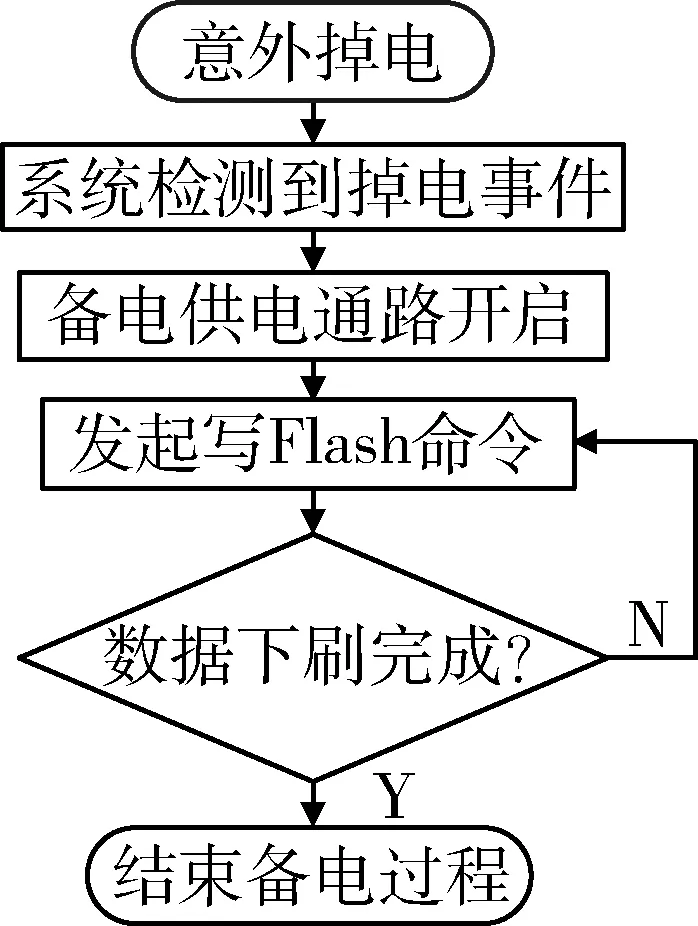

(3)备电流程的简化。在传统的SSD控制器芯片架构中,由于数据以及FTL表项都是存储在DRAM中,而DRAM具有掉电易失数据的特性,因此为保证数据可靠性,在遭遇到异常掉电的情形下,传统控制器芯片需要在板上备电电容的电量支撑下,主动发起Flash的写操作,将需要保存的重要信息全部下刷到非易失的闪存中,当下一次上电后,控制器需要发起读操作再将FTL表项等数据重新读取到DRAM中,完成系统的初始化。图4为SSD异常掉电流程图。

在本架构方案中,由于嵌入式STT-MRAM的掉电非易失特性,在遭遇到掉电异常时,数据和FTL表项依然可以安全地进行存储,因此系统备电流程将会被极大地简化。盘片内部用来做备电的钽电容也能够去除,节省盘片内部的硬件设计成本。根据一款900 GB的SAS接口的企业级SSD盘片的解剖分析可以看到, 为了满足备电需求,盘片PCB上一共放置了共400多个钽电容。如果采用本架构方案,能够将这些额外的钽电容全部移除,一方面节省了硬件元器件成本,另一方面利用钽电容移除的PCB面积来贴NAND Flash颗粒,至少能够使SSD盘容量提升20%。

图4 SSD异常掉电流程图

4 结论

本文提出的基于嵌入式STT-MRAM的固态硬盘控制器架构,能够极大地简化控制器内关于FTL表项的备电流程,简化盘片内的PCB设计难度和成本,在提升SSD读写性能的同时能够有效支撑SSD做到更大的容量。随着STT-MRAM的工艺技术进步和良率的提升,磁旋存储芯片必将在更多的存储细分领域中得到广泛的应用。

[1] TANG D D, LEE Y J. Magnetic memory fundamentals and technology[M]. England: Cambridge University Press,2010.

[2] Xie Yuan. Emerging memory technologies: design, architecture, and applications[M]. Germany: Springer, 2014.

A SSD controller architecture based on embedded STT-MRAM

Li Wei

(China Electronics Technology HIK Group Co., Ltd., Hangzhou 311121, China)

Traditional enterprise Solid-State Disk (SSD) memory chip uses external Dynamic-Random-Access-Memory (DRAM) to store the flash address translate layer mapping table (FTL), this method is high cost, big area occupied, also needs complex power-loss protection flow and extra power backup capacitor. By using new non-volatile memory (NVM) like Spin-Transfer-Torque Magnetic Random Access Memory (STT-MRAM), it has a lot of benefits suck as non-volatile, high density, high speed, low power, long data retention time and unlimited program/erase cycle, proposed a new SSD controller architecture by using embedded STT-MRAM. This proposal can greatly simplify the controller power-loss protection flow and power backup design, save the power capacitor cost inside SSD, also can support the SSD big capacity requirement.Key words: STT-MRAM; Solid State Disk (SSD); architecture; embedded

TN492

A

10.19358/j.issn.1674- 7720.2017.01.009

李炜. 一种基于嵌入式磁旋存储芯片的固态硬盘控制器芯片架构[J].微型机与应用,2017,36(1):29-31.

2016-08-03)

李炜(1981-),男,硕士,工程师,主要研究方向:SoC芯片设计,磁旋存储芯片设计与应用。