视频图像处理系统中SDRAM控制器的FPGA实现

2017-01-19胡辽林刘光飞

胡辽林, 刘光飞

(西安理工大学 机械与精密仪器工程学院,陕西 西安 710048)

视频图像处理系统中SDRAM控制器的FPGA实现

胡辽林, 刘光飞

(西安理工大学 机械与精密仪器工程学院,陕西 西安 710048)

为实现视频图像处理系统中图像数据的实时处理,使用大容量的存储器完成数据缓存是必不可少的一个环节。针对SDRAM的工作原理及时序特性,现提出一种在FPGA芯片上实现SDRAM控制器的方案。根据实时图像数据传输速率的要求,SDRAM的操作模式配置为全页突发读写及自动刷新操作模式,将各个操作进行模块化设计并由一个总状态机控制。整个设计采用Verilog实现。实验结果表明,该控制器在视频图像处理系统中实现了本文所提出的数据高速缓存的功能,并具有读写效率高、控制简单、价格低廉等特点。

SDRAM控制器; 数据缓存; FPGA; 模块化; 状态机

在视频图像处理系统中,图像数据量大且实时性要求高,故需要高速大容量的存储器对图像数据实时缓存[1]。SDRAM相比其他存储器,具有容量大、体积小、读写效率高、价格低等优点,因此在数据处理量大的系统中常被用做数据缓存器[2]。但SDRAM的控制逻辑复杂,时序要求严格,需针对图像处理系统设计一个简单、高效的SDRAM控制器。当前许多处理器及DSP提供了通用的SDRAM控制器,但因为其通用性,运行速度及读写效率都很低。针对该视频图像处理系统,本文提出一种基于FPGA的SDRAM控制器。该控制器配置全页突发读写及自动刷新操作模式[3],并将控制器中各个操作进行模块化设计,再由一个总状态机对所有模块进行控制调用[4]。文中还运用两个异步FIFO进行FPGA及SDRAM之间数据缓冲,实现两者间数据的无缝连接[5]。实验结果表明,采用Verilog硬件描述语言在FPGA芯片上实现的SDRAM控制器能够对视频图像数据进行高效地读写操作,成功实现视频图像数据的缓存。

1 SDRAM的工作原理及简介

本文采用Micron公司的MT48LC32M16A2型号的SDRAM芯片进行测试、调试和仿真,其存储容量为512Mbit(8M×4Banks×16Bit)[6]。

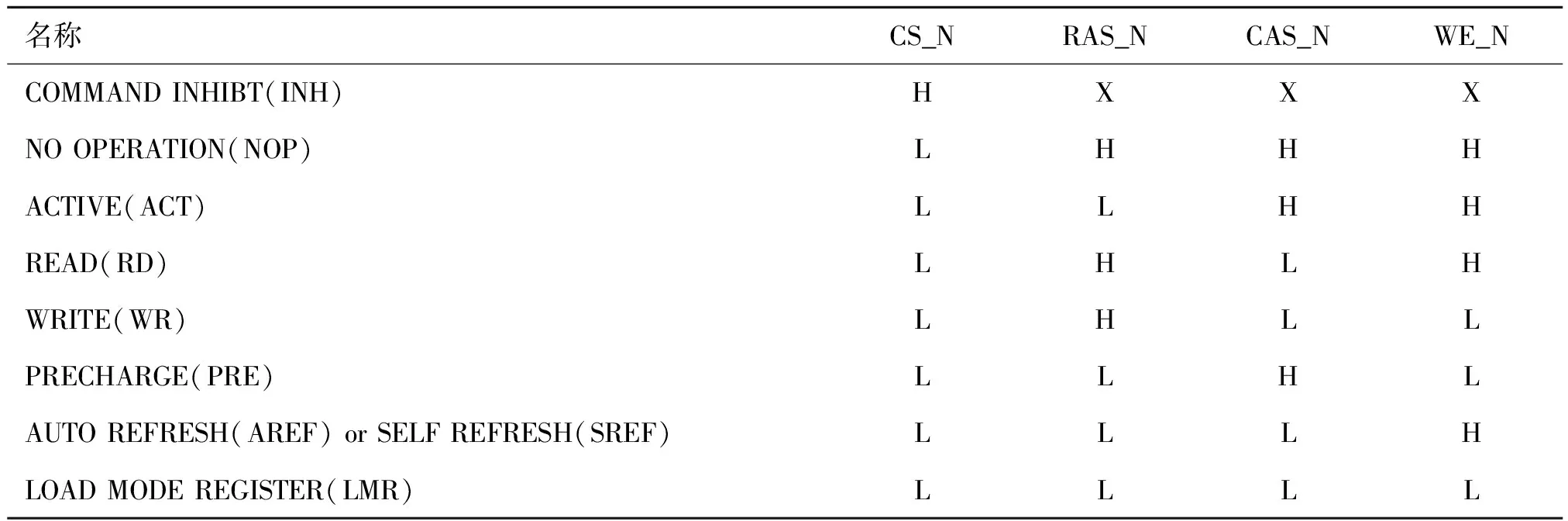

1.1 SDRAM的主要操作命令

SDRAM芯片管脚信号分为三种:控制信号、地址信号、数据信号[7-10]。其中控制信号包括:WE_N(写使能)、CAS_N(列地址有效)、RAS_N(行地址有效)、CS_N(片选);地址信号包括:行列地址(A0~A12)、Bank地址(BA0~BA1);数据信号(DQ0~DQ15)为双向数据信号,其是否有效由输入输出使能信号(DQM0~DQM1)所控制。控制命令的各种逻辑组合可产生各种控制命令,如表1所示,其中H为高电平,L为低电平,X为任意电平[11]。

表1 命令真值表

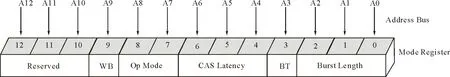

LMR即模式寄存器设置命令是对芯片的读写突发长度(BL)、突发类型(BT)、读取潜伏期(CL)等参数进行设置。

ACT即激活命令是激活一个后续将访问的bank中的一行,BA0~BA1的值为bank地址,地址总线A0~A12提供行地址。这一行的访问直到一个预充电命令在此bank上执行。

PRE即预充电命令是关闭一个bank或所有bank打开的行,A10决定是一个bank还是所有bank被预充电,bank在执行预充电命令经过规定时间之后可供后续访问。

REF即刷新命令是为保持数据有效,刷新分为自动刷新和自刷新,本文中采用自动刷新,这个命令是非持久化的,每次刷新必须在规定时间内执行一次。

WR/RD即读写命令是对一个激活的行进行突发读写操作,读写的数据为DQ总线上的数据,DQM信号决定输入或输出的数据有效,读取时DQM在发出两个时钟周期后有效,写入时则立即生效。

1.2 SDRAM工作流程

SDRAM的主要工作流程可以分为以下三大部分。

1) SDRAM正常工作之前,首先需要上电初始化操作。在SDRAM芯片内部有一个逻辑控制单元,模式寄存器为其提供控制参数,故每次开机时需对其进行初始化,其中最关键步骤就是模式寄存器的配置。

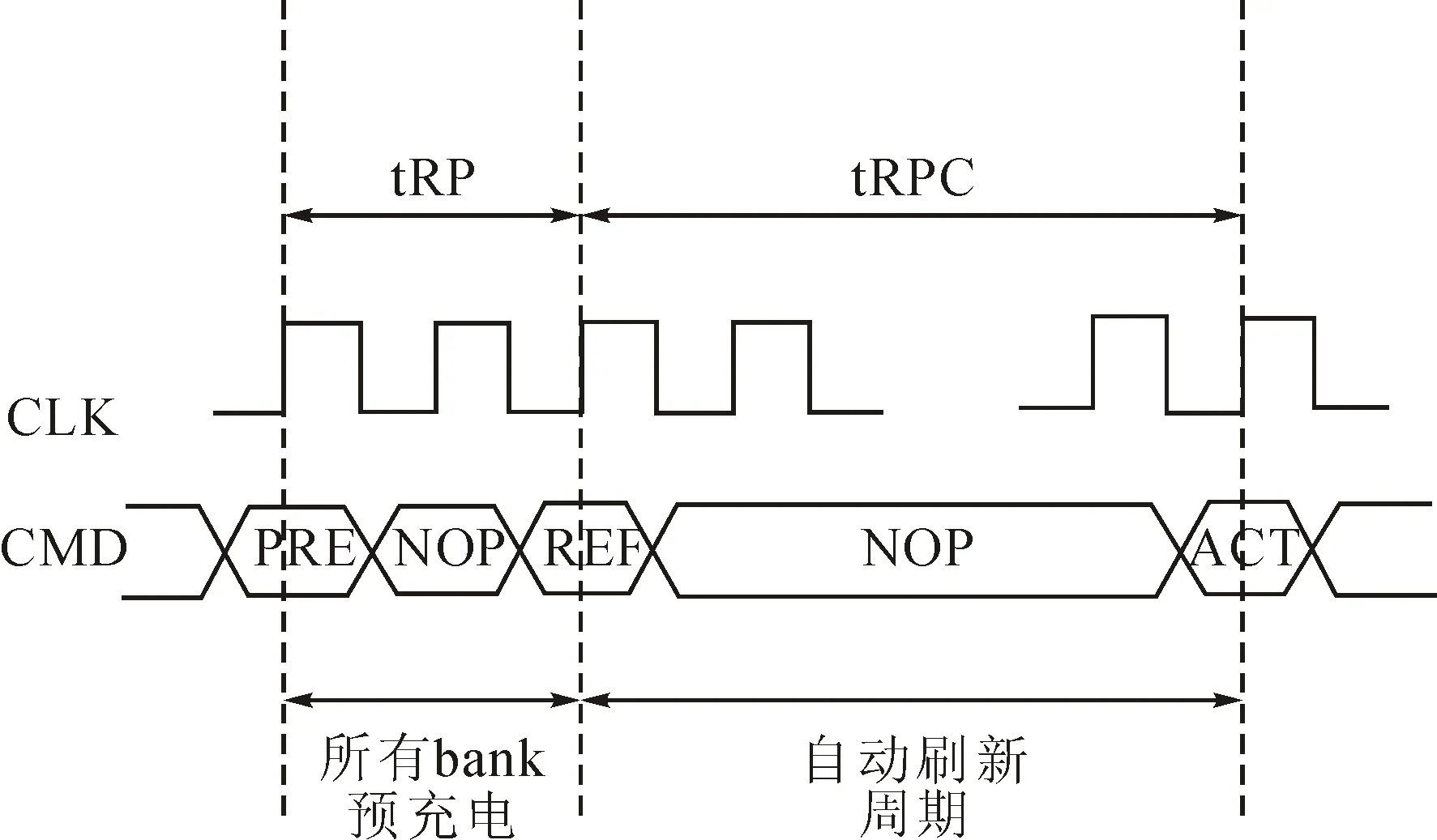

2) SDRAM内部是通过电容存储数据,所以需要定时刷新过程数据以免数据丢失。刷新分为自刷新和自动刷新,而自刷新主要用于休眠状态下数据的保存,本文采用自动刷新。在刷新过程中涉及所有L-bank需要停止工作,在刷新9个时钟周期之后可进入正常工作状态。

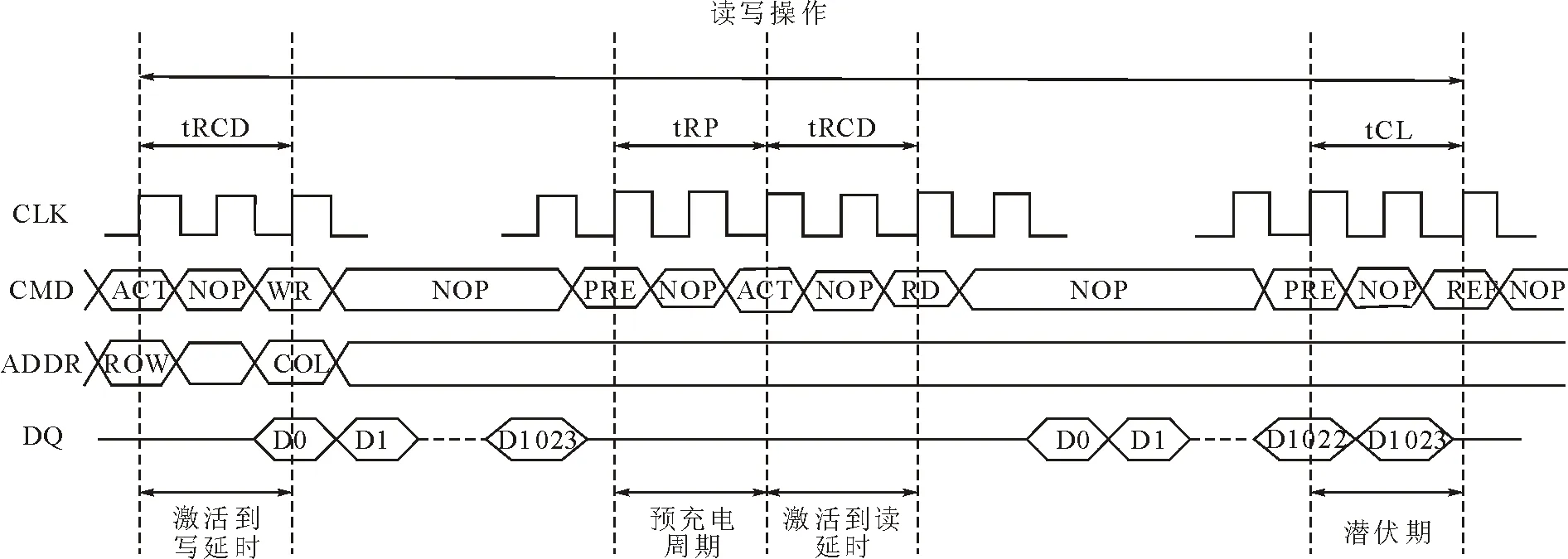

3) 读写过程是影响SDRAM工作效率的关键操作,针对视频图像数据量大的特点,本文选择了全页突发读写模式,以最大可能提高读写速度[12]。读写过程之前需对读写存储单元的行地址进行激活,读写命令与列地址同时发出,且读数据时存在潜伏期。

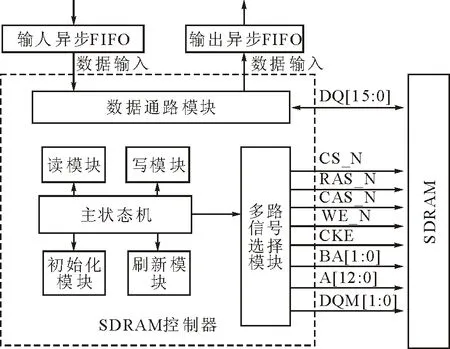

2 SDRAM控制器的实现

本文中SDRAM控制器主要由初始化模块、刷新模块、读/写模块、总状态机模块、数据多路选择模块,数据通路模块。在视频图像处理系统中,该控制器配合两个异步FIFO进行数据之间的衔接。系统框图如图1所示,数据通路模块可获取摄像头所采集的有效数据,也可输出SDRAM中所缓存的有效数据,主状态机控制每个操作模块在特定时间做出正确的动作,保证有效数据与SDRAM芯片进行高速有效交换。

图1 SDRAM控制器系统框图Fig.1 Block diagram of SDRAM controller system

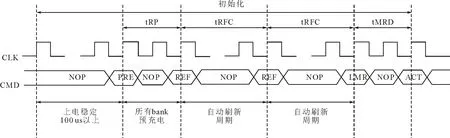

2.1 初始化模块

SDRAM初始化时序图如图2所示,上电后等待100 μs;执行一次所有bank的预充电操作,需等待tRP(行预充电最小周期);接着执行两次自动刷新命令,每次命令均需等待tRFC(自动预充电周期);最后执行模式寄存器设置命令,需等待至少tMRD(LMR命令与激活或刷新命令的最小间隔)。模式寄存器设置方式如图3所示,本文中BL设置为全页,BT设置为顺序类型,CL设置为3。

本文采用有限状态机实现该初始化过程,设计中时钟周期为10 ns,将所有等待时间转换为周期数,整个初始化过程计算出为10 019个时钟周期。实现流程如下:

1)前10 000个时钟周期,命令为NOP,CKE置为1;

2)第10 001个时钟周期,命令为PRE;

3)第10 003个时钟周期,命令为REF;

4)第10 010个时钟周期,命令为REF;

5)第10 017个时钟周期,命令为LMR;

6)第10 019个时钟周期,初始化结束。

图2 SDRAM初始化时序图Fig.2 Sequence diagram of SDRAM initialization

图3 模式寄存器定义图Fig.3 Mode register definition

2.2 刷新模块

SDRAM芯片因内部存储体为电容,需进行不断刷新保持有效数据[13]。刷新具有固定的刷新周期,存储电容的数据有效期最长为64 ms,即每行的刷新周期为64 ms。刷新命令每次只对一行有效,发送间隔跟总行数有关,设计中所选的SDRAM芯片具有8 192行,所以每次的刷新间隔为64 ms/8 192=7.812 5 μs。本文中将单独设计一个刷新模块,考虑到两次刷新间会加入读写操作,因此该模块每隔7.6 μs进行一次刷新,刷新操作的时序图如图4所示。

图4 SDRAM刷新时序图Fig.4 Sequence diagram of SDRAM refreshing

文中采用有限状态机以实现刷新过程,以时钟周期的个数为状态跳转条件。实现流程:第1个时钟周期,命令为PRE;第3个时钟周期,命令为REF;第10个时钟周期,命令为ACT;第11个时钟周期,结束。其关键代码如下。

if(rst)

begin

nop;

refresh_finish <= 0;

end

else

case(time_count)

`ctREF_START: precharge_all;

`ctREF_REF: refresh;

`ctREF_FINISH: ref_finish <= 1;

default : nop;

endcase

2.3 读/写模块

本文分别设计读模块和写模块对SDRAM进行全页突发读写操作,初始化过程结束后,可进行读写操作。首先激活后续将要访问的行,同时给出行地址和bank地址,行列地址访问通过分时复用12位地址总线;发送写命令的同时给出操作列的首地址,并写第一个数据到DQ总线,依次向DQ写完剩余的数据;执行一次预充电命令,等待规定时间后进行行激活,同时给出行地址和bank地址,与写操作不同,读操作具有两个周期的潜伏期,依次从DQ总线读取数据;执行预充电命令,最终完成一次读写操作。全页突发读写操作时序图如图5所示。

图5 SDRAM读写时序图Fig.5 Sequence diagram of SDRAM read/write

文中采用有限状态机实现该读写过程,在全页突发读写完成时此状态机必须立即停止。其读、写过程相似,读操作过程:第1个时钟周期,命令为ACT,送行地址和bank地址;第3个时钟周期,命令为WR,送列地址和第一个有效数据;第1027个时钟周期,命令为NOP,送入最后一个有效数据;第1028个时钟周期,命令为PRE;第1030个时钟周期,读操作结束。其关键代码如下。

case(time_count)

`ctRD_START: active;

`ctRD_READ: read_ap;

`ctRD_GETDATA1: cap_l <= 1;

`ctRD_GETDATA2:

begin

cap_1 <= 0;

cap_h <= 1;

end

`ctRD_FINISH:

begin

read_finish <= 1;

cap_h <= 0;

end

endcase

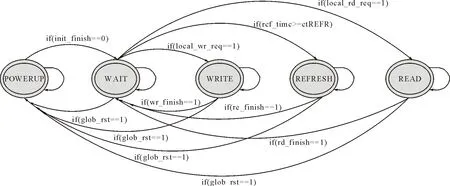

2.4 总状态机模块

本文将初始化操作、读写操作、刷新操作、多路信号选择器都进行了模块化设计,对每个功能进行单独实现,最终由一个总的状态机进行控制。总状态机通过判断,在特定时间执行特定动作来控制各个模块的输出,再通过多路数据选择模块将数据发送到SDRAM芯片。

图6 状态转移图Fig.6 Diagram of state transition

如图6所示,总状态机由五个状态组成,分别为上电初始化状态、读状态、写状态、等待状态、刷新状态。初始化完成之后跳转到等待状态,判断读写、刷新操作是否完成,若未完成,状态停留在等待状态直至各操作完成。

3 仿真结果

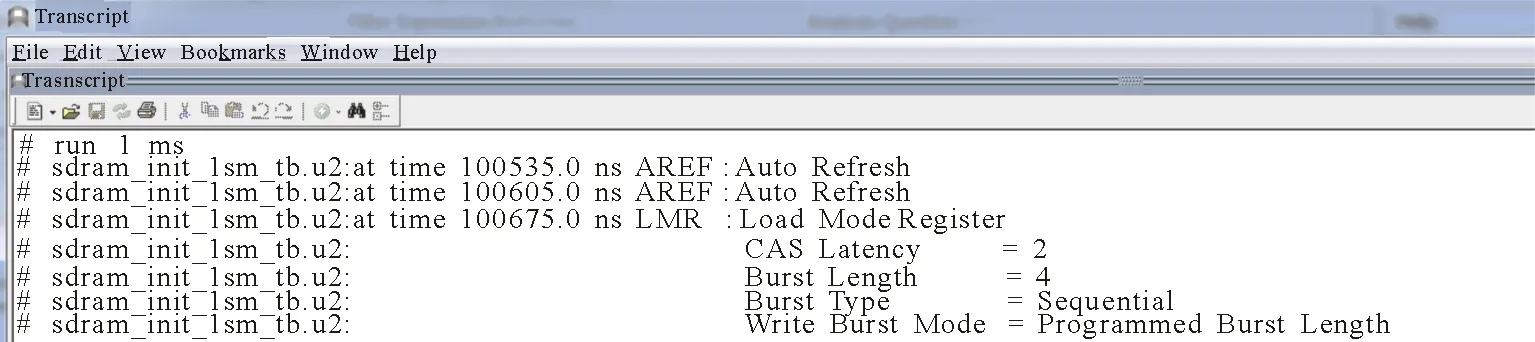

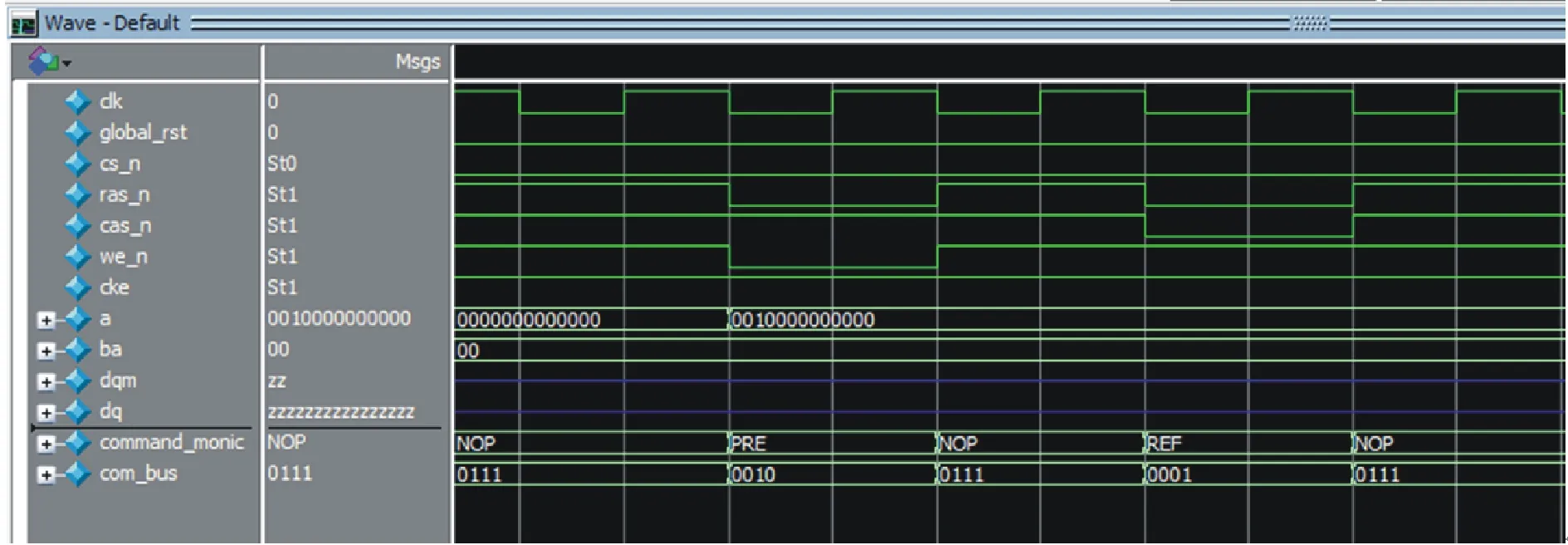

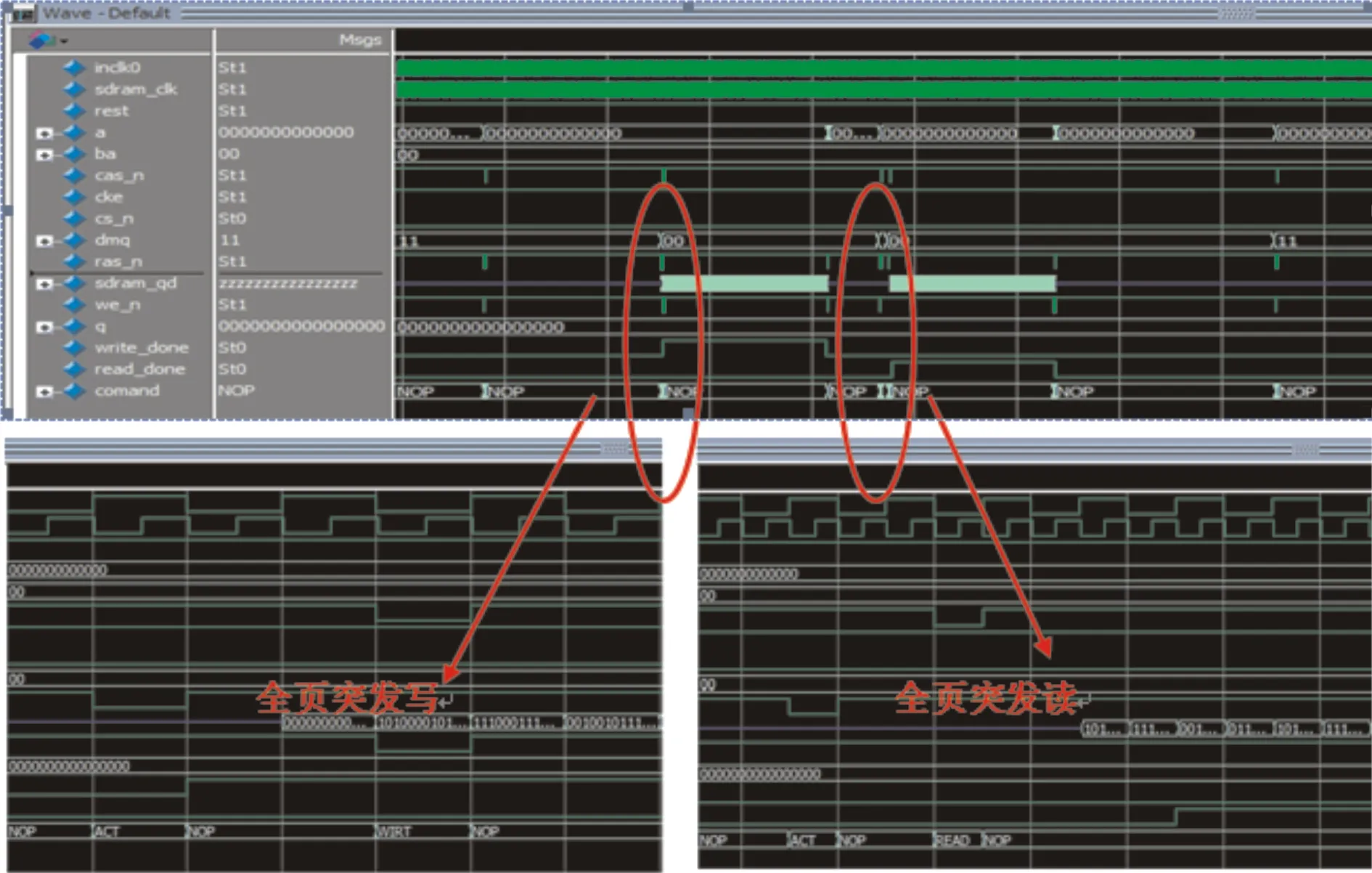

本文中在调试SDRAM控制器时,将所设计的控制器与Micron公司所提供的SDRAM模型共同仿真。首先测试上电初始化过程,该过程的时序图如图7所示。初始化完成之后返回模式寄存器配置信息(如图8所示),返回信息潜伏期为3,突发长度为全页,突发类型为顺序,与文中设计的信息完全相同。图9是在无读写操作时的刷新时序仿真结果,图10是一次全页突发的读写过程。实验结果表明,通过总状态机控制的SDRAM控制器可以完成有效像素数据的缓存。

图7 初始化仿真结果Fig.7 Simulation result of initialization

图8 模式寄存器配置打印信息Fig.8 Information of MR

图9 刷新仿真结果Fig.9 Simulation result of refreshing

图10 读写仿真结果Fig.10 Simulation result of read and write

4 结 语

本文介绍了一种由状态机控制实现SDRAM控制器的方法,把上电初始化、读写操作、刷新操作均采用有限状态机实现,各个模块相互独立,最终由一个总的状态机控制,相比其他实现方法,该方法更为简单。该控制器应用在视频图像处理系统中,可以高速有效地缓存数据,可以通过修改突发长度,配置读写地址应用在更多的场合。

[1]庞双德,刘艳滢. 图像处理系统中SDRAM控制器的FPGA实现[J]. 微计算机信息,2009,25(14):164-165.

PANG Shuangde,LIU Yanying. The implementation of SDRAM controller based on FPGA in image processing system[J]. Control & Automation, 2009, 25(14): 164-165.

[2]杨钦,周云飞,胡永兵. 基于FPGA的视频图像采集与显示系统设计[J]. 计算机工程与设计,2013,34(6):1988-1992.

YANG Qin, ZHOU Yunfei, Hu Yongbing. Design of video image acquisition and display system based on FPGA[J]. Computer Engineering and Design, 2013, 34(6): 1988-1992.

[3]陈文明,刘波,章小兵,等. 高分辨率视频图像处理中SDRAM控制器的设计[J]. 现代电子技术,2013,36(12):97-99.

CHEN Wenming, LIU Bo, ZHANG Xiaobing, et al. Design of SDRAM controller in high-resolution video image processing system[J]. Modern Electronics Technique, 2013, 36(12): 97-99.

[4]刘云川,龚向东. BT.656数字视频流的处理及其硬件实现[J]. 液晶与显示,2013,28(2):238-243.

LIU Yunchuan, GONG Xiangdong. Processing and hardware implementation of BT.656 digital video stream[J]. Chinese Journal of Liquid Crystals and Displays, 2013, 28(2): 238-243.

[5]张杰,胡世安,龙子夜,等. 多速率数据采集与处理系统的设计与实现[J]. 电子测量与仪器学报,2009,23(S1):138-141.

ZHANG Jie, HU Shian, LONG Ziye, et al. Design and realization of multi-rate data acquisition and processing system[J]. Journal of Electronic Measurement and Instrument, 2009, 23(S1): 138-141.

[6]马灵,杨俊峰,宋克柱,等. 地震数据采集中基于FPGA的多DDR SDRAM控制器设计[J]. 中国科学技术大学学报,2010,40(9):939-945.

MA Ling, YANG Junfeng, SONG Kezhu, et al. A design of multiple DDR SDRAM controllers based on FPGA in a seismic data acquisition system[J]. Journal of University of Science and Technology of China, 2010, 40(9): 939-945.

[7]赵强,罗嵘,汪蕙,等. 用于HDTV视频解码器的高性能SDRAM控制器[J]. 电子与信息学报,2007,29(6):1332-1337.

ZHAO Qiang, LUO Rong, WANG Hui, et al. High performance SDRAM controller design for HDTV video decoder[J]. Journal of Electronics & Information Technology, 2007, 29(6): 1332-1337.

[8]王利颖,蒋亚东,罗凤武. 嵌入式实时图像处理系统中SDRAM控制器的实现[J]. 现代电子技术,2009,25(9):137-139.

WANG Liying, JIANG Yadong, Luo Fengwu. Implementation of SDRAM controller for embedded real-time image processing system[J]. Modern Electronics Technique, 2009, 25(9): 137-139.

[9]邓凯,王永明. 一种简单的SDRAM控制器实现方法[J]. 国外电子测量技术,2011,30(9):48-50.

DENG Kai, WANG Yongming. A simple method for SDRAM controller[J]. Foreign Electronic Measurement Technology, 2011, 30(9): 48-50.

[10]陈根亮,肖磊,张鉴. 一种基于FPGA的DDR SDRAM控制器的设计[J]. 电子科技,2013,26(1):52-55.

CHEN Genliang, XIAO Lei, ZHANG Jian. Design of a DDR SDRAM controller based on FPGA[J]. Electronic Science and Technology, 2007, 29(6): 52-55.

[11]王骞,丁轶夫. 高速图像存储系统中SDRAM的实现[J]. 液晶与显示,2006,21(1):48-52.

WANG Qian, DING Yifu. The implementation of SDRAM controller in the high-speed image storage system[J]. Chinese Journal of Liquid Crystals and Displays, 2006, 21(1): 48-52.

[12]刘攀,王红亮,孟令军. 基于FPGA的数字图像采集存储系统的设计[J]. 电视技术,2010,34(6):32-34.

LIU Pan, WANG Hongliang, MENG Lingjun. Design of digital image acquisition and storage system based on FPGA[J]. Video Engineering, 2010, 34(6): 32-34.

[13]郭柳柳, 甄国涌, 刘东海. 基于FPGA高速图像数据的存储及显示设计[J]. 电子技术应用,2014,40(11):75-77.

GUO Liuliu, ZHEN Guoyong, LIU Donghai. High speed image data storage and display based on FPGA[J]. Application of Electronic Technique, 2014, 40(11): 75-77.

(责任编辑 王绪迪,王卫勋)

Implementation of SDRAM controller based on FPGA in video image processing system

HU Liaolin, LIU Guangfei

(School of Mechanical and Precision Instrument Engineering, Xi’an University of Technology, Xi’an 710048, China)

In order to achieve real-time processing of image data in video image processing, using the large capacity memory to complete the data cache is one essential step. It presents a SDRAM controller solution to FPGA chip in the realization of image data cache during video image processing in view of the working principles and time sequence characteristics of SDRAM. According to the requirement for real-time image data transmission rate, the operation mode is configured as full-page burst read and write and auto-refresh, with each operation modularization made and controlled by a total state machine. The design is implemented with Verilog. The result show that the controller is used to complete image data cache in the video image processing successfully, and that it has advantages of high READ/WRITE rate, simple control and low price and so on.

SDRAM controller; data cache; FPGA; modularization; FSM

10.19322/j.cnki.issn.1006-4710.2016.04.014

2015-07-06

陕西省自然科学基金资助项目(2014JM7273)

胡辽林,男,副教授,研究方向为光纤传感及光纤通信。E-mail:huliaolin@163.com

TN79;TP274

A

1006-4710(2016)04-0455-07