基于DSP的时间触发总线设计与实现

2017-01-13毛亚鹏

毛亚鹏

(清华大学计算机系,北京 100084)

基于DSP的时间触发总线设计与实现

毛亚鹏

(清华大学计算机系,北京 100084)

网络通信系统是现代航空电子系统以及其他分布式实时容错系统的中枢,基于时间触发架构的网络通信系统是一个重要的发展方向;首先对于TTP/C协议的基本架构以及上电群启动过程,全局时钟同步,容错策略等关键技术进行介绍,然后提出一种基于TTP的时间触发总线协议,并基于DSP实现协议控制器进行时间触发通讯;结果表明时间触发总线具有良好的时间确定性,容错特性以及较高的总线利用率,适用于航空,铁路,汽车等安全关键系统的底层网络通信。

时间触发;时钟同步;容错策略;时间确定性

0 引言

随着航空电子系统等分布式实时容错系统的逐步发展,其对于网络通信系统的实时性和可靠性需求也在不断提高,相较于原有的事件触发总线如ARINC429,1553B,CAN,以太网等,时间触发架构的总线如TTP,TTCAN,Flex Ray,TTEthernet等具有更高的实时性和可靠性,同时也大大提高了总线的利用率,减少了通信冲突所带来的资源消耗。

在上述基于时间触发架构的总线中,TTP总线是首个被SAE(美国汽车工程师协会)标准化的通信协议。TTP总线主要有两种标准:TTP/A和TTP/C[1],其中TTP/A面向SAE的A类标准,适用于汽车电子等成本较低的非关键应用,而TTP/C面向SAE的C类标准,主要面向高速、实时闭环控制的多路传输网。

TTP/C协议是基于时间触发架构的高速,双余度,多点串行的硬实时容错现场总线协议,可支持5Mbps,25Mbps。目前已经在航空航天领域得到了较多实际应用[2],如洛马公司F16及意大利马基公司M346上的全权数字发送机控制系统FADEC、空客公司A380的客舱压力控制系统、波音公司B787“梦想”客机的电源及环境控制系统等,同时,NASA的新一代载人飞船“猎户座”也使用了基于时间触发架构的TTE网络。

本文将首先介绍TTP/C协议的基本架构,以及上电群启动,全局时钟同步,容错策略,调度表配置等关键技术。然后依据其协议与实际需求,提出基于DSP的协议控制器实现方案,定义合理的数据帧格式,并给出实际通讯波形。结果表明时间触发总线协议具有良好的时间确定性和容错特性。最后,总结了开发过程中的重点和难点,并对于后续工作进行展望。

1 TTP基本架构和通信原理

TTP总线的基本架构[3]如图1所示,一般配置为总线型或星型拓扑结构。每个节点通过通信接口访问总线,总线具有双通道以避免单个信道或者节点故障导致的问题。节点之间通过广播的方式进行数据传输,发送数据时,数据通过两条通信链路进行冗余传输。

图1 TTP基础架构

每个节点分成应用层和TTP通讯层,应用层包括主机层以及与之相连的传感器,作动器等,主机层通过CNI(通信网络接口)与下层TTP控制器进行数据交换,TTP控制器主要包括TTP协议处理器,TTP信息描述表(MEDL),并通过总线开关与TTP总线通道相连。TTP信息描述表存储着控制器的调度控制数据,包括基本的通信行为和必要的启动、集成参数,调度方案ID以及时间触发相关的TDMA参数,而TTP协议处理器则负责按照信息描述表来控制节点的发送和接收等通讯行为,总线开关负责在节点失效时关断以防失效节点干扰总线上正常数据通讯。

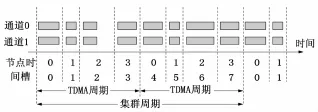

TTP总线的通讯过程如图2所示,以时间触发的方式,基于时分复用的思想,所有节点在全局统一的时钟下,在规定的时间序列规定的时刻进行数据的发送接收任务。整个传输时间轴由重复的集群周期组成,每个集群周期内分成多个TDMA周期,每个TDMA周期被分成多个不等长的时间槽,每个节点都在各自分配到的时间槽内发送数据,以避免通信冲突。

图2 TDMA调度

2 TTP关键技术

基于时间触发通信的一个首要条件是建立一个全局同一的时钟,这个过程需要在启动过程中就开始建立,同时,容错冗余策略对于分布式安全关键系统也是必需的,此外调度表的合理规划对于整体效率也有显著提高。

2.1 全局时钟同步

TTP时钟同步原理[4]为:总线上的节点将会在各自规定的时间槽内进行数据收发,并且都知道具体的收发时刻,通过实际帧的接收时刻和MEDL表中预置的接收时刻的差值,来计算本地时钟与全局时钟的偏移值,并以此来校正本地时钟,实现全局时钟同步。其中参与偏移值计算的帧发送节点被称为同步主节点,主节点时钟精度较高,通常需要保持主节点个数不少于4个以避免拜占庭错误。其余节点则称为从节点,从节点发送的数据帧不参与接收时刻差值的计算。

TTP具体时钟同步算法流程如下:

1)每个节点需要N个寄存器用于存放时间偏移值,其中N为主节点个数,不少于4个。

2)每个节点收到主节点发送的数据帧,计算与MEDL表中预置接收时刻的偏差,寄存器中始终保存最近的N个偏移值。

3)去除N个偏移值的最大值和最小值,对其余值求平均,得到平均时间偏移值。

4)根据全局调度表配置,每个节点都在每个TDMA周期末尾的固定时间槽进行时间偏移计算及校正。

2.2 群启动过程

群启动过程[5]是在系统上电或复位重启时用以建立集群时间同步和状态一致的过程,图3为群启动过程状态图。启动过程中,所有节点均正常上电并初始化,其中启动节点进入启动状态,其余备用启动节点和从节点进入监听状态。启动节点进入启动状态后周期性发送包含全局时间及状态信息的启动帧直到到达预设发送次数,其他节点监听并接收到启动帧后转入被动状态,并通过分析启动帧中的时间及状态信息调整到统一的系统时钟,进入主动状态正常进行时间触发通信。

图3 群启动状态

假如启动节点未正常运作发送启动帧,备用启动节点在监听预置的时间超时后,转变到启动状态,替代未正常工作的启动节点发送启动帧以使集群正常启动。不同备用启动节点预置的超时时间不同,以避免启动帧冲突或产生不同的启动状态。

2.3 容错策略

TTP协议的容错策略主要为成员关系确认算法。TTP协议通过扩展的CRC维护节点间成员关系列表,即数据帧中不包含成员关系列表,但是CRC校验和是结合关系列表来计算得到,因此接收节点在接收到数据帧后结合本地的成员关系表进行CRC校验,若结果一致,则表明接收正确,同时成员关系也正确,则在后续数据帧的附加部分给出确认状态。发送端节点会在发送数据帧后监听两个后续帧状态,若至少有一帧给出确认状态则认为数据发送成功,若两帧均无确认,则认为发送失败[2]。

2.4 调度表配置

时间触发架构节点按照预先配置的调度表来确定各自的发送和接收时间,每个节点均有各自的时间槽。调度表需要确定集群周期以及TDMA周期的长度,TDMA周期内各个时间槽的长度和起止时间。这些数据的确定需要考虑实际节点传输数据的周期以及长度,当节点数较少或者总线负载较低时,可以简化调度表模型以方便配置。当节点数量较多且数据信息种类也较多,如有多个发送周期,长度不同等,则需要在满足数据发送要求的情况下尽量减少时间片总长度,提高效率的同时提供更多的时间用于突发消息的传输。由于调度表为预先配置,因此可以使用较耗时的优化算法[6 7]提前规划,以使总线运行状态达到最优。

3 基于DSP的时间触发总线设计与实现

3.1 系统框图

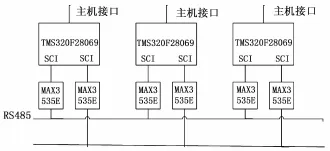

节点协议控制器以TMS320F28069来实现,通过两路SCI经过MAX3535E转换芯片连接到RS485总线进行时间触发通讯。TMS320F28069作为协议控制器,向上通过主机接口与主机交互,包括数据传输以及MEDL表的配置部署;运行时负责整个协议框架的调度运行,包括精确定时和时钟同步,接收和发送数据等;数据通过SCI串行通信接口经过MAX3535E转换芯片连接到RS485总线,由于TTP需要两个物理层通道,因此使用两个接口分别连接到两个通道,其中MAX3535E提供发送使能控制,使每个节点只有在自己的发送时间槽才占用总线。

3.2 帧格式

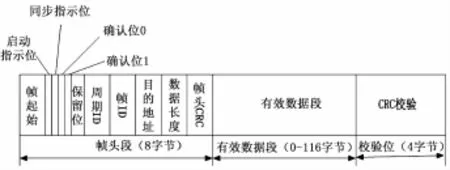

根据TTP协议以及部分实际需求,定义如图5所示帧格式。

帧长度为128字节,由帧头、有效数据段和校验位组成。帧头包含8个字节,分为帧起始位,启动指示位,同步指示位,两个确认位,保留位,周期ID,帧ID,目的地址,有效数据长度,帧头CRC校验。帧起始位用于指示帧的开始,启动指示位用于指示当前帧是否为启动帧,同步指示位则指示当前帧为同步帧,两个确认位用于实现后续帧对于前面帧的接收确认,保留位用于后续功能扩展。周期ID和帧ID用于指示当前帧在集群周期中的位置,目的地址用于指示接收节点,数据长度用于指示有效数据段长度,最后是帧头的CRC校验以验证帧头段的正确性。

图4 系统框图

图5 帧结构

有效数据段长度可变,范围为0~116字节,用于传输实际应用数据,如果启动帧或同步帧无数据需要发送,则有效数据段为0。由于帧头数据长度段表示范围限制,有效数据段长度以字节为单位。

CRC校验用于校验帧头和有效数据段,长度为4字节,选取CRC-32标准多项式0x104C11DB7.

3.3 通讯流程

各个节点控制器运行通信软件流程如图6所示。

图6 软件通信流程

预先选取时钟精度高且稳定的节点作为主节点,负责系统启动与全局时钟同步,主节点在上电复位初始化后按照群启动流程发送启动帧,从节点中的备用主节点负责在监听超时后发送启动帧,以确保系统正常启动。正常启动后各个节点按照MEDL表中预置时序逻辑执行任务,在各自时间槽到达时发送相应数据帧或同步帧,并在相应时间接收总线上数据,其余时间处理节点的非通讯任务。接收模块在接受到数据帧后首先进行校验位判断,如果校验位出错,则将对应确认位置位以供发送节点判断,若校验位正确,则解析有效数据段数据以供主任务使用,同时解析帧头段状态以获取确认位信息,并记录错误或进行对应处理。各流程结束后均回到时序判断状态,等待下一个任务。

3.4 测试与实验

按照前述系统框图及帧定义,流程设计实现实验用平台,包含3个节点,其中1号节点为主节点,负责启动及同步帧的发送,2,3号节点为从节点,主要发送数据帧。整个集群周期时序设计由于节点数有限,实验时设计为主节点在每个周期发送同步帧,之后1,2,3号节点依次发送数据帧,每个时间槽时长为1 ms,波特率设置为2.5 Mbps,以10 ms为周期。节点信息描述表(MEDL)需预先配置,包括集群周期的时序,以及相关节点间数据帧的传输处理时延,定时器的最小时间单位等。

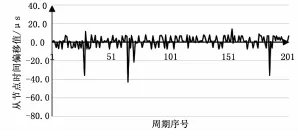

图7 从节点时间偏移值

图7所示为主从节点间通过每个周期全局时钟同步后从节点的时间偏移值,在200个采样周期中,从节点偏移值基本保持在10μs以内,极少数周期出现偏移值达到40μs。因此在实际通信实验的时间槽分配中预留偏移时间为100μs以避免多个节点间时间重叠而产生的通信冲突。

4 结论

时间触发协议总线基于时间触发架构,由于没有通信冲突,既减小了数据缓冲区的需求,同时也极大提高总线利用率;同时通过提供精确全局时钟同步并按照时序进行数据传输,提供了较好的时间确定性和实时性;采用成员关系表及双通道等容错策略,提供了错误的精确隔离便于诊断和应对;同时由于底层通讯与主机应用层的分离架构,利于实现设备的并行开发和维护,并降低了系统的寿命周期成本[8]。这些特性很好的满足了航空电子系统的需求,同时也会逐渐被应用到铁路,汽车等安全关键系统中。

通过对于时间触发协议总线的通信原理及关键技术的分析,搭建了基于DSP的协议控制器以及总线通信实验平台,设计合理的帧结构以及软件流程,实现基本的时间触发架构并进行通信实验。对于TTP协议中的容错策略,目前还未完全实现,因此在之后的工作中需要实现协议中的容错服务,并尝试应用到具体的工程项目中。

[1]Time-Triggered Protocol TTP/C High-Level Specification Document Protocol Version 1.1[S].Specification edition 1.5.2 of 5-Jan-2004 Document number D-032-S-10-028.

[2]金德琨,敬忠良,王国庆,等.民用飞机航空电子系统[M].上海:上海交通大学出版社,2011.

[3]Kopetz H,Grünsteidl G.TTP-A time-triggered protocol for fault-tolerant real-time systems[A].The Twenty-Third International Symposium on Fault-Tolerant Computing,1993[C].FTCS-23.Digest of Papers,IEEE,1993:524-533.

[4]Leen G,Heffernan D.TTCAN:a new time-triggered controller area network[J].Microprocessors and Microsystems,2002,26 (2):77-94.

[5]张兴隆,苏罗辉,杨 敏.基于FPGA的时间触发协议控制器实现[J].系统仿真学报,2010(A01):114-118.

[6]Zeng H,Natale MD,Ghosal A,et al.Schedule optimization of time-triggered systems communicating over the FlexRay static segment[J].Industrial Informatics,IEEE Transactions on,2011,7 (1):1-17.

[7]Lukasiewycz M,Glab M,Teich J,et al.Flex Ray schedule optimization of the static segment[A].Proceedings of the 7th IEEE/ACM international Conference on Hardware/Software Codesign and System Synthesis[C].ACM,2009:363-372.

[8]Kopetz H,Ochsenreiter W.Clock synchronization in distributed real-time systems[J].IEEE Transactions on Computers,1987,100(8):933-940.

Design and Implementation of Time-Triggered Protocol on DSP

Mao Yapeng

(Department of Computer Science and Technology,Tsinghua University,Beijing 100084,China)

The communication network system is the key technology to the avionics system and other distributed real-time fault-tolerant systems,and the communication network systems based on Time-Triggered Architecture indicate an important upgrade direction.It firstly introduces the basic structure of TTP/C,and the key technologies like start-up process,global time synchronization,fault-tolerant strategy.Then introduces a simplified time-triggered protocol based on TTP/C,and implements the protocol controller on DSP to realize the time-triggered communication.The results show that time-triggered protocol is quite a suitable communication network system for the avionics system,railway system,automotive system and other safety-critical system with its time determinability,fault-tolerant strategy and higher bus utilization rate.

time-triggered;time synchronization;fault-tolerant strategy;time determinability

1671-4598(2016)08-0209-03

10.16526/j.cnki.11-4762/tp.2016.08.057

:TP393

:A

2016-01-28;

:2016-03-10。

毛亚鹏(1990-),男,浙江绍兴人,硕士研究生,主要从事总线通信技术方向的研究