高可靠分布式容错计算机架构的研究

2017-01-13解文涛

解文涛,王 锐,徐

(中国航空计算技术研究所,西安 710119)

高可靠分布式容错计算机架构的研究

(中国航空计算技术研究所,西安 710119)

新一代飞机平台对操作性能、安全和可靠性、综合保障能力等特性提出了新的要求,飞机管理计算机作为飞机平台的安全关键部件,其系统结构、容错技术等需要适应不断变化的微电子和计算机技术的发展;为适应上述发展趋势,国外尝试将各项先进技术应用于新一代飞机平台,使飞机具有先进飞行控制系统的功能和品质,实现从传统单一飞行控制系统发展成为包括了集飞行控制、推力控制、公共设备管理等功能一体的飞机飞行平台控制、监测、配置系统,最终形成了综合飞行器管理系统;作者在吸取国外先进系统构架的基础上,对系统体系结构、实时调度算法和容错技术进行深入的研究,提出了基于高可靠分布式构架的容错计算机的设计思路,并对TTE总线的选用进行了分析论证,重点描述了成员一致性保证和余度同步等关键技术;该容错计算机系统实现了基于TTE网络的分布式容错技术,研制的原理样机验证系统具有分散安装、可靠性高、扩展性好、维修成本低、健壮、安全等诸多优点。

分布式;容错;同步;TTE总线

Keywrds:distributed;fault tolerance;synchronization;TTE bus

0 引言

随着系统信息处理技术、数字控制技术、飞行控制技术和功能需求等多方面快速发展,传统集中式计算机系统的全总线化结构[1]逐渐暴露出以下问题:

1)没有物理统一的网络、CCDL通信网络与外部通信网络隔离;

2)总线式结构扩展能力有限、灵活性差;

3)系统连线较多、环形网络布线复杂、重量较大、维修性差。

为了解决传统结构的不足,国外设立许多计划研究先进的IVMS体系结构。国外新设计的IVMS体系结构呈现出分布式的发展趋势[2],空客公司最新提出了基于交换通信网络的分布式飞行控制系统。该系统以交换式通信为骨干,系统各节点都配备终端网络接口,飞行控制子系统间完全通过网络进行信息交换。系统中大量使用智能作动控制器,实现了执行部件的控制与检测功能的分离[3],降低了系统余度的复杂性和硬件配置要求,使得系统布线简单,设备安装、配置、扩展灵活,故障隔离好,系统安全风险低和易维护等诸多优点。

新一代航空飞行器的设计理念是将飞行控制、推力控制和公共设备管理等系统功能综合到IVMS中实现[4],并基于确定性通信技术,采用全网分布式开放系统架构,通过使用符合ARINC 653标准和DO-178B规范的安全实时操作系统,在时间、空间分区保护机制下,实现不同安全级别功能在计算机平台上的综合,实现余度管理和故障自动重构,提升了系统的资源利用率、可靠性、生存性,降低了系统的体积、重量、功耗、布线复杂度和全寿命周期费用等。

1 确定性通信网络的选用分析

对于分布式机载强实时高安全控制系统而言,节点间通信的实时性与确定性是系统实现的关键。目前实时嵌入式计算机系统中普遍使用基于事件触发的串行通信协议[5]。大量研究表明:对高可靠性系统而言,基于时间触发的总线网络的解决方案更具优势。时间触发架构 (Time-triggered Architecture,TTA)系统和事件触发架构 (Even-triggered Architecture,ETA)系统的工作原理不同。前者的控制信号来源于时间进程;后者的控制信号来源于事件的发生(如一次中断)。时间触发系统中使用的状态信息来自规定时间内的某个条件,如传感器的值;而事件信息一般是在事件发生时激活中断服务程序采取相应的措施。

ETA系统与TTA系统之间的基本不同与控制信号源有关。在TTA系统中控制总是驻留在分布式计算机系统的内部。TTA系统是一个物理上封闭的确定性系统[6]。在ETA系统中,控制信号可能源自计算机内部,也可能源自计算机系统外部的环境(如中断机制转发过来的)。不可预测的环境将因而导致计算机系统的不确定性的行为。

从2006年开始,奥地利维也纳大学Kopet研究小组成立的了TTTech公司,开发和推广TTA通信产品,TTEthernet网络(TTE)是其最先进的技术,TTTech公司对基于时间触发以太网给出如下定义:

TTE=以太网+时钟同步+时间触发通信+速率受约传输+保证传输

TTE通过一个内在的、集中式的调度表控制它自己的活动及外部环境之间的相互作用,而传统以太网采用的ET(E-vent-Triggered事件触发)型网络则受控于外界环境,并对外部事件的刺激做出响应。

2 分布式计算机架构设计

高可靠分布式容错计算机系统包括3个节点计算机,分布在3个结构独立的机箱内,满足不同的任务、不同的余度配置要求。系统整体结构采用TTE总线基础上的分布式架构,系统总体结构如图1所示。系统采用3余度高完整计算架构、保证系统在任意两次故障后,能够继续完成关键任务。从物理结构上,系统包括3个结构独立的节点,通过高速串行网络互连,从逻辑结构上,所有的模块处于同一个网络上,其中CPU模块都是对等的,即每个CPU模块都对系统的计算、余度管理等功能负责,系统中只要保留2个CPU模块,1个RDC模块,即可保证系统的工作。每个节点内RDC自动完成(即RDC发生可自检的故障,也可通过接收网络上CPU命令,由RDC完成)。

系统工作时3个容错计算机节点同时工作,通过TTE数据总线交换信息,节点计算机对信号源的信息进行交叉比较,再将信息进行节点间的交叉表决,最终表决值参加控制率计算。任何一个处理器故障均会由同一节点内的另一处理器隔离,任何一个节点故障(两次故障),该节点上的任务将有其它节点代替执行。系统节点计算机之间采用松耦合的同步工作,节点计算机间的同步和交叉信息交换通过通信分区来实现。系统容错通过采用备份功能分区的切换和资源的重新分配完成。

系统软件设计包括3个部分:操作系统、余度管理功能包以及应用软件。从逻辑结构上,三者之间的关系如图2所示。

图1 系统总体结构

图2 系统软件结构

3 成员一致性保证技术

飞行器管理计算机实现对多个任务的功能综合,满足不同安全级别、不同余度配置任务共享平台的系统要求[7]。为保证各功能在共享硬件上运行的安全性及隔离性要求,系统需要设计管理中间件来实现系统成员一致性保证协议[8]。成员一致性保证是实现由集中式容错向分布式容错跨域的关键[9]。成员一致性保证技术包括:一致性决策算法、隐含确认算法。

飞行器管理计算机系统的每一节点机上都设置一个任务成员表单。表单中会记录所有正常运行的分区任务。每一个节点机在获取到信息时都会依据是否接收成功标志更新本地的任务成员表单。每次在信息传递的过程中,接收一方都要检查隐藏或包含CRC校验码的发送方的任务成员表单。因为所有节点机都严格按照时间触发周期的调度方式收发信息,每一节点机都会在一个时间触发周期内检查所有成员的表单。当与接收方有交联的所有任务成员表单都不同时,发送方节点机被认为是有误的。这种策略就通过节点机间的相互确认保证了系统内所有节点机的一致性。整个成员一致协议设计包含两部分:第一部分是隐含确认机制与一致性表决机制。以下是两个算法的实现原理。

一致性表决算法:每个节点机维护一张本地的成员任务成员表单。当某一个节点机准备与其它节点机交换信息数据时,将自身任务执行情况添加到本地成员表单中。当接收方收到正确的信息数据时,它将发送方节点机加入到本地成员表单中。节点机依据以下3个条件判断信息数据传输正确与否:信息传输须发生在预定的时间偏差内;传输活动成功完成;在将发送端加入接收端的成员表单后,双方的成员表单内容须一致。接收端检查校验发送端传输数据,如发现错误,发送端节点机将被接收端节点机从其成员表单内删除。数据若正确,节点机则会将发送端节点机加入成员表单并使确认计数器累加,若接收失败时,接收端节点机将从成员表单中删除发送端节点机并使失败计数器累加。接收端节点机可判断出成员表单是否匹配、数据是否完整以及是否成功数据传输等情况(空帧)。当出现空帧时,接收端节点机不累加任何计数器,但将本应出现在该时段的发送数据的节点机从成员表单中删除。在某节点机发送数据前,要执行成员表单决策算法。节点机先检查在上次发送后接收的错误帧是否多于正确帧,即比较失败计数器是否小于确认计数器。若结果为真,节点机将清零两个计数器并将数据送出;反之,节点机将上报一个错误给上级应用层,然后进入故障静默状态。

隐含确认算法的主要内容是诊断出节点机的故障并将结果通知其它所有非故障节点机。具体可描述为如下过程:在时间段t的广播者p,发送消息,然后检测下一时间段的非故障广播者q的成员表单,如果p包含在q的成员表单中,并且表单中的其它成员均相同,则q可以推出自己信息广播成功。否则,可能的原因是p发送故障或q接收故障,p须等待另一非故障广播者r,如果q的成员表单中包含p,但不含q,p和q表中的其它成员内容相同,说明p消息发送成功,则q接收故障。若p不在r的成员表单中,但q在r的成员表单中,q和q表中的其它成员内容相同,则推断p发送故障。此时,p自己将移出成员表单,进入故障静默状态。若节点机在其下一个时间触发周期前还未完成隐含确认算法,则该节点机将会因为决策算法而被动进入故障静默状态。

4 同步技术

络底层时间同步,建立分布式网络统一的时间基准对系统至关重要。网络时间协议是通过软件的方法提供了一种在系统互连网络上实现时间同步和协调的一种机制。如在以太网上采用的网络时间协议、简单网络时间协议和精密时间协议等。

高精度时间同步技术是实现TTA架构的分布式计算机系统的关键。高可靠分布式计算机的多数表决策略需要同步技术消除异步度[10],节点机内部两个CPU模块之间,以及CPU模块与RDC之间也需要同步技术协调一致。另外,综合在CPU模块上的不同分区应用任务,对实时性、确定性以及部件协调性均有要求,因此分区间的同步技术也是不可回避的重要内容。

节点同步技术。系统中所有节点计算机使用两步同步方法:1)“对齐后调度切换”;2)“周期重新同步”对节点计算机的本地时钟与通信控制器的时钟进行校正对齐,从而实现节点时间同步。该方法能够实现节点计算机与网络时钟的直接同步,从而意味着系统中各节点的间接同步。节点同步示意图如图3所示。

同步的主要功能是维持本地节点机与其它有效节点机的同步运行。同步是为了消除不同节点之间的运行周期的异步度,在同一时间运行相同的帧任务,保证CCDL的时间一致性。同步是系统分区的最高优先级任务,在同步期间需要停止时间计数,并在同步完成后从零时间开始新一帧的时间周期。

消息时间同步技术。除了节点同步技术,还需实现通信网

图3 同步在分区下的调度情况

传统的网络时间同步方法主要存在以下问题:

1)采用B/S架构,时间服务器故障会导致全局故障,系统容错性能差。

2)采用纯软件算法的同步校正方法,由于网络固有的传输时延不确定性,处理器性能差异导致软件时间同步的精度不高。

为解决上述问题,国外主要采用以下新方法来改进分布式系统中网络时间同步:

1)采用软硬件结合的方法,在现有网络的基础上适度增加硬件支持,实现软硬件混合的时间同步,如新颁布的IEE1588协议推荐方法,同步提升同步处理的实时性提高系统时间同步精度。

2)提高网络时间消息传输的优先级、减少传输抖动、提升同步的稳定性。

3)优化同步算法,采用先进的表决、选举算法、降低单时间服务器对系统全局时钟的影响,提升系统同步的鲁棒性。

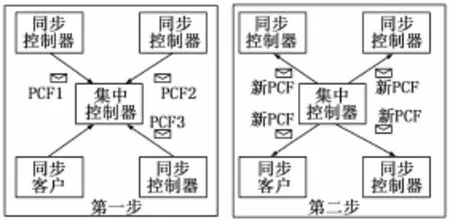

消息时间同步方法是采用上述先进理念开发出的一种新型容错的高精度时间同步解决方案,属于软硬件相结合的方法,全局时钟同步包括同步流程、集群检测与处理、多同步域/多优先级网络时钟同步等内容。时间同步流程分为两步,如图4所示。

图4 时钟同步流程

首先,同步控制器向同步集中器传输协议控制帧(protocol control frame,PCF)。PCF帧并非在任何时间都可以发送,是在本地时钟指示到达一定的时间后,才会发送PCF帧。同步控制器的本地时钟与PCF帧有关系,如发送时间。当PCF帧送达集中控制器,PCF帧会记录在该传播过程中的延迟情况,包括传播延迟、动态发送延迟以及动态接收延迟等。

其次,同步集中器接收到与之连接的各链路上的不同源PCF帧后,经过时序保持算法与集中算法获得一个新PCF帧,并将该帧发向同步客户与同步控制器。集中控制器的作用类似一个仲裁机构,依据同步控制器发送的PCF帧,通过集中算法与时序保持算法,表决计算出一个都认可的时钟,然后把该信息送回同步控制器及同步客户代理,经过同步控制器与同步客户代理处理后就可实现同步了,直至实现全域同步。

节点机上网络同步和分区时间同步的实现是建立在网络同步的基础上,利用分区调度表切换的方式实现了分区间时间同步。

5 测试与验证

为了进一步验证该构型计算机的容错能力,建立了一个集开发、系统仿真、测试及综合为一体的容错计算机综合测试、验证及演示平台,如图5所示。平台支持余度容错计算机的设计与分析、软件开发、系统综合和测试、以及演示验证的功能,实现对容错计算机系统的研究,包括软/硬件测试方法、故障检测方法、故障隔离方法、故障恢复方法等方面的研究。同时,可对容错计算机系统提出定量的分析,包括在采用不同的处理器系列、不同的余度结构的容错计算机下,系统的可靠性分析、可用性分析、维护性分析。

图5 原型系统测试验证环境原理

在上述测试验证平台下,完成了对TTE网络关键技术的测试和验证,包括测试系统的网络通讯能力、数据备份传输功能和容错能力消息收发的波形示例。对三节点高可靠分布式容错计算机的测试,验证了三节点系统架构满足飞机的飞行控制与管理基本功能,对接口故障、处理器故障的容错功能测试,证明系统具备至少2次故障工作的能力,对故障静默等能力的测试,证明系统可用性等性能指标满足要求,解决了当系统发生故障时,在系统现有资源状况下,在保证系统关键任务的条件下,系统功能的缓慢降级,达到系统当前资源与系统工作模式的最佳匹配,从提高重构决策速度及提高关键数据管理水平两方面着手提高故障恢复速度及完整。

6 结束语

高度功能综合、网络化、分布式的计算机系统将是容错计算机发展的显著特征。本文围绕先进航空飞行器对分布式计算机系统的需求进行了分析,提出了高可靠分布式容错计算机的构架建议,重点对TTE网络、成员一致性保证以及余度同步等关键技术给出了解决途径,为后续工程研制提供了有效思路。

[1]郭丽娟.基于时间触发的高可靠实时系统架构[J].计算机工程,2006.

[2]John Rushby.CSL Technical Report:A Comparison of Bus Architectures for Safety Critical Embedded Systems[R].SRI International,Menlo Park,California,March 2003.

[3]王树义,南建国,赵松云.综合化航电核心处理系统容错设计[J].计算机测量与控制,2012,20(8).

[4]陈 益,程俊强,林 坚.新型飞行管理计算机的设计[J],计算机技术与发展,2006,16.

[5]冯晓旺,蓝海文.新一代航空航天总线技术[J].航空制造技术,2012.

[6]Hermann Kopetz.The Time-Triggered Architecture[Z].IEEE,2003:112-124.

[7]周耀荣.用于综合化模块化航电系统的高安全性虚拟分布式计算机系统[R].中国航空工业第631研究所,2008,10.

[8]姚学礼.网络通信协议一致性测试研究[J].通信技术,2009,42(5).

[9]Doerenberg,et al.Fault Tolerant Data Communication Network [P].United States.Related U.S.Application Data.US7206877 B1.Apr.17,2007.

[10]徐拾义.可信计算系统设计和分析[M].北京:清华大学出版社,2006.

Research on Architecture of High Dependable Distributed Fault-tolerant Computers

Xie Wentao,Wang Rui,Xu Ao

(Aeronautical Computing Technique Research Institute,Xi′an 710119,China)

A new generation of aircraft platform on the operating performance,reliability,security and comprehensive security features put forward new requirements,the management computer as the safety key components of the aircraft platform,the system structure,such as fault tolerant technology needs to adapt to the changing of the development of microelectronics and computer technology.In order to adapt to the development trend,try to all kinds of advanced foreign technology is applied to a new generation of aircraft platform,make the function of the aircraft with advanced flight control system and quality,realize from the traditional single flight control system become including a set of flight control,thrust control,public equipment management functions such as the integration of the aircraft flight control,monitoring,configuration,system platform,finally formed a comprehensive vehicle management system.The author on the basis of absorbing foreign advanced system architecture,the system architecture,do some in-depth study of real-time scheduling algorithm,and fault tolerance technology,is proposed based on high reliable distributed fault tolerant computer design,and analyzes the selection of TTE bus,focusing on the members to ensure consistency and redundancy,synchronization and so on key technologies.The fault tolerant computer system to realize the distributed fault tolerant technique,based on the TTE network principle prototype verification system with dispersion installation,high reliability,good scalability,low maintenance cost,robust,secure,and many other advantages.

1671-4598(2016)08-0161-04

10.16526/j.cnki.11-4762/tp.2016.08.043

:TP338.8

:A

2016-01-21;

:2016-03-14。

解文涛(1977-),男,西安市人,高级工程师,主要从事计算机应用方向的研究。