并行交替高速数字化仪的研究与设计

2017-01-12甘伟旺李智

甘伟旺++李智

摘 要: 为了解决低采样速率数字化仪的现状,研制了基于四片ADC并行交替采样高速数字化仪。首先介绍了基于多片并行采样的原理,给出了基于FPGA和ARM数字化仪的整体设计方案;然后对并行交替采样的误差进行了理论分析并设计了Farrow结构的分数延时滤波器对并行时间误差进行校正;最后对数字化仪采样数据进行频谱分析实验。实验结果表明,研制的高速数字化仪能有效、快速地提高系统的采样率,且校正效果良好,在实际工程中有良好的应用前景。

关键词: 并行采样; 数字化仪; FPGA; 高速数据传输; Farrow滤波器

中图分类号: TN79?34; TP335+.1 文献标识码: A 文章编号: 1004?373X(2016)23?0078?05

Research and design of parallel and alternate high?speed digitizer

GAN Weiwang1, LI Zhi2

(1. School of Electronic Engineering and Automation, Guilin University of Electronic Technology, Guilin 541004, China;

2. Guilin University of Aerospace Technology, Guilin 541004, China)

Abstract: In order to solve the low sampling rate situation of digitizer, a parallel and alternate high?speed digitizer based on four ADCs was developed. The parallel sampling principle based on multiple ADCs is introduced. The overall design scheme of the digitizer based on FPGA and ARM is given. The theoretical analysis for the error of parallel and alternate sampling is performed. A fractional delay filter with Farrow structure was designed to correct the parallel time error. The sampling data of the digitizer is conducted for spectrum analysis experiment. The experimental results show that the high?speed digitizer can improve the system sampling rate effectively and quickly, and has perfect correction effect and good application prospect in practical engineering.

Keywords: parallel sampling; digitizer; FPGA; high?speed data transmission; Farrow filter

0 引 言

数字化仪是将模拟信号转换成数字信号的电子设备。高速高精度的数字化仪适用于地质测量、测绘、国土、航空雷达、生物医疗、高端仪器设备等,在这些应用领域中对数字化仪的采样速度和精度都提出严格的要求。然而,受电子技术发展的制约,普通的数字化仪和示波器不能同时满足高速和高精度的要求。研制高采样速率的数字化仪是当前数据采集领域的重要研究方向。

受电子器件制造工艺的影响,单片ADC很难同时满足高采样速率高采样精度的要求。并行交替采样结构能有效地提高整个系统的采样率,同时能降低系统的成本。然而该结构虽然解决了高采样率和高精度的矛盾,但同时也给系统引入了失配误差。失配误差主要有三种,其中包括增益误差、偏置误差和时延误差[1?3]。这些误差处理不当,将会严重影整个系统的性能。

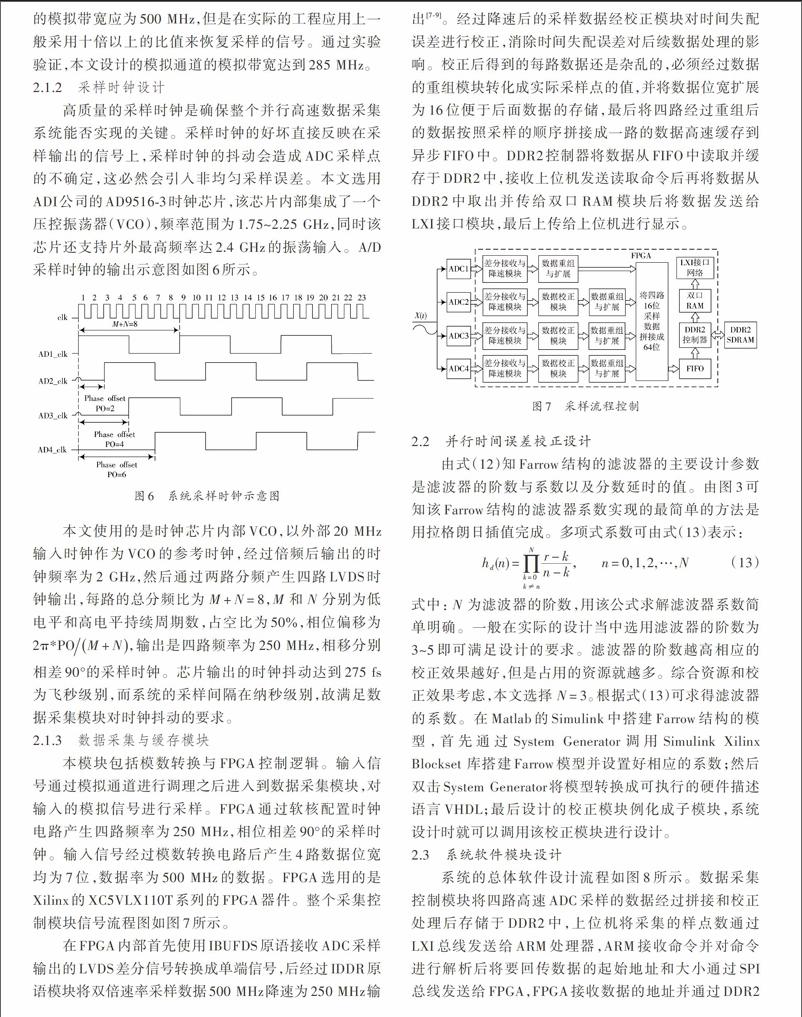

针对传统数据采集系统的精度高但采样率低的现状,本文设计了基于FPGA与ARM架构的高速高精度数据采集系统,采用了并行交替采样结构[4],使用四片低速ADC实现高速采集、存储、处理和传输,对时间失配误差进行频谱分析,并设计了分数延迟滤波校正模块对其进行校正。

1 并行交替采样的原理

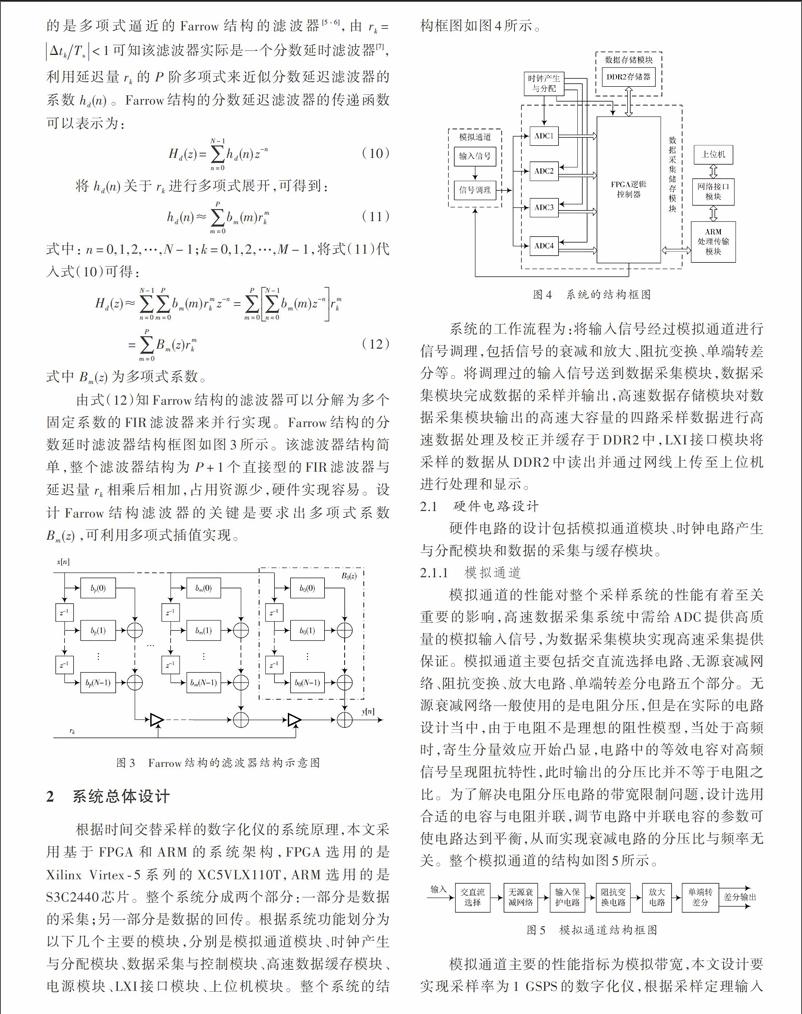

1.1 并行交替采样系统结构

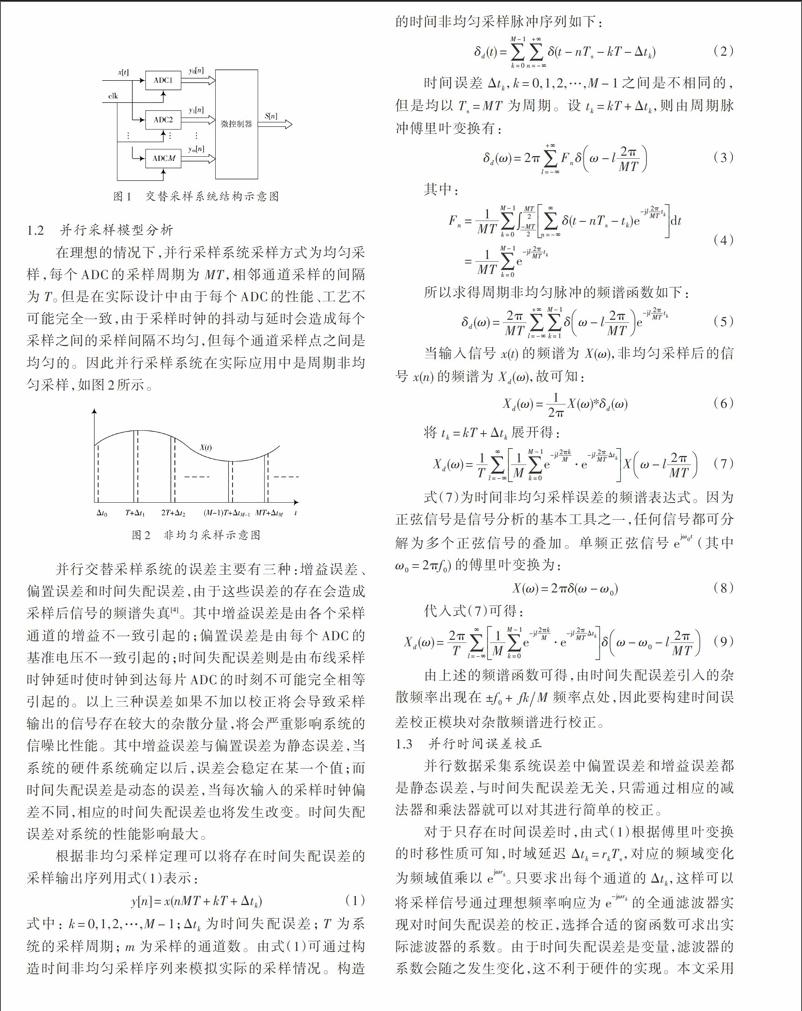

并行交替采样的思想最早是由Black和Hodges提出[5],基本思路是由[M]路独立的ADC组成采样通道,每一个采样通道的采样率为[fsM,]所有通道之间的相位差为[2πM,][M]路采样通道对同一个输入信号进行并行交替采样,最后再将这[M]路的采样数据按照采样的时间顺序通过多路选择器进行数据的拼接,组成采样率为[fs]的数字化仪。交替采样系统结构如图1所示。

3 实验结果及分析

根据上述原理设计了并行交替采样数字化仪的样机,该实验样机的分辨率为14 b。利用安捷伦3352A高精度信号源作为实验的输入信号,输入一个信号幅度为1 V,频率为10 MHz的正弦信号,数字化仪样机的等效采样率为1 GSPS。校正模块分为误差测量和校正两个方面,首先用文献[10]的方法测定每路时间失配误差[rk]=[0,0.03,0.05,0.01],将测定时间误差数据保存用于随后校正模块。做两次实验,首先将四路未经校正的采样数据直接拼接,然后将校正后的采样数据拼接。分别用在线逻辑分析仪ChipScope将两次拼接后的数据上传给上位机,上位机通过Matlab对采样数据进行傅里叶变换分析其频谱。图9和图10分别为采样的4 096个样点未校正和校正后的频谱分析图。

由图9,图10可知,未校正前采样输出的频谱中含有杂散频谱线,这些在点[±f0+fkM]([f0=]10 MHz)处的谱线是由时间失配误差引起的,即在点[k*250±10 MHz]处,而250 MHz处的谱线是由偏置误差引起的。由图9可知校正前系统的无杂散动态范围SFDR=-50.5 dB,而校正后的SFDR=-70.8 dB。校正后系统的无杂散动态范围提高了20.3 dB,验证了该校正算法的有效性。由于校正模块只对时间失配误差进行了校正,并没有对其偏置和增益误差进行校正,当系统加入偏置误差和增益误差校正后将进一步提高系统的无杂散动态范围,校正效果更好。

4 结 论

本文设计了一种基于FPGA和ARM架构的高速数字化仪,采用并行交替采样技术构建了一个高速的数据采集系统。本文主要对四片ADC高速采样数据进行高速缓存和拼接,并对并行采样时间失配误差进行了频谱分析,利用Farrow结构的滤波器对时间失配误差进行了校正。实验结果表明,并行交替采样技术可以快速提高系统的采样速率,同时设计的Farrow结构的校正算法提高了系统的无杂散动态范围,系统运行可靠稳定。

参考文献

[1] 尹亮,周劼,姚军.多片ADC并行采集系统的增益误差补偿[J].现代电子技术,2007,30(17):170?171.

[2] 周浩,赵雷,李玉生,等.基于数字后处理算法的并行交替采样ADC系统[J].数据采集与处理,2010(4):537?543.

[3] 王凯,李小波,查淞.多片AD并行采样技术在软件无线电中的应用[J].电子技术应用,2010(3):57?59.

[4] 何丕雁,白泰礼.一种改进的正弦拟合时基失真估计算法[J].系统工程与电子技术,2003(3):359?361.

[5] BLACK W C HODGES D A. Time interleaved converter arrays [J]. IEEE journal of solid?state circuits, 1980, 15(6): 1022?1029.

[6] FARROW C W. A continuously variable digital delay element [C]// Proceedings of 1988 IEEE International Symposium on Circuits and Systems. Espoo: IEEE, 1988: 2641?2645.

[7] VOGEL C. The impact of combined channel mismatch in time?interleaved ADCs [J]. IEEE transactions on instrument & measurement, 2005, 54(1): 415?427.

[8] 张晓东.6GSPS数字示波器关键技术研究[D].成都:电子科技大学,2009.

[9] 洪萌,耿相铭.基于FPGA高速并行采样技术的研究[J].现代电子技术,2011,34(5):180?182.

[10] 朱子翰,吕幼新.时间交替采样系统的误差测量与FPGA实现[J].电子测量技术,2011,34(3):54?56.