3D NoC关键通信部件容错方法研究综述

2017-01-10欧阳一鸣孙成龙梁华国易茂祥黄正峰闫爱斌

欧阳一鸣,孙成龙,陈 奇,梁华国,易茂祥,黄正峰,闫爱斌

(1.合肥工业大学计算机与信息学院,安徽合肥 230009;2.合肥工业大学电子科学与应用物理学院,安徽合肥 230009)

3D NoC关键通信部件容错方法研究综述

欧阳一鸣1,孙成龙1,陈 奇1,梁华国2,易茂祥2,黄正峰2,闫爱斌2

(1.合肥工业大学计算机与信息学院,安徽合肥 230009;2.合肥工业大学电子科学与应用物理学院,安徽合肥 230009)

三维片上网络通过硅通孔(Through Silicon Via,TSV)将多层芯片进行堆叠,具有集成密度大,通信效率高等特点,是片上多核系统的主流通信架构.然而,工艺偏差及物理缺陷所引发的错误和TSV良率较低等因素,使得三维片上网络面临严重的故障问题.为保证通信效率,对三维片上网络关键通信部件进行容错设计必不可少.本文针对三维片上网络关键通信部件——路由器和TSV的故障和容错相关问题,从容错必要性、国内外研究现状、未来的研究方向和关键问题、以及拟提出的相关解决方案四个方面,展开深入探讨.为提高片上网络可靠性、保证系统高效通信提供一体化的解决方案.

集成电路;三维片上网络;容错;TSV;路由器加固;

1 引言

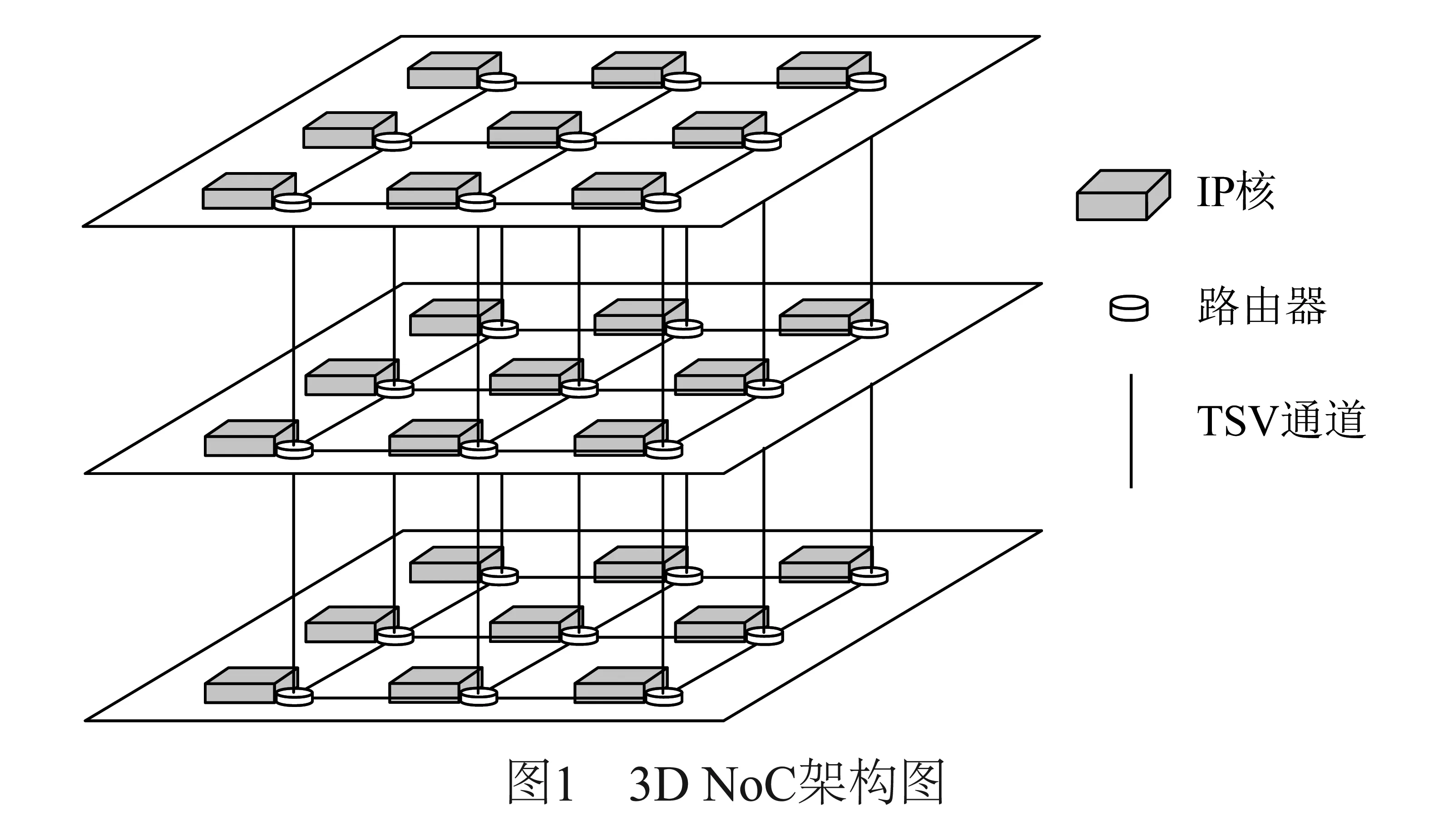

三维片上网络(Three Dimensional Network-on-Chip,3D NoC)[1~3]作为三维集成电路发展的产物,已经成为片上多核及众核系统的主流通信架构,其架构如图1所示.3D NoC通过硅通孔(Through Silicon Via,TSV)[4,5]将多个晶片(Die)在垂直方向进行堆叠,有效缩短了内连线长度,减少了延时、降低了功耗、提高了系统的性能,满足了多核系统对通信效率的需求.

然而,随着特征尺寸的缩小、集成密度的增加以及TSV的引入,都导致芯片面临着严重的可靠性问题[6~8].

ITRS2012[9]中预测,至2025年集成电路的特征尺寸将达到10nm,其工作电压将不断降低、工作频率逐步攀升、集成度持续提高,单个芯片所能集成的晶体管数目及芯片总面积呈现出不断增大的趋势,从而引起芯片内部发生更多的缺陷.主要体现在:(1)受制于制造工艺水平,芯片在生产过程中产生更多缺陷.(2)芯片在生命周期内,由于氧化、电路老化、电子迁移、电介质击穿、热载流子注入、负偏压温度不稳定性等原因,造成故障增多.(3)系统受到串扰、噪声、电磁干扰、α粒子撞击、宇宙辐射等因素影响,导致芯片功能短暂性失效.这些因素都将使得3D NoC面临严重的可靠性问题.

除了纳米工艺下集成电路所固有的可靠性问题外,作为层间通信媒介的TSV也严重影响着3D NoC中通信的可靠性.TSV因其具有高速、高集成密度、高带宽、低功耗等特性,成为3D NoC层间通信的主流方案[10,11],但是受到制造工艺的限制,TSV往往存在缺陷[12].文献[13,14]指出,由于绑定衬垫偏离标称位置所引起的未对准,以及TSV制造过程中产生的空隙、位移、表面氧化及机械应力所导致的随机开放性故障,是TSV失效的主要原因.图2展示了TSV的缺陷图.

由以上分析可知,纳米工艺下集成电路所固有的可靠性问题以及TSV故障问题,主要表现为通信部件发生永久或瞬时故障,从而导致数据的丢失或错误传送,直接影响3D NoC的通信性能.因此,探索提高通信部件可靠性的有效容错方法是3D NoC当前重要研究内容之一,国内外学者对此展开了一系列的探索和研究.

容错方法的设计主要归结为两类,一类是设计容错路由算法,绕过故障节点,保证各部件之间能够正常通信;另一类是通过架构上的改进,达到容错的目的.国内研究团队在容错路由算法方面主要有以下工作.文献[15]提出了基于局部故障块的容错路由算法,采用扩展的局部可靠性信息来指导三维mesh/torus网的容错路由,在每个平面内部对无故障节点分类,大大提高系统的计算能力和系统性能.文献[16]提出了一种无死锁的三维动态路由算法,以传统二维NoC奇偶拐弯模型为基础,将三维路由空间划分为8个象限,针对每个象限制定相应的路由策略,从而实现免死锁.文献[17]提出了基于故障链路缓存再利用的容错路由算法,该算法为每个通信节点增加4条自收发通道,并采用基于缓存再利用的透传机制,通过复用故障链路两端的正常缓存和通道来透传故障通道上的数据包,提高了数据包采用最优输出端口的概率.文献[18]针对3D mesh NoC中的节点故障,提出了一种无虚拟通道容错路由算法,该算法建立在3D防御区域基础之上.3D防御区域能够提供故障体的位置信息,根据防御区域提供的故障体位置信息,该算法可提前发现故障位置并改变转发端口,在实现容错的同时避免引入死锁.

国内研究团队在架构上改进方面主要有以下工作.文献[19]提出了一种故障通道隔离的低开销容错路由器架构,通过减少不必要的交叉开关及合理优化各个端口VC的数目来减小路由器整体开销.文献[20]提出一种可配置双向链路的容错偏转路由器,处理片上网络中的瞬态故障和永久性故障.文献[21]提出了3D Spidergon架构,在三维拓扑结构原型基础上,通过该拓扑的延时模型建立拓扑结构和延时时间的关系,并以此确定最小化延时时间条件下的拓扑结构.上述方案均是通过拓扑结构的设计,使得3D NoC具有一定的容错能力.

国外研究团队在容错路由算法方面主要有以下工作.文献[22]针对3D NoC中层间故障率大于层内故障率的现象,提出了一种仅针对层间TSV故障的XZXY路由算法,采用单向逐层递进式方法寻找无故障TSV.文献[23]中提出了一种混合预测容错路由机制HLAFT,根据源目的节点的相对位置优先采用最短路径传送数据包.文献[24]提出一种适应性容错路由算法FT-DyXYZ,对永久性链路故障进行容错,并且使用邻近的拥塞信息平衡负载.国外研究团队通过增加硬件架构来实现容错的方案主要有以下工作.文献[25]提出了增加一个检测网络来优化路由路径的方案,低开销的监控平台可以提供流量、故障等信息.文献[26]提出了通过增加冗余TSV来解决3D NoC层间通信部件故障问题的方案.文献[27]提出了一种双向通道buffer的容错NoC架构,利用通道buffer的可逆性提高网络性能,克服了故障链路的影响,降低了功耗.

以上研究针对3D NoC的通信部件故障问题,提出了相应的容错方案,提高了3D NoC的可靠性.但随着集成电路规模的增大,3D NoC中的故障呈现多样性、不确定性等特点,现有的容错方案出现了资源利用率不高或者开销过大等问题.基于此,本文针对3D NoC通信过程中的两个关键部件路由器和TSV涉及到相关容错问题,从以下几个方面展开论述:(1)容错必要性分析;(2)国内外已有方案的分析和总结;(3)未来研究方向和关键问题的提取;(4)拟提出的解决方案.通过本文的研究,建立一套比较完善系统化的容错体系,为提升三维集成电路可靠性提供理论方法和关键技术.

2 3D NoC中路由器容错技术研究

路由器作为NoC中最重要的通信部件之一,负责数据的存储与转发.因此提高路由器可靠性是实现系统高效通信的必要条件.基于此,本文首先探讨路由器内部用于数据存储的FIFO和转发阶段所涉及的交叉开关中的故障问题.

2.1 容错必要性

路由器由多个部件组成,包括输入FIFO、交叉开关及相应的仲裁逻辑.每个部件发生故障的概率也并非相同.文献[28]通过对路由器设计分析可知故障的分布与元件面积成正比关系,所含晶体管越多的元件,越容易出现故障.在45nm工艺下,对于5端口的基准路由器,如果FIFO大小为32-flit,那么FIFO和交叉开关面积分别占路由器总面积的94%和3.0%.FIFO大小为8-flit时,则占80%和10.5%.

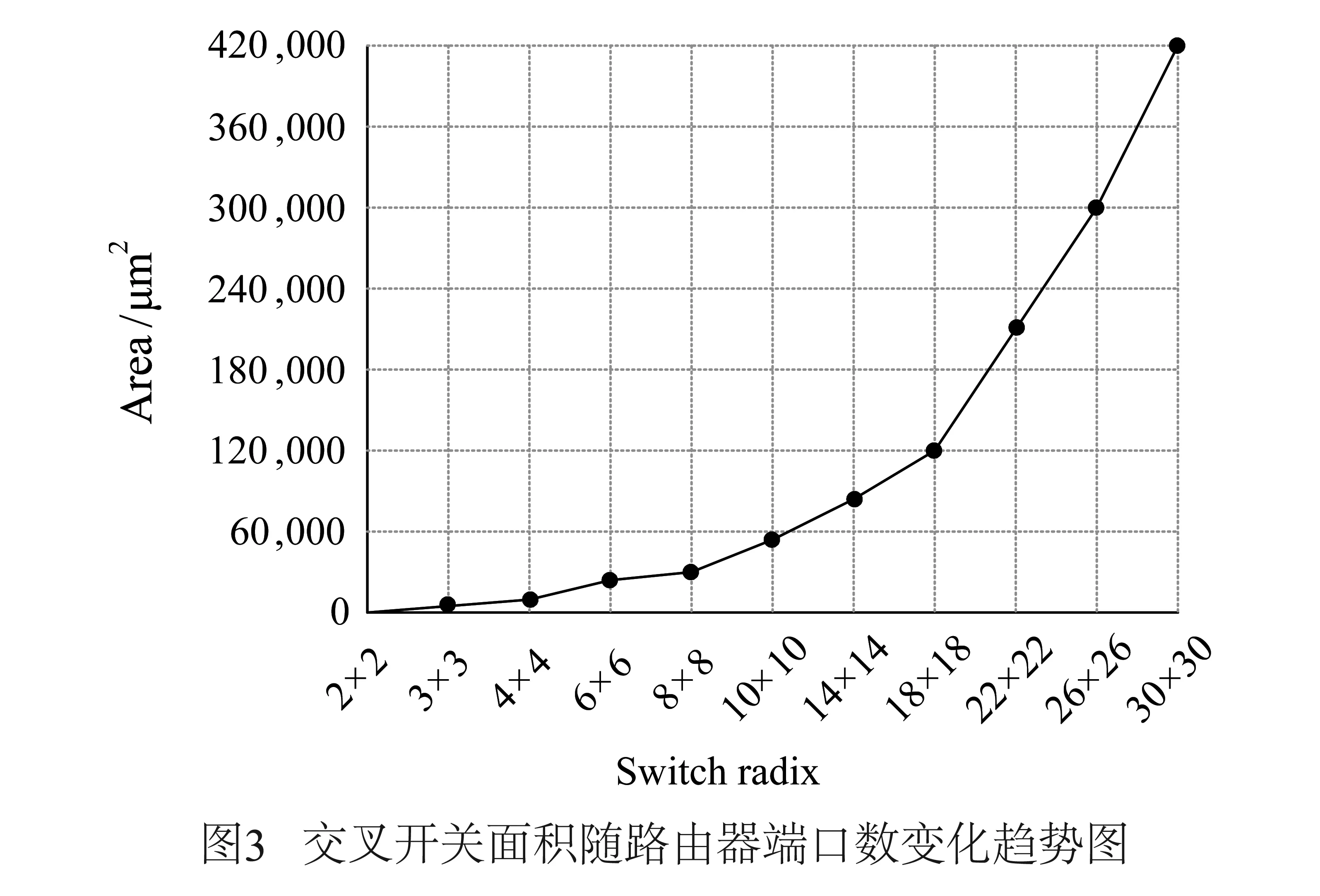

此外,文献[29,30]指出交叉开关面积随着路由器端口数的增加呈指数级增长,如图3所示.那么随着片上网络由2D向3D发展及网络拓扑结构的变化,使得路由器端口数目增加,从而导致交叉开关的面积急剧增长.

以上数据充分说明,在路由器面积中FIFO面积占绝大部分,其次为交叉开关.因此FIFO模块和交叉开关模块包含更多的晶体管,也就更容易出现故障.FIFO和交叉开关部件发生故障时均会导致路由器丢包,降低通信能力,严重影响系统性能,因此对路由器中的FIFO和交叉开关进行容错设计是提高路由器可靠性的关键,也是在实现片上系统中高效可靠通信时必须要解决的问题.

2.2 国内外研究现状分析与总结

2.2.1 针对FIFO故障的研究成果分析

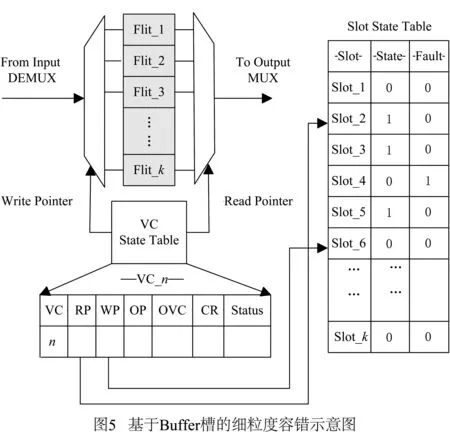

改变路由器的硬件结构是实现FIFO容错的一种有效方法.文献[31]提出了一种可靠性敏感的虚通道路由器,先孤立故障路由器,然后相邻路由器会回收往故障路由器发送数据的虚通道中的FIFO,对其进行重新分配.文献[32]针对路由器FIFO故障,提出了一种故障及拥塞感知的容错路由器架构.通过增加一个冗余的输入端口,当其它端口出现故障时启用冗余端口传输数据.文献[33,34]提出了虚通道共享的容错路由器架构,将部分端口的虚通道进行共享,对共享虚通道进行统一管理.当某个虚通道发生故障时,通过其他功能完好的虚通道存储数据,从而实现容错功能.这些容错方法都是将故障FIFO弃之不用,属于粗粒度容错.当若干个Buffer槽出现故障便将整个FIFO丢弃,显然没有最大程度利用可用资源.随后文献[28]针对Buffer槽故障进行了研究,通过控制FIFO的读写指针来跳过故障Buffer槽容错,有效地保证了系统可靠性,提高了系统性能并充分利用了Buffer资源.但是,路由器中FIFO是有最小容量要求的,它必须能够满足相邻路由器间信号的往返延时需求.因此,当剩余良好的Buffer槽数量少于最小容量时,仍保留FIFO功能显然不合理.上述方案分别通过粗细粒度的FIFO容错策略达到了较优的容错效果.

综上所述,探索片上路由器FIFO部件自适应容错方法,根据FIFO中Buffer槽的故障程度选择合适的容错策略,在保证系统高可靠性、提高通信效率的同时,实现对资源既合理又充分的利用是十分必要的.

2.2.2 针对交叉开关故障的研究成果分析

针对交叉开关故障,已有的容错方案中主要通过硬件冗余和链路旁路两种方法实现容错.文献[35]提出了一种双交叉开关的路由器架构,并在输入端口和交叉开关间添加了一个2×2的开关.根据交叉开关故障信息动态选择功能完好交叉开关工作,配置开关导通相应的输入和输出端口,从而实现容错.文献[36]针对交叉开关故障,提出一种三模冗余的容错方案和改进的带有错误检测和通知的流控机制,有效区分故障.文献[28]提出一种ViCis的路由器架构,增加了一条旁路总线.当交叉开关故障时,数据可以从旁路总线传输.但是总线具有分时复用的特性,当出现多方向数据同时刻竞争总线传输时,效率不高.此类方法,能够实现对交叉开关故障容错,但容错能力有限.

因此,未来在采用交叉开关内部硬件冗余机制来处理交叉开关故障时,要在保证容错能力的前提下尽量减小容错带来的额外开销.所以,应仅对核心部件设计冗余模块,根据内部模块故障信息,自适应地选择有效的数据通道进行通信.这样不仅能够实现容错,而且硬件开销相对较小.

2.3 未来研究方向和关键问题的提取

2.3.1 FIFO中基于故障粒度划分的容错方法研究

工艺尺寸缩减使芯片在制造过程中产生更多缺陷,系统规模的增大以及工作频率的上升,导致芯片对外界环境的刺激更加敏感,对芯片进行容错设计已刻不容缓.FIFO作为片上路由器中面积最大的部件容易发生故障,而且故障后将会严重影响系统通信性能,对FIFO的容错是提高片上网络通信可靠性的关键.因此,探究不同故障粒度条件下的容错方法,突破现有FIFO粗放式容错的限制,设计一种能够根据故障程度动态调整策略的高效容错方案是FIFO容错技术的发展趋势.

设计一种能够根据故障程度动态调整策略的高效容错方案首先需要通过FIFO故障粒度模型的建立与分析,对FIFO的故障程度进行粒度划分,进而在对不同粒度的故障选取相应的容错策略,在实现容错的同时,提高资源的利用效率.FIFO故障粒度模型的建立是自适应FIFO容错策略设计的前提条件.建立故障粒度模型要综合考虑导致FIFO故障的众多因素,包括故障发生的随机性、动态存储器误差失效机理、片上网络中FIFO存储特性以及Buffer槽之间故障发生的相互作用关系等.FIFO故障型对FIFO容错方案的形成以及性能评估具有指导性意义,因此建立合理的故障粒度划分的FIFO故障模型是FIFO自适应容错方法研究中的关键问题.

2.3.2 交叉开关中基于核心部件冗余加固的低开销、高可靠性研究

交叉开关是片上通信过程中数据转发的重要部件,其发生故障将对系统的延时及路由路径的正确性产生严重的影响.因此必须对交叉开关进行容错设计,以提高系统的可靠性.如何在开销和性能中间寻找一个有效的平衡点,保证在低开销的前提下满足交叉开关的性能需求,是需要考虑的问题.因此探究低开销、高可靠的交叉开关设计方案是在对片上网络路由器的容错设计中另一个发展趋势.

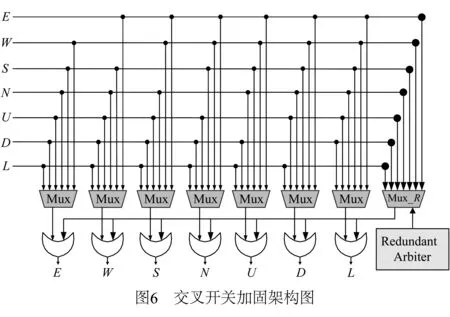

交叉开关中多路选择器作为数据转发过程的核心部件,直接影响交叉开关的可靠性.核心部件之间的相互协同工作是实现低开销、高可靠交叉开关容错架构的关键,如何处理多个输入端口数据对核心部件的信号请求和仲裁授权,直接影响系统的容错能力.因此综合考虑交叉开关的故障程度,分析部件之间的相互关系,建立冗余核心部件仲裁机制,高效合理的管理交叉开关各部件之间的协同工作,是交叉开关加固容错机制中需要解决的关键问题.

2.4 拟提出解决方案的设计

2.4.1 故障粒度划分的FIFO容错方法总体实现

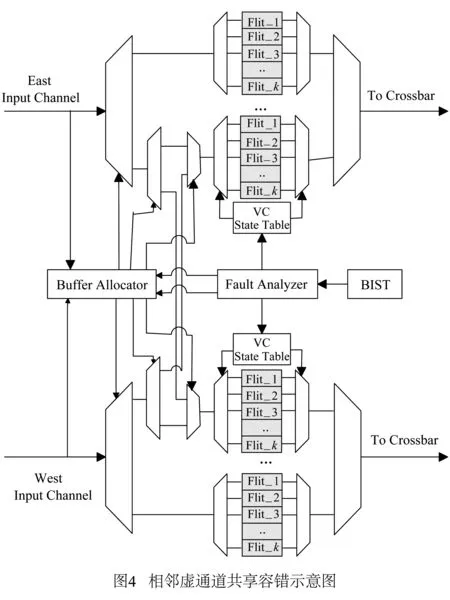

在FIFO容错方面,为了提高资源利用率,拟提出一种粒度划分的FIFO容错方案.当路由器中的FIFO发生粗粒度故障时,即可用的Buffer槽数不能满足相邻路由器间信号往返延时需求时,拟采取的方案是弃用整个FIFO,通过相邻端口虚通道共享实现容错.如图4所示,当系统通过BIST(Built-In Self-Test)模块检测出路由器东端口某个VC(Virtual Channel)出现故障时,将结果传送给Fault Analyzer模块进行故障类型分析,在确定了故障类型后,Fault Analyzer模块驱动相应信号有效,从而启动不同的容错方案.图4中Fault Analyzer模块将故障信息传向上游路由器及Buffer Allocator模块.路由器根据西端口共享VC的状态,通过Buffer Allocator模块决定是否响应数据包的请求.当FIFO中故障Buffer槽数目较少时,FIFO故障将被定义为细粒度故障,本文拟采取通过重配置读/写指针跳过故障Buffer槽的方法容错.如图5所示该方法通过在Slot状态表中增加Fault位来标示Buffer槽是否故障,Buffer控制器将通过Fault位以及当前读/写指针的状态合理处理FIFO的读写.通过基于粒度划分的自适应容错方案的设计,在实现FIFO容错的同时,保证了系统资源的高效利用.

2.4.2 核心部件冗余加固的低开销、高可靠交叉开关容错方案设计

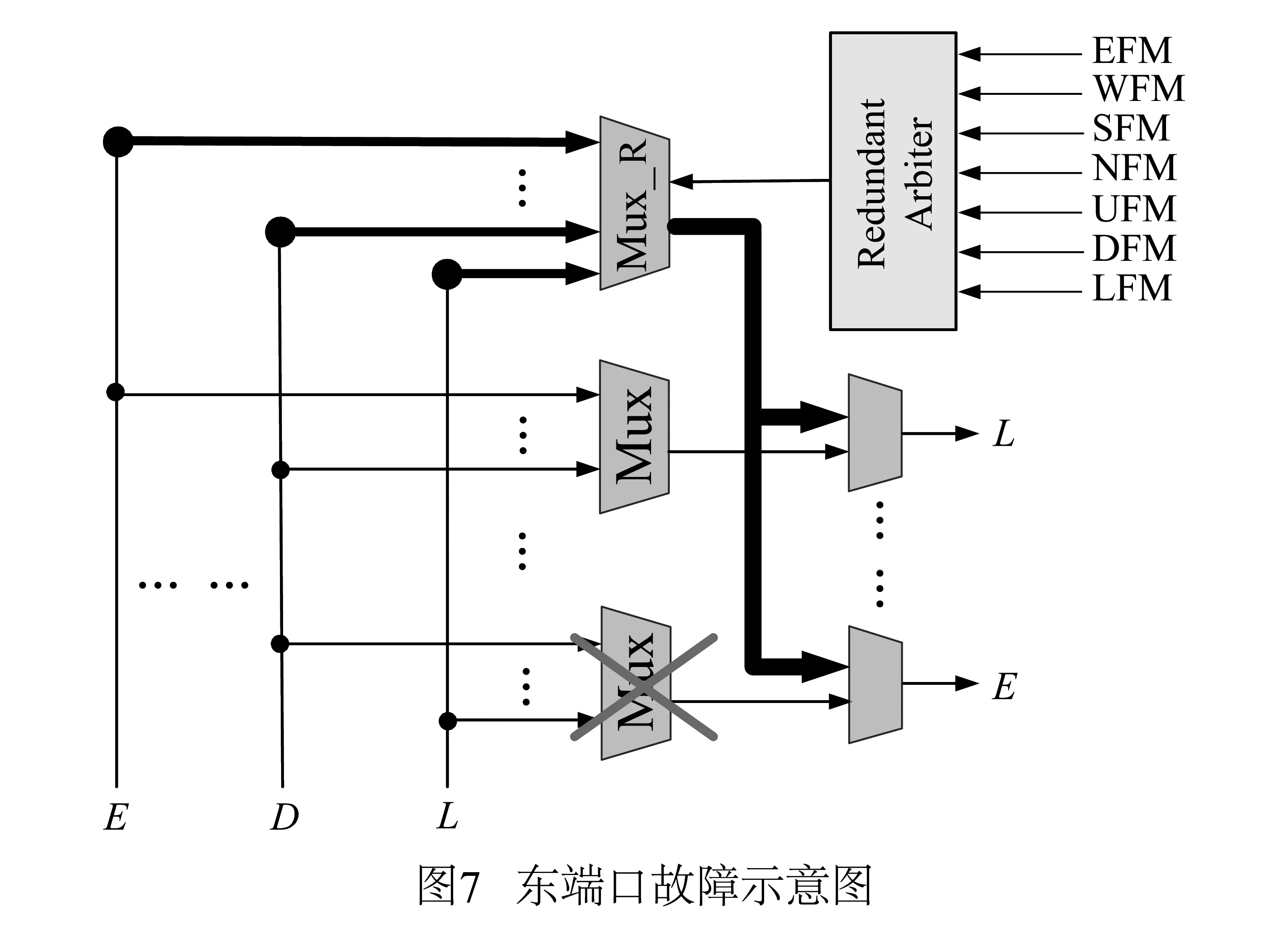

在交叉开关故障研究方面,拟采取图6所示的容错方案对交叉开关进行加固,即通过核心部件硬件冗余机制确保其与正常部件协同工作,其中核心部件为交叉开关内部的多路选择器.当核心部件发生故障时,拟使用冗余部件进行数据传输;无故障时,拟通过冗余部件加快数据转发的传输速度.具体是在传统的架构中添加一个冗余核心部件Mux-R,每个输入端口都与之相连接,通过一个冗余仲裁器(Redundant Arbiter)在交叉开关出现故障时,对Mux-R的请求信号进行仲裁和信号选通,负责数据请求的优先级分配.图7描述了交叉开关东端口故障示意图,东端口(E)接受来自南(S)、西(W)、北(N)、上(U)、下(D)、及本地(L)端口的请求.Arbiter的输入信号为多路选择器的故障信号(XFault Mux,XFM),其中X∈{E、S、W、N、U、D、L}.XFM请求信号在X端口的Mux出现故障时有效,即优先考虑正常的Mux进行数据传输,只有在出现故障时才使用Mux-R,也就是说PMux-X>PMux-R,其中P表示优先级.在数据传输过程中,如果某个Mux出现故障,则请求该端口输出的数据将无法传输,此时存储在FIFO中的数据就可以通过Mux-R进入相应的输出端口.当多个端口Mux出现故障,数据同时向Mux-R申请时,利用Redundant Arbiter采用优先级仲裁机制进行仲裁.通过以上的方法,能够有效地解决交叉开关故障问题,提高系统的可靠性,保证数据的有效传输.

3 3D NoC中TSV相关容错技术研究

在通信过程中,数据离开路由器后,便进入链路传输阶段.链路作为数据传输的载体,是另一关键通信部件,因此提高其可靠性也是实现系统高效通信的必要条件.然而作为层间通信媒介的TSV存在着产品良率较低等问题,故障TSV将导致层间某些垂直通道失效.因此,对TSV进行容错设计,降低由TSV故障带来的系统性能损失,尤为重要.

3.1 容错必要性

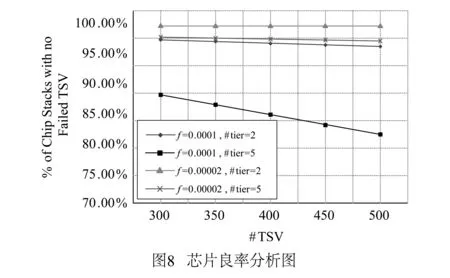

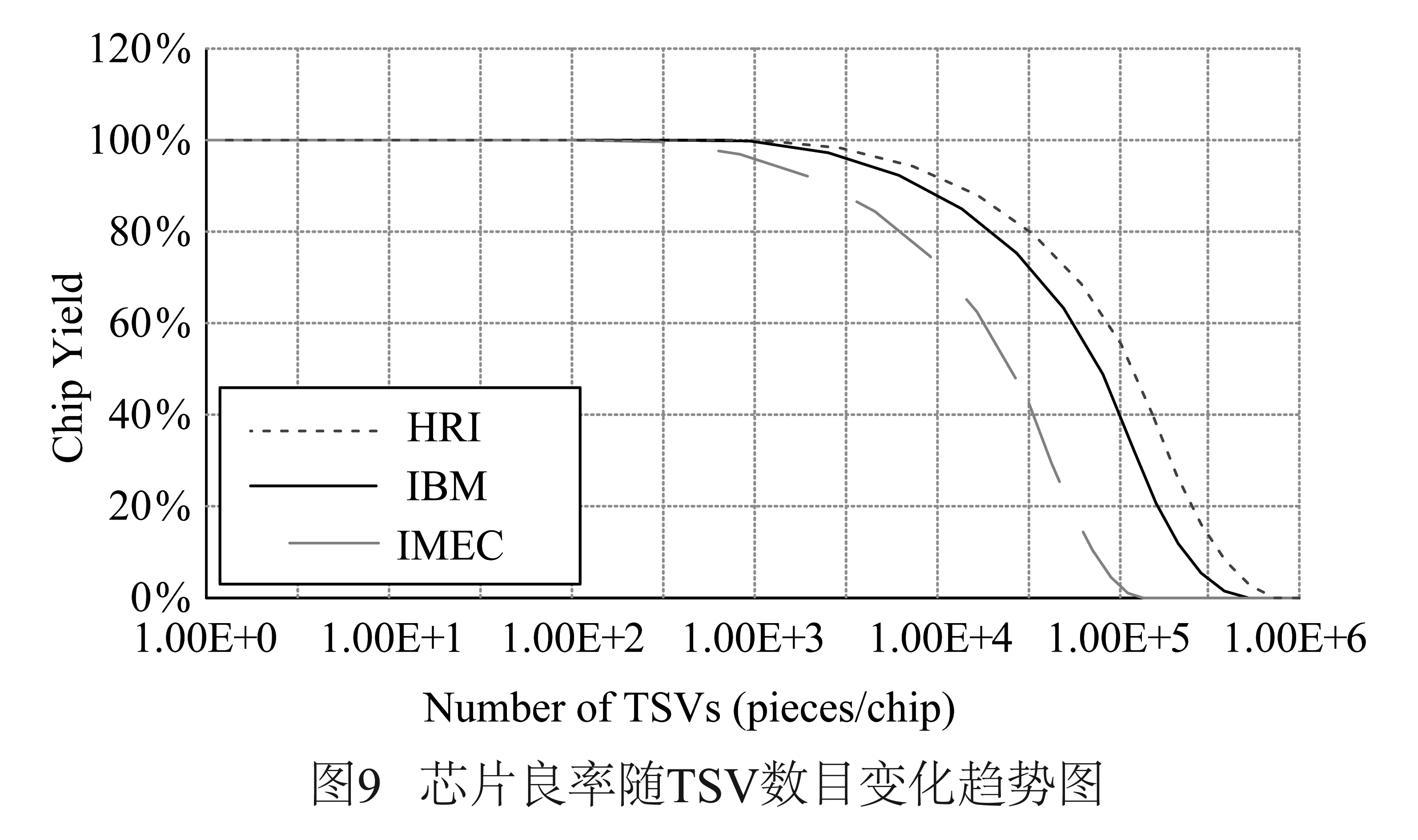

由制造缺陷导致TSV故障,影响了芯片的性能.且随着芯片集成密度的增加,TSV故障对芯片良率的影响随之增大[37].文献[26]分析了芯片封装良率与TSV数目以及堆叠层数之间的关系,如图8所示,其中f代表单个TSV位线的故障率,结合TSV的直径及绑定衬垫的大小,可判断f的取值大概在10-4到 10-5之间.#tier代表堆叠的层数,实际包含TSV的层数为#tier-1.由芯片绑定成功的概率公式(1-f)#TSV×(#tier-1)可知,随着TSV数目以及绑定层数的增加,芯片绑定的成品率将急剧下降.该结论在实际制造过程中也得到了印证,图9展示了HRI[38]、IMEC[39]以及IBM[40]所给出的TSV良率曲线图.从中可知,当TSV数目达到一定数量级后,芯片的成品率趋近于零.

3.2 国内外研究现状分析与总结

在TSV众多容错方案中,容错路由算法因其硬件开销小、资源利用率高以及容错能力强等特点,被广泛研究.文献[41]指出TSV的分布影响算法性能,因而在3D集成设计时应该综合考虑TSV的分布以及采用的算法.文献[42]针对不同TSV互连密度的3D NoC,提出六种稳定、简单且无死锁的路由算法,这些算法可维持非全互连3D NoC的系统性能.容错路由算法大多是在网络中查找可用TSV.当数据包到达某一节点后发现TSV故障,则采取偏转或丢包的策略,带来延时和功耗开销,增加了网络负担.基于上述问题,文献[43,44]针对非全互连3D拓扑提出一种分布式无死锁的路由算法Elevator First.该方案解决了死锁和TSV的寻找难题,但层间通信的路径不一定最优.

综上所述,探究基于最优TSV寻址的自适应容错路由算法,降低因TSV故障造成的非最短路由路径传输概率,使系统性能损失达到最小,这是TSV容错中的一个研究重点.

路由算法实现简单且容错能力强,能够很好地屏蔽故障TSV.但若仅是少数TSV位线发生故障,就绕过整个故障TSV通道,显然造成了资源的浪费.因此,需要细粒度的TSV容错方案,提高资源的利用率.冗余TSV以及TSV串行化传输是两种可行的容错方案[45].文献[46]提出了一种非专用的冗余TSV架构,不区分正常TSV和冗余TSV.当某根TSV位线发生故障时,剩余可用TSV通道均进行移位,绕过故障TSV位线.文献[26]提出了一种开销合理的TSV冗余架构.对于给定的TSV位线数目以及故障率,通过概率模型计算所需的冗余TSV数目,并在TSV两端通过配置多路选择器实现故障TSV的屏蔽.文献[47]提出了一种利用交换部件代替衬垫的容错架构,冗余TSV与正常TSV组成TSV阵列,通过配置交换部件,绕过故障TSV.

通过增加冗余TSV,能够提高封装良率且实现简单.但随着芯片规模的增大,冗余TSV带来的面积开销不容忽视[48],而且在平面层上起绑定作用的TSV衬垫所占据的面积也很大.为了减少冗余TSV位线的数目,有研究者提出了基于TSV串行化传输的容错方案.当少数TSV位线发生故障时,通过串行化操作实现故障屏蔽.文献[49]提出了一种基于移位寄存器的TSV串行化传输策略,并给出了一种串行TSV的布局方式.通过算法实现最优TSV通道布局以及串行化比率的选择,从而最大化实现传输线路的复用,减少面积和功耗开销.文献[50]提出了一种基于共享TSV-Hub的串行化传输策略.TSV-Hub由一组TSV阵列及相应的控制逻辑组成,通过TSV-Hub实现层间传输的串行化及容错.文献[51]根据层间TSV通道利用率不高的特点,提出了多个路由器共享TSV的机制.在保证系统性能的前提下,各路由器分时复用TSV进行层间传输,减少了TSV的数目.

以上分析可知,冗余TSV实现简单,容错效率高,然而存在着面积开销过大的缺陷.基于串行化传输的容错方案,不增加TSV位线的数目,但需要额外的时钟周期完成数据的传输,且发生故障的TSV位线数目较多时容错能力较差.基于此,探索一种冗余TSV与细粒度串行化传输相结合的自适应容错方法,在实现容错的同时保证资源的高效利用,是未来TSV容错中的一个发展方向.

3.3 未来研究方向与关键问题提取

3.3.1 TSV故障感知的最优路径选择方法研究

为解决自适应容错路由算法中非最短路径传输所引起的延时及功耗上升等问题,探索一种TSV故障感知的最优路径选择容错路由算法是TSV容错研究中一个重要的发展方向.TSV故障感知的最优路径选择容错路由算法首先应能高效地收集并共享TSV的故障信息,然后利用TSV状态及层间通信路径的全局信息,选取最优的中间TSV来完成故障下IP核的高效通信,从而使系统性能损失最小.在此路由算法实现中,中间TSV的选取尤为重要,因其选择结果的好坏将直接影响到层间通信的延时和功耗.因此,基于最优TSV寻址的高效自适应路由算法,构建合理的TSV评价模型,选择出通信路径中最优TSV,是算法实现中所遇到的关键问题.

3.3.2 基于自适应TSV控制器的高效容错策略研究

TSV容错如何根据TSV故障位线的数目合理地选择具体的容错策略,从而达到以最小的代价实现故障TSV的屏蔽,提高系统通信能力,是TSV容错研究中的另一个发展方向.

自适应容错能力的TSV冗余容错策略需要在路由器内部添加一个TSV控制器,TSV控制器可以冗余TSV共享与细粒度串行化传输机制相结合,根据故障TSV位线的数目,实现冗余TSV的映射以及串行化的传输.TSV控制器的一个关键功能就是实现竞争的公平仲裁及资源的合理分配,在控制过程中,既要考虑到当前故障的程度,又要协调其他部件对共享资源的占用.因此,在分配及仲裁过程中,需要综合考虑系统的容错能力、资源的利用效率及资源占用后对整体性能的影响,进而设计一种合理的分配及仲裁机制,是细粒度TSV容错策略设计中的一个关键问题.

3.4 拟提出的解决方案设计

3.4.1 TSV故障感知的最优路径选择方法总体实现

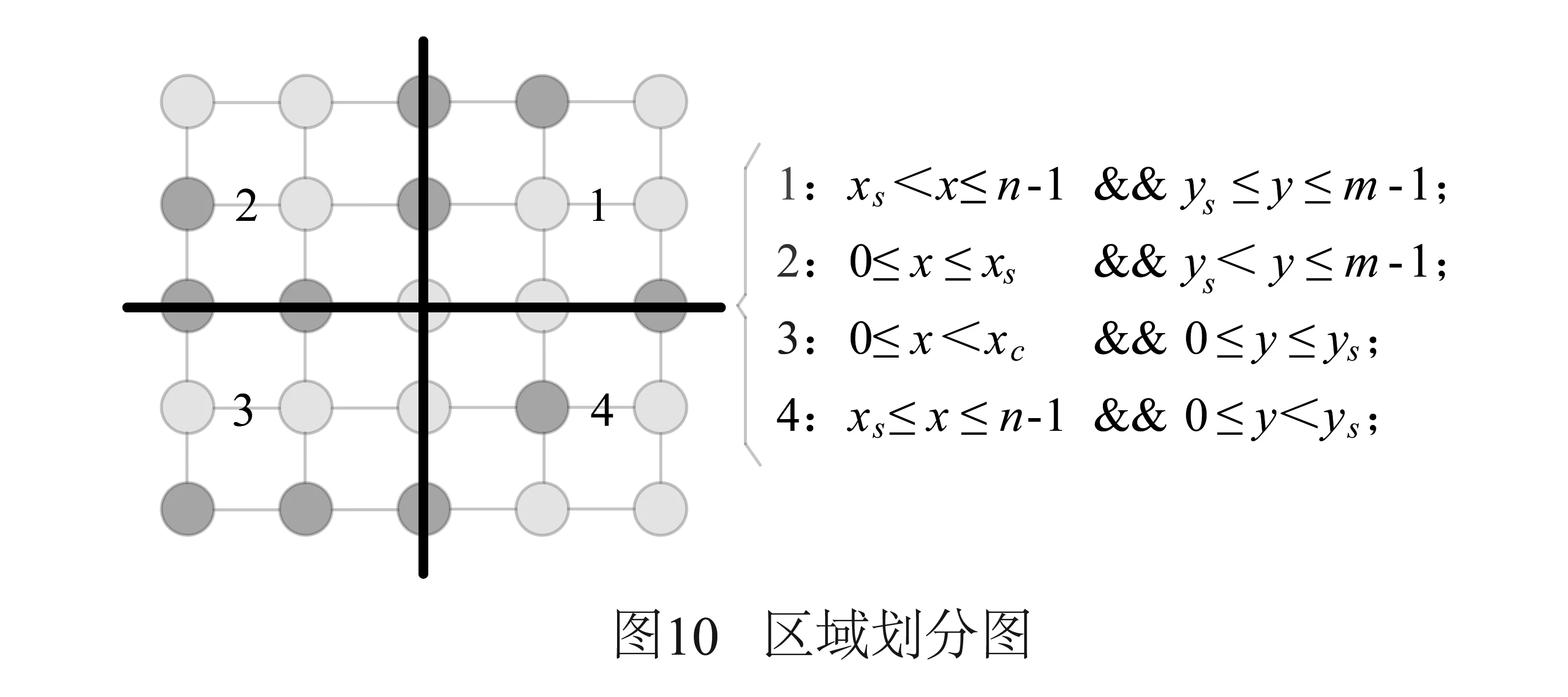

在非全互连三维架构下的容错路由算法方面,拟采取用一张TSV表来记录当前层所有TSV的可用状态.层间通信数据包在注入网络之前,先通过在本地TSV表中查找出最优TSV的地址,并将该TSV地址作为临时目的地址添加到数据包头部,数据包根据层内路由算法找到最优TSV后,再根据原目的地址判断数据的传输方向,直至到达目的地.当数据包需层间通信时,为查找到最优TSV的地址,我们在逻辑上将TSV表以源节点为中心划分成四个区域,如图10所示.若目的节点在源节点的上方,且映射到第四区域中,则查找最优TSV地址的具体顺序如图11所示.先查看源节点是否可用,若可用则直接将数据包向上传输,否则查找第四区域.为尽量保证数据包在最短路径上传输且提供路径多样性,在区域中查找时,根据目的节点在本层上的映射节点与源节点的相对距离由近至远逐一查找.若该区域中无可用TSV,则根据映射节点更偏向哪一区域再进一步查找,直至找到可用TSV.

3.4.2 基于自适应TSV控制器的高效容错方法设计

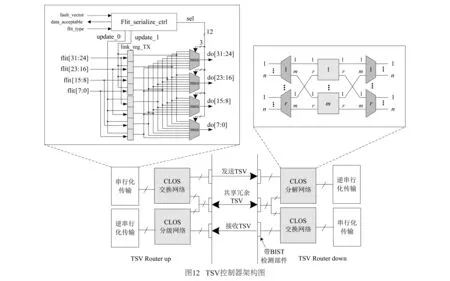

在TSV的细粒度容错方面,拟采用如图12所示的TSV控制器来实现自适应容错.其主要由三部分组成:BIST检测部件、三级CLOS交换网络以及串行化传输部件.首先由BIST检测单元对单向TSV通道进行检测,确定故障TSV位线的数目及位置;然后根据故障TSV位线信息及冗余TSV通道状态,选取相应的容错策略.具体过程如下,若故障TSV位线数目小于冗余TSV位线的数目,且冗余TSV通道处于空闲状态,则通过输入输出端口全互连的三级CLOS网络,将数据映射到单向TSV通道与冗余TSV通道的合集上,在接收端利用分解CLOS网络将数据还原;若故障TSV位线数目过多或冗余TSV通道被占用,则采用细粒度的串行化传输方案,保证数据的正常传输.将flit划分成相同大小的子flit块,并在发送端及接收端分别设置两个flit大小的寄存器阵列,实现flit的拆分及组装,然后以子flit块为基本单位,按照流水线的方式,保证可用TSV位线的高效利用.

4 总结与展望

芯片容错作为提高集成电路产品使用周期的有效方法,在学术界和工业界都得到了广泛的研究.针对3D NoC的容错设计目前已有诸多的研究,但是仍然存在着较多亟待解决的问题.本文对3D NoC容错设计面临的新挑战开展研究,探究通过3D NoC中低开销、高可靠的容错方法,来解决3D NoC中关键通信部件(路由器和TSV)的故障问题.文章从路由器中的Buffer、交叉开关中的关键部件、TSV容错路由算法以及TSV冗余控制器设计四个方面,首先分析总结国内外已有相关容错方案以及这些方案普遍存在的不足之处,其次探究了未来可容错性设计的发展方向与技术路线中的关键问题分析,最后给出了具体的拟解决方案.其中的关键问题包括如何在Buffer故障的情况下高效合理的利用剩余的可用资源;如何设计低开销、高可靠的交叉开关容错架构,来解决交叉开关内部故障问题;如何在非全互连3D NoC架构中寻找最优TSV进行通信,以及探究冗余TSV与细粒度串行化传输相结合的通信自适应容错方法.通过本文的相关研究,为片上网络建立系统化的容错体系提供参考,同时也为提升三维集成电路可靠性提供理论方法和关键技术.

传统单一的容错方法都存在资源利用率不高或开销过大等问题,针对故障位置和故障程度的不同,动态自适应地选择高效可靠的容错策略将是未来片上网络容错领域一个重要的发展方向.

[1]XIANG D,Chakrabarty K,Fujiwara H.Multicast-based testing and thermal-aware test scheduling for 3D ICswith a stacked network-on-chip[J].IEEE Transactions on Computers,2015,(99):1.

[2]Radfar F,Zabihi M,Sarvari R.Comparison between optimal interconnection network in different 2D and 3D noC structures[A].27th IEEE International System-on-Chip Conference (SOCC)[C].Las Vegas,NV:IEEE,2014.171-176.

[3]Elmiligia H,Gebalib F,El-Kharashi W M.Power-aware mapping for 3D-NoC designs using geneticalgorithms[J].Procedia Computer Science,2014,34:538-543.

[4]EghbalA,YaghiniP M,YazdiS S,BagherzadehN.TSV-to-TSV inductive coupling-aware codingscheme for 3D network-on-chip[A].IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT)[C].Amsterdam:IEEE,2014.92-97.

[5]Sepulveda J,Gogniat G,Florez D,Diguet J-P,Pires R,Strum M.TSV protection:towards secure 3D-MPSoC[A].IEEE 6th Latin American Symposium onCircuits & Systems (LASCAS)[C].Montevideo:IEEE,2015.1-4.

[6]Ren Y,Liu L,Yin S,Wu Q-H,et al.A vlsi architecture for enhancing the fault tolerance of NoC using quad-spare mesh topology and dynamic reconfiguration[A].International Symposium on Circuits and Systems[C].Beijing:IEEE,2013.1793-1796.

[7]Radetzki M,Feng C C,Zhao X,Jantsch A.Methods for fault tolerance in networks-on-chip[J].ACM Computing Surveys,2013,46(1):1-38.

[8]Hernandez C,Roca A,Flich J,et al.Fault-tolerant vertical link design for effective 3D stacking[J].IEEE Computer Architecture Letters,2011,10(2):41-44.

[9]OSADA T,GODWIN M.International technology roadmap for semiconductors[EB/OL].http://www.itrs.net/.1999-07-08/1999-07-09.

[10]Ye H,Chi M,Huang S H.A design partitioning algorithm for 3-D integrated circuits[A].IEEE Int.Symp.ComputCommunControl Autom[C].Tainan:IEEE,2010.229-232.

[11]Hsu M K,Balabanov V,Chang Y W.TSV-aware analytical placement for 3-D IC designs based on a novel weighted-average wirelength model[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2013,32(4):497-509.

[12]Loi I,Mitra S,Lee T H,Fujita S.Benini L.A low-overhead fault tolerance scheme for TSV-based 3D network on chip links[A].International Conference on Computer-Aided Design[C].San Jose:IEEE,2008.598-602.

[13]Patti R.Impact of wafer-level 3D stacking on the yield of ICs[DB/OL].Future Lab.Int.,2007-09-07.

[14]Jiang L,Xu Q,Eklow B.On effective through-silicon via repair for 3-D-stacked ICs[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2013,32(4):559-571.

[15]向东,陈爱,孙家广.基于局部故障块的3维mesh/torus网的容错路由[J].计算机学报,2004,27(5):611-618. Xiang Dong,Chen Ai,Sun Jia-guang.Fault-tolerant routing in 3D meshes/tori based on locally formed fault blocks[J].Chinese Journal of Computers,2004,27(5):611-618.(in Chinese).

[16]虞潇,李丽,张宇昂,潘红兵,王佳文,韩平.一种面向功耗免死锁三维全动态3D NoC路由算法[J].电子学报,2013,41(2):329-334. Yu Xiao,Li L,Zhang Yu-ang,Pan Hong-bing,Wang Jia-wen,Han Ping.A power-aware dead lock avoid three-dimensionalfull-adaptive routing algorithm for 3D NoC[J].Acta Electronica Sinica,2013,41(2):329-334.(in Chinese)

[17]张士鉴,韩国栋,沈剑良,柯璘.基于故障链路缓存再利用的NoC容错路由算法[J].计算机辅助设计与图形学学报,2014,26(1):131-137. Zhang Shi-jian,Han Guo-dong,Shen Jian-liang,KeLing.Fault-tolerant routing algorithm of NoC based on buffer reuse of faulty links[J].Journal of Computer-aided Design & Computer Graphics,2014,26(1):131-137.(in Chinese)

[18]王宇飞,李光顺,吴俊华.无虚拟通道的3D NoC Zone Defense容错路由算法[J].计算机应用研究,2016,33(1):205-209. Wang Yu-fei,Li Guang-shun,Wu Jun-hua.3D NoC zone defense fault-tolerant routing algorithm without virtual channels[J].Application Research of Computers,2016,33(1):205-209.(in Chinese)

[19]欧阳一鸣,陈义军,梁华国,易茂祥,李建华.一种故障通道隔离的低开销容错路由器设计[J].电子学报,2014,42(11):2142-2149. Ouyang Yi-ming,Chen Yi-jun,Liang Hua-guo,Yi Mao-xiang,Li Jian-hua.Design of a low-overhead fault channel isolated fault-tolerant router[J].Acta Electronica Sinica,2014,42(11):2142-2149.(in Chinese)

[20]冯超超,张民选,李晋文,戴艺.一种可配置双向链路的片上网络容错偏转路由器[J].计算机研究与发展,2014,51(2):454-463. Feng Chao-chao,Zhang Ming-xuan,Li Jin-wen,Dai Yi.A fault-tolerant deflection router with reconfigurable bidirectional link for NoC[J].Journal of Computer Research and Development,2014,51(2):454-463.(in Chinese)

[21]Lei Zhou,Ning Wu,Fen Ge.3-D spidergon:3-D topology of delay optimization for networks-on-chip[J].Transactions of Nanjing University of Aeronautics & Astronautics,2011,28(4):372-378.

[22]Akbari S,Shafieey A,Fathy M,Berangi R.AFRA:A low cost high performance reliable routing for 3d mesh NoCs[A].Design,Automation & Test in Europe Conference & Exhibition[C].Dresden:IEEE,2012.332-337.

[23]Ahmed A B,et al.Graceful deadlock-free fault-tolerant routing algorithm for 3D network-on-chip architecture [J].Elsevier Journal of Parallel and Distributed Computing,2014,74(4):2229-2240.

[24]Jouybari H N,Mohammadi K.A low overhead,fault tolerant and congestion aware routing algorithmfor 3D mesh-based network-on-chips[J].Microprocessors and Microsystems,2014,38(8):991-999.

[25]Rahmani A M,Vaddina K R,Atifk L,Liljeberg P,Losilaj P,Enhunenh T.High-performance and fault-tolerant 3D NoC-bus hybrid architecture using ARB-NET based adaptive monitoring platform[J].IEEE Transactions on Computers,2014,61(3):734-747.

[26]Hsieh A C,Hwang T T,Chang M T.TSV redundancy:architecture and design issues in 3D IC[A].Design,Automation & Test in Europe Conference & Exhibition[C].Dresden:IEEE,2010.166-171.

[27]Ditomaso D,Kodi A,Louri A.QORE:A fault tolerant network-on-chip architecture with power-efficient quad-function channel (QFC) buffers[A].IEEE 20th International Symposium High Performance Computer Architecture (HPCA) [C].Orlando,FL:IEEE,2014.320-331.

[28]Deorio A,Fick D,et al.A reliable routing architecture and algorithm for NoCs[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and System,2012,31(5):726-739.

[29]Pullini A,Angiolini F,Murali S.et al.Bringing NoCs to 65 nm[J].IEEE Micro,2007,27(5):75-85.

[30]Passas G,Katevenis M,Pnevmatikatos D.Crossbar NoCsare scalable beyond 100 nodes[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and System,2012,31(4):573-585.

[31]Neishaburi M H,Zilic Z.Reliability aware NoC router architecture using input channel buffer sharing[A].Great Lake Symposium on VLSI[C].New York:ACM,2009.511-516.

[32]欧阳一鸣,张一栋,梁华国,黄正峰.三维片上网络故障及拥塞感知的容错路由器设计[J].电子学报,2013.41(5):912-917. Ouyang Yi-ming,Zhang Yi-dong,Liang Hua-guo,Huang Zheng-feng.A fault-tolerant design of faults and congestion-aware router in three-dimensional network-on-chip[J].Acta Electronica Sinica,,2013.41(5):912-917.(in Chinese)

[33]LATIF K,et al.A novel topology-independent router architecture to enhance reliability and performance of networks-on-chip[A].IEEE IntSymp on Defect and Fault Tolerance in VLSI and Nanotechnology Systems[C].Vancouver:IEEE,2011.454-462.

[34]Latif K,Rahmani A M,Liang G,et al.PVS-NoC:partial virtual channel sharing NoC architecture[A].International Euromicro Conference[C].New York:IEEE,2011.470-477.

[35]Zhang Y,Morris J,Kodi A.Design of a performance enhanced and power reduced dual-crossbar network-on-chip (NoC) architecture[J].Microprocessors and Microsystems,2011,35(2):110-118.

[36]Ghiribaldi A,Strano A,Favalli M,et al.Power efficiency of switch architecture extensions for fault tolerant NoC design[A].International Green Computing Conference[C].San Jose:IEEE,2012.1-6.

[37]Garrou P,Bower C,Ramm P.Handbook of 3D Integration:Technology and Application of 3D Integrated Circuits(1-2)[M].Weinheim:WILEY-VCH Verlag GmbH & Co.KGaA,2008.

[38]Miyakawa N,et al.A 3D prototyping chip based on a wafer-level stacking technology[A].Asia and South Pacific Design Automation Conference[C].Yokohama:IEEE,2009.416-420.

[39]Swinnen B,Ruythooren W,Moor P D,et al.3D integration by cu-cuthermo-compression bonding of extremely thinned bulk-Si die containing 10μm pitch Through-Si Vias[A].International Electron Devices Meeting[C].San Francisco:IEEE,2006.1-4.

[40]A Topol,La Tulipe D C,Shi L,S Alam M,et al.Enabling SOI based assembly technology for three-dimensional integrated circuits[A].International Electron Devices Meeting[C].San Francisco:IEEE,2005.352-355.

[41]Kim D H,Athikulwongse K,Lim S K.Study of through-silicon-via impact on the 3-D stacked IC Layout[J].IEEE Transactions on VLSI Systems,2013,21(5):862-874.

[42]H Ying,A Jaiswal,T Hollstein.Deadlock-free generic routing algorithms for 3-Dimensional networks-on-chip with reduced vertical link density topologies[J].Journal of Systems Architecture,2013,59(7):528-542.

[43]Bahmani M,Sheibanyrad A,Pétrot F,et al.A 3D-NoC router implementation exploiting vertically-partially-connected topologies [A].IEEE Computer Society Annual Symposium on VLSI[C].Los Alamitos:IEEE Computer Society,2012.9-14.

[44]Dubois F,Sheibanyrad A,Pétrot F,et al.Elevator-first:a deadlock-free distributed routing algorithm for vertically partially connected 3D-NoCs[J].IEEE Transactions on Computers,2011,62(3):609-615.

[45]Pasca V,Anghel L,Benabdenbi M.Error resilience exploration in 3D systems[A].IEEE International On-Line Testing Symposium[C].Chania:IEEE,2013.1-5.

[46]Kang U,Chung H J.8 Gb 3-D DDR3 DRAM using through-silicon-via technology[J].IEEE Journal of Solid-State Circuits,2010,41(1):111-119.

[47]Zhang J,Yu L,Yang H.Self-test method and recovery mechanism for high frequency TSV array[A].IEEE/IFIP International Conference on VLSI and System-on-Chip[C].Hong Kong:IEEE,2011.260-265.

[48]Pasca V,Anghel L,Rusu C,Locatelli R,Coppola M.Error resilience of intra-die and inter-die communication with 3d spidergon STNoC[A].Design,Autumation& Test in Europe Conference[C].Dresden:IEEE,2010.275-278.

[49]Pasricha S,et al.A framework for TSV serialization-aware synthesis of application specific 3D Networks-on-Chip[A].International Conference on VLSI Design[C].Hyderabad:IEEE,2012.268-273.

[50]Miller F,Wild T,Herkersdorf A.Virtualized and fault-tolerant inter-layer-links for 3D-ICs[J].Microprocessors and Microsystems,2013,37(8):823-835.

[51]Liu C,Zhang L,Han Y,Li X W.Vertical interconnects squeezing in symmetric 3D mesh Network-on-Chip[A].Asia and South Pacific Design Automation Conference[C].Yokohama:IEEE,2011.357-362.

欧阳一鸣 男,1963年生,博士,教授,中国计算机学会高级会员,容错计算专业委员会委员.研究方向:片上网络(NoC)与片上系统(SoC),嵌入式系统的综合与测试,数字系统设计自动化.

E-mail:oyymbox@163.com

孙成龙 男,1993生,硕士研究生,研究方向:片上系统以及片上网络容错方法.

E-mail:scl0313@163.com

陈 奇 男,1990年生,硕士研究生,研究方向:片上系统以及片上网络容错方法.

E-mail:chenqi-swj@163.com

梁华国 男,1959年生,教授,博士生导师,中国计算机学会容错计算专业委员会委员,研究方向:嵌入式系统综合与测试、数字系统设计自动化、ATPG 算法与分布式控制等.

E-mail:huagulg@hfut.edu.cn

易茂祥 男,1964年9月出生,博士,教授,IEEE会员,硕士生导师.主要研究方向:超大规模集成电路(VLSI)综合与测试、VLSI可靠性、计算机应用技术.

E-mail:mxyi126@126.com

黄正峰 男,1978年生,博士,副教授,硕士生导师,中国计算机学会容错计算专业委员会委员.主要研究方向为嵌入式系统综合与测试、数字集成电路的硬件容错、星载SoC芯片的抗辐射加固.

E-mail:hanson-hfut@sina.com

闫爱斌 男,1983年生于吉林白城,2015年获得合肥工业大学计算机应用技术专业工学博士学位,现为安徽大学计算机科学与技术学院讲师.研究方向为纳米集成电路软错误率分析和星载系统芯片SoC的抗辐射加固.

E-mail:abyan@mail.ustc.edu.cn

Fault-Tolerant Method of Critical Communication Components in 3D NoC:A Review

OUYANG Yi-ming1,SUN Cheng-long1,CHEN Qi1,LIANG Hua-guo2, YI Mao-xiang2,HUANG Zheng-feng2,YAN Ai-bin2

(1.SchoolofComputerandInformation,HefeiUniversityofTechnology,Hefei,Anhui230009,China; 2.SchoolofElectronicScience&AppliedPhysics,HefeiUniversityofTechnology,Hefei,Anhui230009,China)

3D NoC stacking the multi-chips with TSV has many advantages,such as high integration density and high communication efficiency.It is the mainstream of communication architecture on multi-core on-chip systems.However,due to the process variation,physical defects and low yield of TSV,3D NoC is facing serious fault problems.It is essential to design a fault-tolerant mechanism for 3D NoC to ensure the efficiency of communication.In this paper,we focus on the failure and fault-tolerance issues of the critical communication components (routers and TSVs) in 3D NoC.From the description of fault-tolerance necessity,researches situation at home and abroad,future research directions,key issues and the proposed solutions,we conduct an in-depth discussion.Thus,we provide integrated solutions for improving the reliability of NoC and ensuring efficient communication system.

integrated circuit; 3D NoC; fault tolerant; through-silicon-via; router reinforcement

2015-05-11;

2016-03-04;责任编辑:梅志强

国家自然科学基金(No.61474036,No.61274036,No.61371025,No.61574052);安徽省自然科学基金(No.1508085MF117)

TP302

A

0372-2112 (2016)12-3053-011

��学报URL:http://www.ejournal.org.cn

10.3969/j.issn.0372-2112.2016.12.034