一种高增益大带宽的增益自举型折叠共源共栅放大器设计

2017-01-07唐海林赵宗佑于跃宝

王 停,唐海林,赵宗佑,于跃宝

(1.中国人民解放军93756部队 特设教研室,天津 300131;2.河北工业大学 电子信息工程学院,天津 300401)

一种高增益大带宽的增益自举型折叠共源共栅放大器设计

王 停1,2,唐海林1,赵宗佑1,于跃宝1

(1.中国人民解放军93756部队 特设教研室,天津 300131;2.河北工业大学 电子信息工程学院,天津 300401)

提出了一种应用于高速高精度流水线 ADC中的高增益大带宽的增益自举型全差分折叠共源共栅放大器.放大器采用0.18 m 1P6M CMOS工艺.通过仔细的设计运放的单位增益带宽和极零点改善其闭环稳定性.仿真结果表明:放大器的直流增益为93 dB,单位增益带宽为1.8GHz,在输出共模电压范围为0.6V~1.2V内,放大器的直流增益大于88 dB.整个芯片的版图面积为96 m×120 m.

共源共栅;增益自举;放大器;开关电容;共模反馈;流水线ADC

0 引言

运算放大器是数模混合信号集成电路中的十分关键的模块,尤其是在高速高精度模数转换器中[1].运放的增益、带宽、功耗、共模输出范围、失调电压、转换速率和稳定性直接决定着转换器的性能.运放的增益和带宽决定了信号在流水线模数转换器(Pipelined ADC)中能否精确传递,运放的静态功耗决定了Pipelined ADC的整体功耗,其噪声决定了Pipelined ADC的采样电容,进而决定了其转换速度.随着CMOS工艺的进步,晶体管的特征尺寸不断下降,MOS管的输出阻抗逐渐减小[2],晶体管的本征增益也随之逐渐降低.即使多级放大器也很难实现大于60 dB的直流增益,并且多级放大器的稳定性比较差,带宽很小.因此多级放大器无法满足高速高精度ADC对高增益大带宽的放大器的要求.设计者提出了很多新技术,例如增益自举结构、共源共栅结构.其中,套筒式共源共栅结构能够实现很高的直流增益和大的闭环带宽,但是其输出摆幅很小[3].折叠共源共栅运算放大器需要消耗较大的功耗,但是其输出摆幅和输入共模范围较大[4].因此在高速高精度Pipeline ADC中,通常采用带有增益自举结构的折叠共源共栅放大器.

提出了一种采用双输入对的增益自举型折叠共源共栅放大器.因为在运放共享结构的Pipelined ADC中,运放通常在2个时钟相位交替工作,没有时间进行复位.在后一级进行闭环放大时,运放的输入端会保留前一级闭环放大时输入端残留的电荷.这会严重恶化ADC的性能.采用双输入对结构时,2个输入对在2项非交叠时钟的控制下交替工作,1个输入对进行闭环放大时,另一个输入对进行复位.而在下1个相位进行放大时,就不会受到上一级闭环放大时残余电荷的影响[5].此放大器分别采用开关电容和单管共模反馈来控制输出共模电压,不会引入额外的功耗.此运放中的2个辅助运放用来提高共源共栅管的跨导.在不增加系统极零点的情况下实现了很大的增益和带宽.

1 电路结构

1.1 整体结构

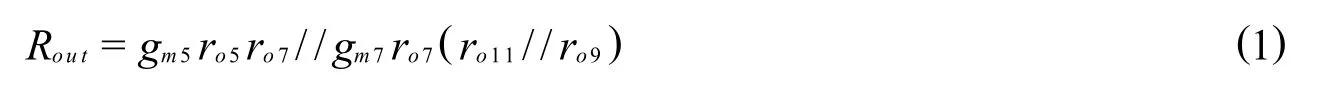

图1是双输入对折叠增益增强型折叠共源共栅放大器原理图.此放大器由3个放大器组成:主放大器、辅助放大器A1和A2.在不采用辅助放大器A1和A2时,主放大器的输出阻抗为

当采用辅助放大器时,其输出阻抗为

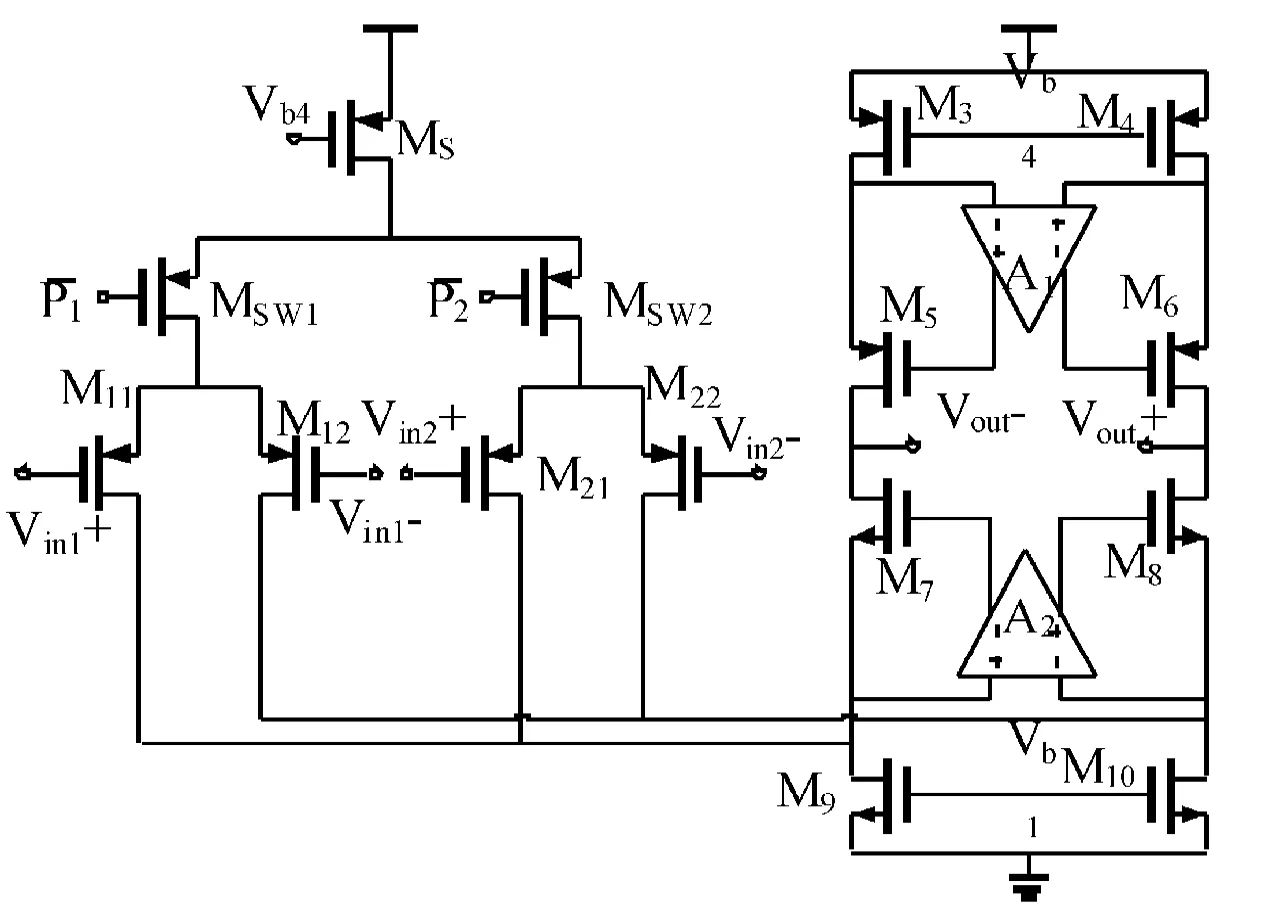

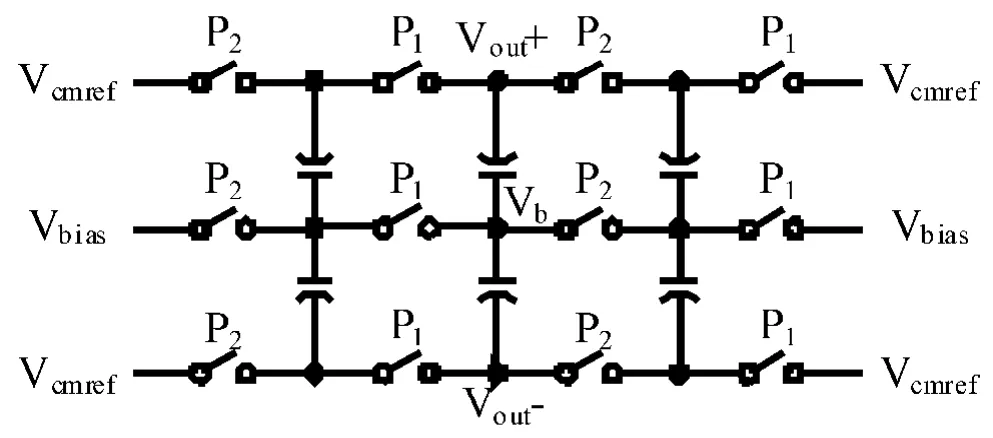

1.2 辅助放大器的设计

辅助放大器分别采用NMOS和PMOS管差分输入对.图2和图3分别为其电路结构.在设计辅助放大器时必须注意极零点对耦合现象,如果极零点对出现在闭环系统地 3 dB带宽内,则会使系统的建立时间变长.在增益自举结构中,极零点对出现在辅助运放的单位增益频率附近,提高极零点对的发生频率可以避免它对建立时间的影响,但如果提高到主运放次级点附近时,会使运放出现不稳定,因此辅助运放的设计必须满足

图1 双输入对折叠增益增强型折叠共源共栅放大器原理图Fig.1 Theschematic dual-input folded cascodeGain-Boosted op-amp

图2 辅助放大器A1Fig.2 Auxiliary amplifier A1

图3 辅助放大器A2Fig.3 Auxiliary amplifier A2

由于此运放是用在开关电容电路中,放大器的建立过程一般分为线性建立和压摆过程,运放的压摆过程直接影响着系统的响应速度和功耗.例如在Vin+和Vin-端输入一个较大的阶跃电压,则M 11管截止,电流全部流入晶体管M 12,此时M 8的漏电流变小,而M 6的漏电流对其输出端的负载电容充电,输出电压升高.同理Vout-端的负载电容放电,输出电压降低,运放工作在压摆过程。当输入端的电压降到一定程度后,M 11导通,放大器进入线性放大过程。通常情况下要合理设置放大器的压摆区和线性建立区,使得响应时间最短,通常将建立时间的1/3分配给压摆区,进而计算出各支路所需的偏置电流.

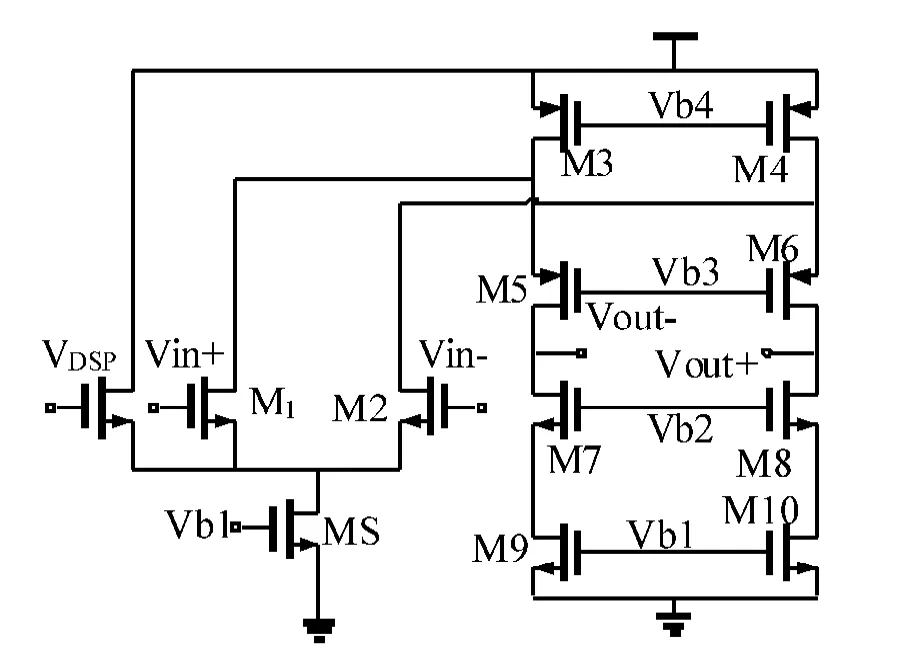

1.3 共模反馈电路

共模反馈电路是保证放大器正常工作的基本电路之一.折叠共源共栅放大器的上端是电流源,下端是电流漏,它们的饱和电流稍有偏差,输出端工作点电压就以大幅度波动,使得饱和电流较大的管子进入不饱和区,放大器不能正常工作.共模反馈电路检测输出共模电压并与设定值进行比较,再通过放大器放大这个误差电压,然后调节电流源或者电流漏的偏置电压,使得它们的饱和电流向着使输出电压接近参考电压的方向变化.

共反馈电路有有源和无源之分,使用无源的开关电容共模反馈电路,如图4所示,开关电容共模反馈电路允许的输出电压变化范围大,电路实现简单,只要定时刷新电容的电压即可正常工作.图4采用的开关电容共模反馈电路可以保证运放在2个相位都能正常工作,因为电路有两组充点电容给反馈电容充电[6].P1时,左边两组电容接在共模反馈电路中,保证运放共模反馈正常工作,右侧一组电容再充电到设定电压值;P2时,右边两组电容接在共模反馈中,保证运放共模反馈正常工作,左侧一组电容充电到设定电压值.运放在所有相位都可以正常工作,为预防共享技术提供基础.

图4 开关电容共模反馈电路Fig.4 Switched capacitor CMFB

2 仿真结果

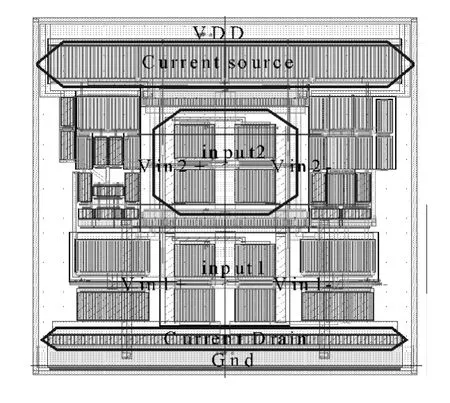

图5 运放的版图Fig.5 The layoutof theop amp

图6为此放大器的仿真结果,从结果中看出,其开环直流增益为93 dB,单位增益带宽积为1.8 GHz,相位裕度为64.72°.

图6 运放的仿真结果Fig.6 The simulation resultsof theop amp

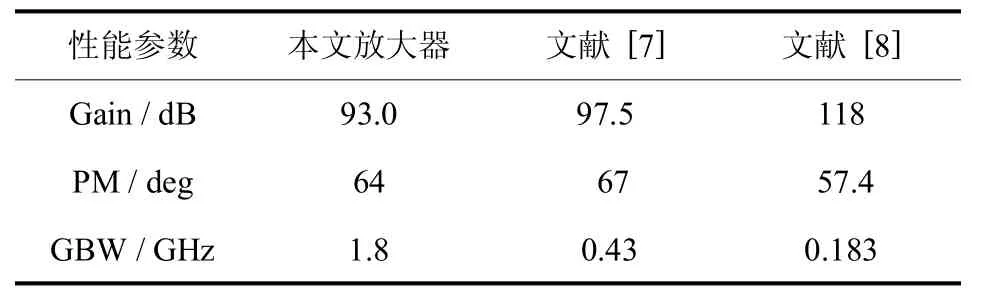

表1是此放大器与参考文献 [7]和文献 [8]的性能对比数据.通过对比可以看出,此放大器的开环直流增益和相位裕度与文献 [7]和文献 [8]中的放大器性能相近,但是单位增益带宽积要明显优秀很多.

表1 性能对比图Tab.1 Performance comparison chart

3 结论

本文提出了1种双输入对的增益增强型折叠共源共栅放大器,此放大器应用于高速高精度Pipelined ADC中,主运放采用双输入对交替工作,辅助运放采用单管共模反馈,节约了功耗、简化了电路结构.主运放采用开关电容共模反馈,因为开关电容共模反馈不会限制差分输入信号摆幅,并且不会在共模环路中引入额外的极零点对.运放的直流增益为93 dB,单位增益带宽为1.8GHz,相位裕度为64.72°,芯片的版图面积为.

[1]BultK,Geelen G JGM.A fast-settling CMOSOp Amp forSC circuitsw ith90-dBDCgain[J].IEEESolid-StateCircuits,1990,25(6):1379-1383.

[2]Kamath Y,Meyer R,Gray P.Relationship between frequency response and settling time of operationalamplifier[J].IEEESolid-State Circuits,1974,9(6):347-352.

[3]DasM.Improved design criteriaofgain-boosted CMOSOTA w ith high-speed optim izations[J].IEEETransCircuitsSyst I,Fundam Theory Appl,2002,49(3):204-207.

[4]A loisiW,Giustolisi G,Palumbo G.Analysis and optim ization of gain-boosted telescopic amplifiers[C]//Proc IEEE Int Symp CircuitsSyst.(ISCAS'02),USA:2002:321-324.

[5]RazaviB.Design of Analog CMOS Integrated Circuits[C]//Boston,MA:M cGraw-Hill,2000.

[6]JohnsD,Martin K.Analog Integrated CircuitDesign[M].NY:Wiley,1997.

[7]AhmadiM M,NajafiV,KhosravianiK.A new and efficientdesign procedure for gain-boosted cascode amplifiers[C]//Proce Eur Conf Circuit Theory and Design,(ECCTD'03),2003,3:401-404.

[8]Narendra Nath,TodaniR,Handrima C.Simplified designmethod for fully differentialgain-boosted folded cascade OTA[C]//IEEEConference on Information and Communication Technologies.2013,10:943-948.

[责任编辑 代俊秋]

Design on again-boosted cascodeamplifierw ith high gain and highunity-bandw idth

WANG Ting1,2,TANG Hailin1,ZHAO Zongyou1,YU Yuebao1

(1.Departmentof Electrical and Instrumentation,People's Liberation Army Air Force 93756,Tianjin 300131,China;2.School of electronic and Information Engineering,HebeiUniversity of Technology,Tianjin 300401,China)

This paper presents a high unity gain bandw idth fully differential folded-cascode operational amplifier using gain-boosted technique.Theamplifierisdesigned in TSMC 0.18 m 1P6M CMOStechnology.Theunity-gainbandw idth (GBW)and polesof thegain-boosting amplifierswere carefully designed to improve thestability.Theimplemented design providesa directcurrent(DC)gain ofaround 93 dBw ith aunity gain frequency of1.8GHz.Itexhibitsa DC gain larger than 88 dBwhen the outputcommon-mode voltagebetween 0.6 V and 1.2 V.The overall layoutsize is96 m×120 m.

cascode;gain-boosted;amplifiers;sw itched-capacitor;common feedback;pipeline ADC

TP368.2

A

1007-2373(2016)04-0020-04

10.14081/j.cnki.hgdxb.2016.04.004

2015-10-13

王停(1985-),男(汉族),博士生.