一种多核SoC的复位管理系统设计

2017-01-05张跃玲赵忠惠白涛汪健张瑾

张跃玲,赵忠惠,白涛,汪健,张瑾

(北方通用电子集团有限公司 微电子部,苏州 215163)

张跃玲,赵忠惠,白涛,汪健,张瑾

(北方通用电子集团有限公司 微电子部,苏州 215163)

设计了一种适用于多核SoC系统的低功耗上电复位电路,并根据冷复位、暖复位、看门狗复位、软件复位等复位源的类型设计了一种多核SoC系统的复位管理电路。复位管理电路提供了多核SoC系统处理器、片上总线及片上各个IP模块的复位信号,并都进行了相应的异步复位、同步释放处理。结果表明,设计的多核SoC系统的复位管理电路能够正确控制SoC芯片复位及复位释放后的多核SoC系统正常运行。

多核SoC系统;复位管理电路;上电复位;异步复位

引 言

随着大规模集成电路技术的发展,内嵌多个微处理器核的大规模SoC系统芯片渐渐成为集成电路设计的主要方向。而大规模多核SoC系统中的复位管理电路控制着SoC系统内部的逻辑功能和一定的时序关系,影响着片上多核SoC系统能否正常工作,是大规模多核SoC系统的关键部分。复位管理电路是多核SoC芯片重要基础组成部分,处理的合理与否直接影响整个电路的性能,也是大规模SoC系统电路能够正常工作的关键。复位管理电路负责为多核SoC系统和系统中的各模块IP提供相应的复位信号,控制着整个系统及片上IP的工作。而在复杂的SoC系统中,复位信号源的类型通常有1个或更多,送入复位管理电路模块的外部复位信号源多数为异步信号,如果处理不当,会引起亚稳态信号传播,导致系统不能正常运行。

本文介绍了一种内嵌多个DSP处理器核的SoC系统中的复位管理电路,该复位管理电路设计主要受冷复位、暖复位、调试复位、看门狗复位等复位源的影响控制,是一种复杂的多核SoC复位控制电路。此复位管理电路通过有效合理的设计方法能够处理各种复位源信号之间的关系及释放顺序,产生控制多DSP处理器核的SoC系统及内部逻辑、系统总线和内部其他IP模块的复位信号,并能够正确合理地复位及控制复位释放。

1 复位源设计及处理

复位管理电路是为SoC片上系统提供复位结构和层次、启动流程和复位结果的电路模块。设计的SoC系统的复位管理电路主要支持的复位类型为冷复位、暖复位、调试复位、看门狗复位、软件复位等复位源类型,各种复位源的复位功能如下:

冷复位——复位整个芯片所有逻辑;

暖复位——复位整个芯片逻辑,但不包括4个DSP的调试电路;

调试复位——仅复位4个DSP的调试电路;

看门狗复位——功能与暖复位相同;

软件复位——由软件写操作触发,处理器核及所有外设模块都支持单独的软件复位。

1.1 冷复位(上电复位)

冷复位即为上电复位引脚(POR),可以复位所有SoC内部逻辑及模块,影响所有复位域。在多核SoC系统中设计了一种片内上电复位电路,用于芯片上电时进行系统复位,能够在SoC系统开始供电的时候提供一个复位信号,以确保整个系统从一个确定的状态启动。

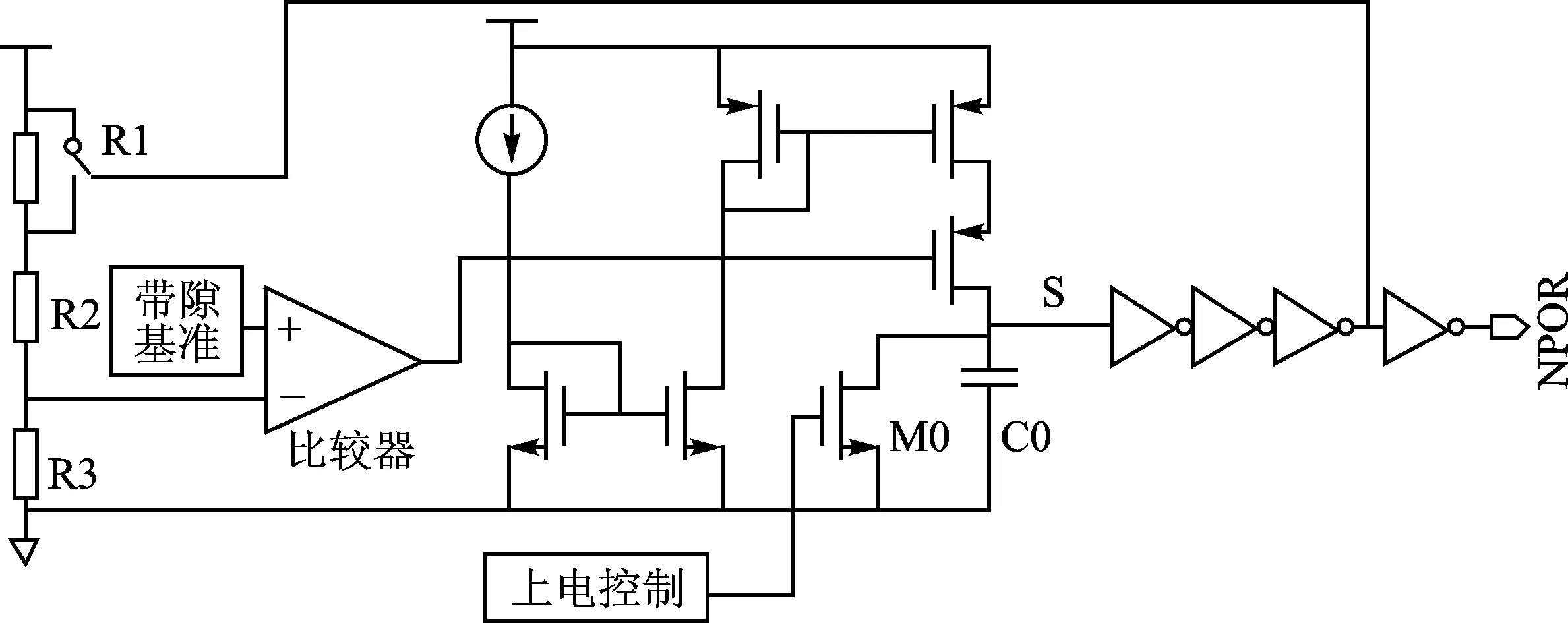

设计的上电复位电路如图1所示,包括带隙基准、比较器电路、上电控制电路。其中带隙基准源产生一个不随温度、电源电压和工艺变化的稳定电压,该电压与通过电阻(R1、R2和R3)分压产生的电平通过比较器比较,比较器输出电平控制电容C0充电,满足复位电平要求。在电源上电初期,比较器的工作点尚未建立,易发生误动作,上电控制电路的控制使电源在较低值下,电容电压恒为0,通过回差的设计可以防止电源上电期间的抖动,最后整形电路整形输出上电复位信号NPOR。

图1 上电复位电路

上电复位电路中,设计了一种nA量级极低功耗的电流偏置电路如图2所示,电路中不含有电阻,且带隙电压和偏置电流均与MOS管的阈值电压无关,带隙基准、比较器和上电控制电路均采用此技术。

偏置电路启动电路由M19、M20、M21、M22、M23、M24、M25、M26、M27组成。它帮助高稳定电流源发生电路脱离简并点而正常工作,高稳定电流源发生电路为其他电路模块提供偏置电流。电源开始上电,M25的栅压为低,M25导通,M27的栅压逐渐升高;当M27导通后,VA被拉低,VB变低,M1的栅源电压升高,MR导通,电流源电路和PTAT电压产生电路开始工作。当M1的栅源电压稳定后,M26导通,M27关断,VA、VB、VC、VD各点电压值由自身工作点决定。

nA量级高稳定电流源产生电路由电流源电路、与绝对温度成正比的PTAT电压产生电路和偏置电路组成。当MOS管工作在亚阈值区且其源漏电压大于0.1 V时,其电流表达式为:

(1)

(2)

M5、M6、M7、M8、M9、M10、M14、M15和MR组成电流源电路。设MR的电流为IR,栅源电压为VGSR,源漏电压VDSR,则有:

(3)

(4)

(5)

由于式(5)中不含VTH项,可以改善VTH对IR的影响。考虑载流子迁移率的温度特性,μ=μ0(T0/T)m,m为常数约1.5。由以上公式推导可知:

(6)

其中,IR0为与温度无关的常数。由上式看出,IR是仅与温度成正比,与工艺参数几乎无关的高稳定电流。

1.2 暖复位

暖复位即为暖复位引脚(RST),其低电平有效,外部暖复位信号来自外部按键信号,由于容易引发抖动和受外部毛刺信号影响,需要进行去毛刺和同步处理。在此多核SoC系统设计的复位管理电路中,使用数字电路设计中常使用的触发器级联完成滤波功能,实现防抖动、去毛刺的功能。

1.3 看门狗复位

在多核SoC系统内部设计了看门狗电路,用于检测微处理器核的运行情况,当出现程序跑飞或微处理器故障时,看门狗电路能够发出中断或复位信号。

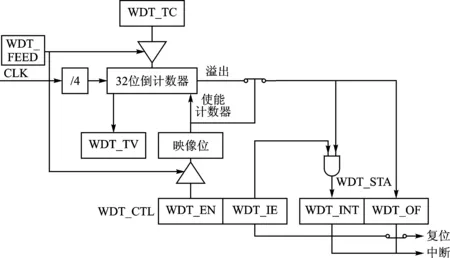

设计的看门狗复位源电路原理框图如图3所示。

图3 看门狗原理框图

图4 复位管理模块结构框图

看门狗电路的复位由复位管理模块控制,外部暖复位请求或上电复位均能引起复位管理模块复位看门狗电路。看门狗电路工作时,通过检测喂狗信号控制内部计数器;当开启看门狗模块功能时,如果出现喂狗异常或处理程序异常时,看门狗模块会发出中断或复位请求信号。看门狗电路内部计数器出现第一次溢出,在使能中断功能情况下,发出中断信号;在计数器出现第二次计数溢出时,发出复位信号。看门狗复位模块复位请求信号是一个高电平有效的复位信号并送至复位管理模块,看门狗复位信号送至复位管理模块内部需要先用复位管理模块的时钟作同步处理,防止亚稳态问题。

由于设计的多核SoC系统内嵌4个DSP处理器,片上设计4个结构和功能相同的看门狗模块。4个看门狗电路产生的复位请求信号都送至多核SoC系统的复位管理模块,复位管理模块对4个看门狗复位请求信号作相同处理,功能与暖复位一致,任意看门狗复位请求都会引起复位管理模块除调试复位外的其他逻辑复位。

1.4 软件复位

由软件写操作触发引起IP模块、片上总线、处理器核的复位,软件复位即通过微处理器核配置SoC系统片上的复位控制器,对片上微处理器核、片上总线、IP模块进行复位和复位释放。在此多核SoC系统中的复位管理模块分配复位控制管理寄存器的地址,并在复位管理电路中进行逻辑控制设计,可通过配置复位寄存器的值来实现片上SoC系统的软件复位功能。在此系统设计中,对SoC系统内的微处理器核和IP模块分配复位控制寄存器进行了软件复位管理。

2 多核SoC系统复位管理

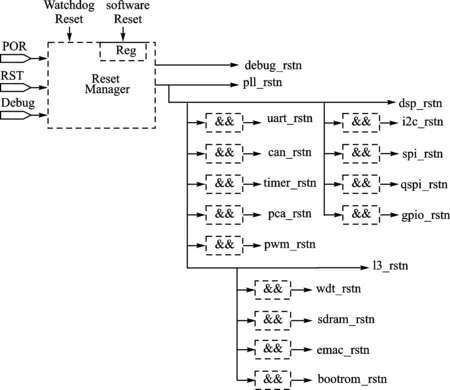

复位管理模块主要完成整个电路的复位时序管理,设计的复位管理电路应用于控制内嵌多个处理器核的SoC系统中。设计的多核SoC系统包含处理器核、片上总线,以及各IP模块;产生的复位信号需要有效地控制处理器核、片上总线,以及连接在片上总线的各个高速、低速IP甚至整个多核SoC系统。复位管理模块结构框图如图4所示,其中复位管理模块的复位源请求集中来自硬件、看门狗定时器、JTAG控制器和软件的复位,复位管理模块产生的复位信号能够驱动每个模块和系统的复位,是设备安全系统的一个集成部分。

SoC系统的复位管理电路设计方案简图如图5所示,主要是由外部复位请求、上电复位请求、看门狗复位以及通过配置寄存器产生的软件复位控制而产生;复位管理模块产生了全局复位信号(如图中的rstn)和每个微处理器核及模块IP需要的复位信号。全局复位信号控制着每个微处理器核、片上总线及其他各个IP模块。当全局复位信号释放后,需要经过每个模块部分的相应时钟同步后释放,才能送至相应模块,这样可防止亚稳态的产生和传播(如图中rstn信号,这里只做了简要图示,实际电路中需要用每个模块的时钟同步)。另外全局复位信号和配置寄存器产生的软件复位控制着微处理器核和IP模块的复位,图5中dspn_rstn为设计的SoC内部复位管理模块控制微处理器核的复位信号。

图5 SoC的复位管理电路设计框图

外部复位、上电复位、看门狗复位都需要经过用复位电路使用的时钟进行同步和除毛刺处理,三者经过与门后控制复位管理电路内部的复位定时器的复位端;外部复位、上电复位以及看门狗复位任一复位请求信号,均会使全局复位信号rstn拉低,并引起复位内部定时器复位清零。当外部复位、上电复位及看门狗复位都解除后,复位定时器的复位解除,复位管理模块的复位定时器开始计数,设计为内部复位计数器计数到定值(一般是大于处理器核的复位唤醒需要的时间),计数器停止计数并保持定值,释放全局复位信号使rstn拉高。

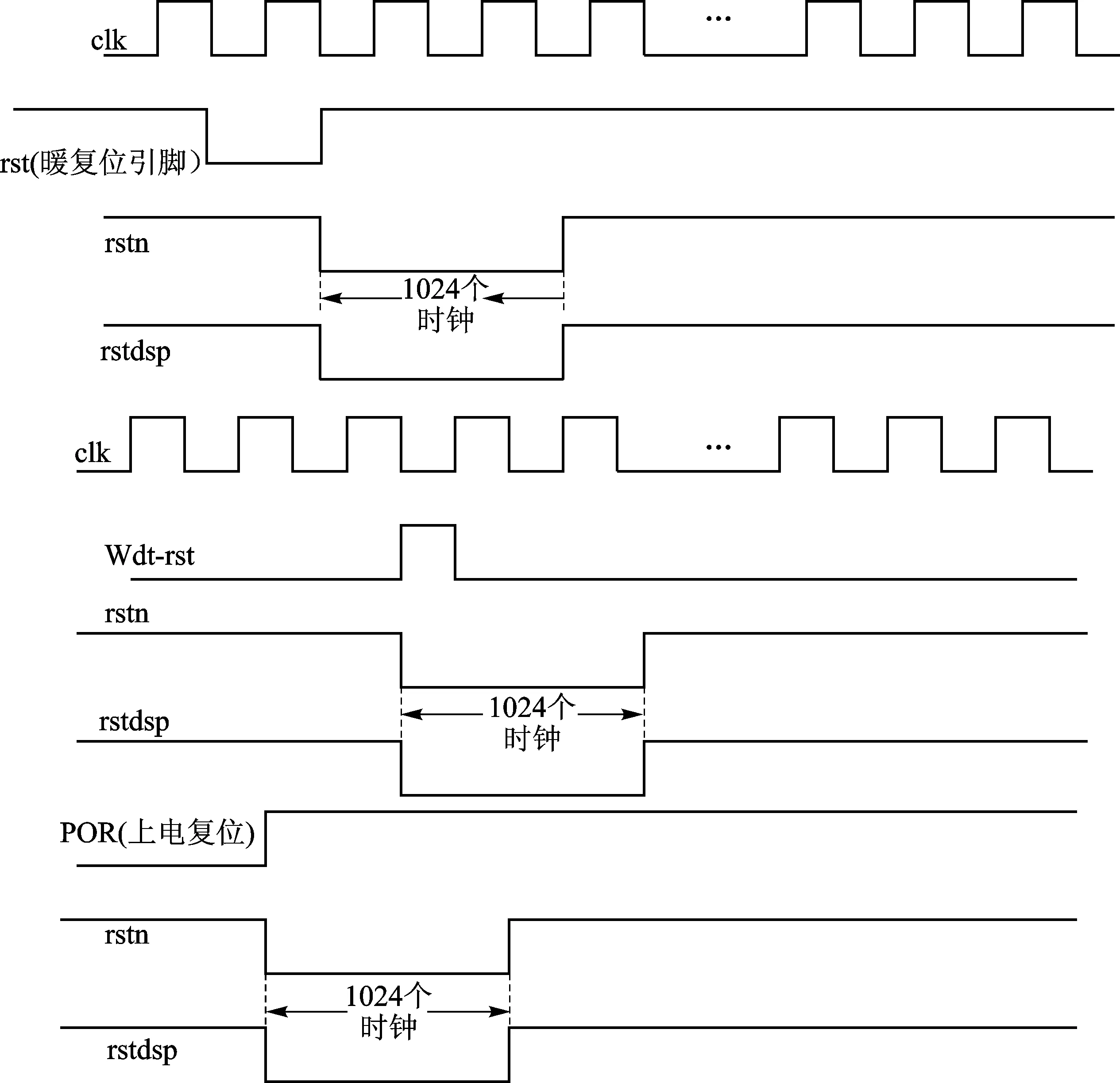

处理器核可通过配置相应的复位控制寄存器,关闭和开启相应模块复位信号,当配置复位控制寄存器为1时,每个模块复位释放,处于正常工作状态;当配置复位控制寄存器为0时,使相应微处理器及IP模块复位,关闭复位寄存器控制的微处理器核及IP模块。另外整个SoC系统及各个IP模块都采用异步复位、同步释放的复位管理模式,这样减少了采用同步复位的资源消耗,也减少了大的系统中异步复位产生的亚稳态状态的发生,使大的数字系统电路稳定工作。上电复位、看门狗复位、外部复位和产生的全局复位及处理器核的复位信号时序关系如图6所示。

图6 复位源与产生的复位时序示意图

3 测试结果

设计的多核SoC系统采用标准的SMIC 0.13 μm工艺已完成流片,并在测试基板上进行了流片后芯片的测试。为了更好地测试复位信号,芯片设计中已引出某个微处理器核(DSP0)的复位信号(复位寄存器默认值状态下和全局复位信号一致),引到I/O端口为测试信号。

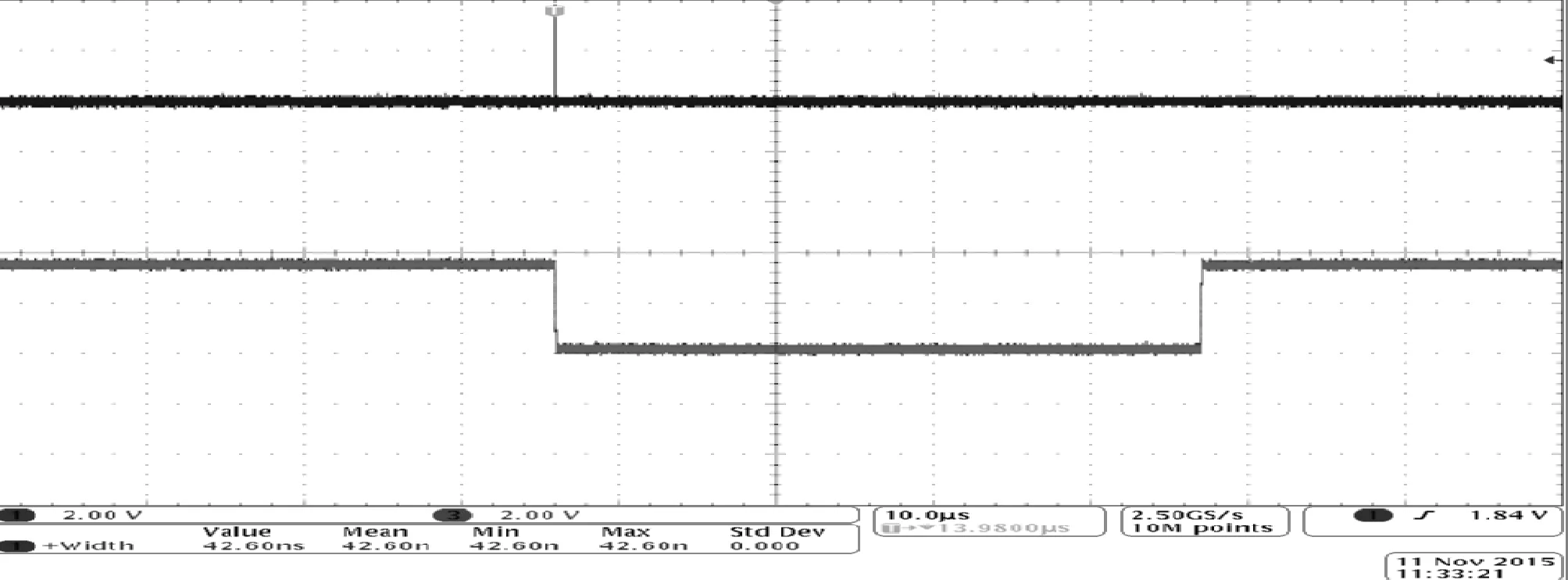

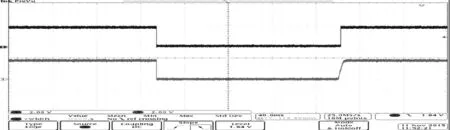

测试验证看门狗复位的正确性,测试结果显示,当及时喂狗时,全局复位测试信号保持高电平状态,当未及时喂狗时,测试全局复位信号出现一段时间低电平输出信号,如图7所示。深色代表引到多核SoC芯片 I/O端口的看门狗复位请求信号,浅色代表全局复位信号。可见看门狗复位出现高电平引起全局复位为低,并保持一定时间后重新释放。

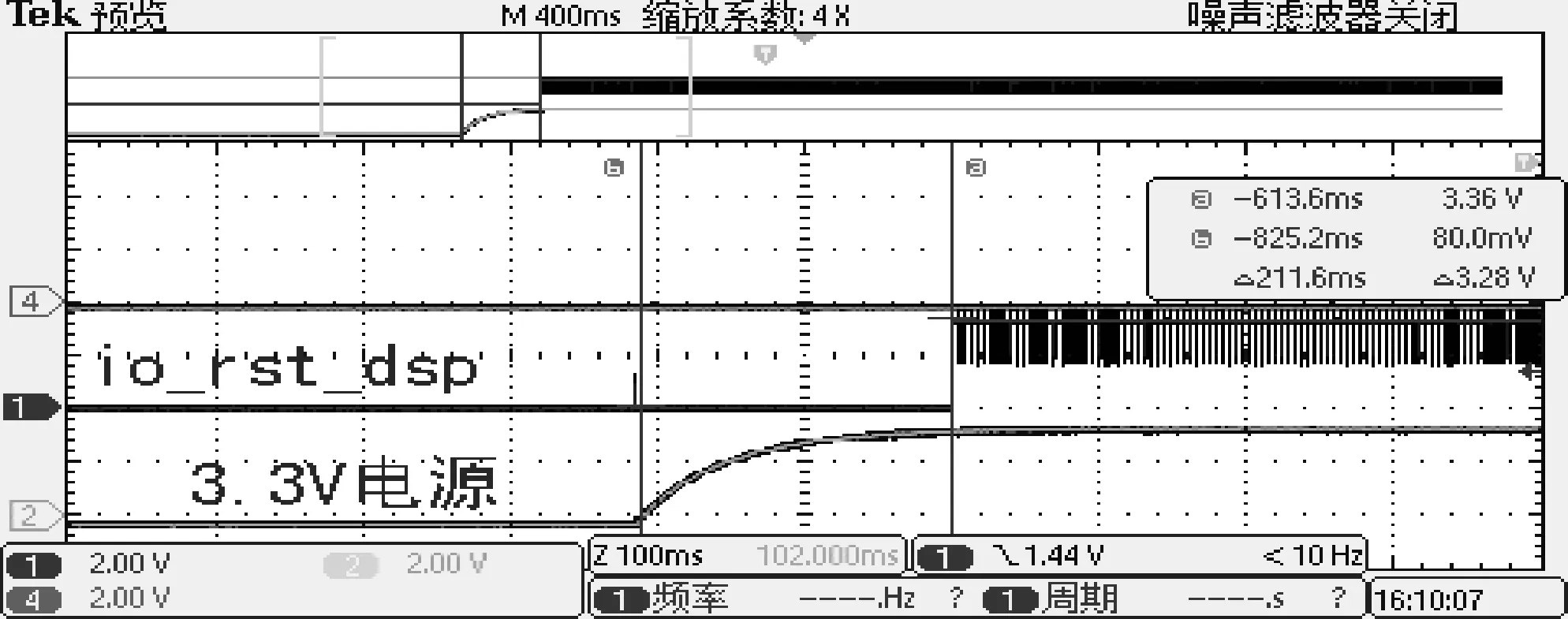

外部暖复位引脚输入端输入一个复位信号,使用示波器观察复位输出信号端是否也相应地产生复位输出信号。从图8中可以看出,外部暖复位信号为低,引起复位电路为低(深色通道为SoC内部引至端口的处理器核复位信号,浅色通道为外部复位信号)。

图7 看门狗复位引起的全局复位

图8 外部复位功能测试波形

在电源上电过程中,上电复位使处理器核或者系统的全局复位信号有起始低电平状态,在上电过程中,WDT复位和外部暖复位为无效复位状态,只有上电复位受影响,并设计需要初始的复位低电平信号。电路的上电复位与电源电压的关系如图9所示,测试表明上电复位信号(2通道)与外部电源(1通道)关系符合设计要求,功能正确。

图9 上电复位测试波形

在4个DSP的SoC系统调试界面,配置控制DSP和IP的寄存器,观测DSP和IP的测试信号,以对测试引脚的DSP的复位信号进行测试。在DSP界面配置*(int*)0x4000 2000=0x0000 0000;配置DSP0的复位控制寄存器为0,DSP0复位,测试引脚信号图略——编者注,可以看出配置DSP0的寄存器为0,引起DSP0的复位引脚信号拉低为低电平。

结 语

本文基于一个内嵌多个DSP微处理器控制的SoC芯片的设计与实现项目为基础,介绍了一种大规模多核SoC系统的复位电路设计。设计了多核SoC芯片上电复位电路, 并结合其他复位逻辑控制完成整个复位管理电路的设计。设计的多核SoC芯片成功流片后,在设计的PCB基板上测试了SoC芯片的复位相关信号,验证了上电复位、看门狗复位、外部复位、软件复位对复位管理电路的影响。结果表明,设计的复位管理电路能够提供SoC芯片内部需要的所有复位信号,正确控制SoC运行,能够控制多核SoC正确复位和复位释放后的SoC正常工作。

[1] 孙国志,宁宁,张弛.一种片上系统复位电路的设计[J].电子技术应用,2012,38(12):32-35.

[2] 司焕丽,胡杨川.一种适用于SoC的时钟复位管理电路设计[J].通信技术,2013,46(12):104-106.

[3] 张红莉,高明伦,徐诺.一种基于比较器的新型片内上电复位电路的实现[J].中国集成电路,2004(8):31-35.

[4] 刘迪军.超大规模集成电路设计中的复位电路设计[C]//中国通信集成电路技术与应用研讨会,2007.

[5] 姜超.SoC系统的时钟和复位电路[D].上海:复旦大学,2005.

[6] 周垚.SoC芯片中低功耗线性稳压器和上电复位电路设计[D].南京:东南大学,2011.

张跃玲(设计师),主要从事数字集成电路及大规模SoC设计。

Zhang Yueling,Zhao Zhonghui,Bai Tao,Wang Jian,Zhang Jin

(R&D Center in Suzhou,214 Institute of China North Industries,Suzhou 215163,China)

A low-power power-on reset circuit for the multi-core SoC is designed,and a reset management circuit is designed also according to the types of cold reset,warm reset,watchdog reset,software reset and so on.The reset management circuit provides a multi-core SoC system processor,on-chip bus and the reset signal of each IP module,and all of the corresponding asynchronous reset,synchronous release processing.The experiment results show that the designed reset circuit can supply the reset signal in the multi-core SoC and make the SoC work normally.

multi-core SoC system;reset management circuit;power-on reset;asynchronous reset

TN432

A

�士然

2016-06-20)