多核DSP的雷达数据处理平台设计

2017-01-03张利平

张利平

(中国西南电子技术研究所,成都 610036)

多核DSP的雷达数据处理平台设计

张利平

(中国西南电子技术研究所,成都 610036)

雷达数据处理平台是雷达的重要组成部分,在现代雷达中通常用来分析和融合雷达信号处理回传的目标信息,通过一系列复杂计算,将处理后的目标信息送给雷达综显进行显示。给出了以TMS320C6678为核心构建硬件平台的设计方案。通过实际测试,验证了平台的性能和工作的正确性。

雷达;数据处理平台;嵌入式多核;TMS320C6678

0 引 言

现代雷达已经被赋予了新的作战使命,不再单纯地作为目标探测的工具。在雷达的衍生应用中,需要处理雷达二次信息,如速度、航迹、机型、敌我属性、空情态势及各种人机交互信息[1]。在某些特定的雷达应用中,可能还需要显示数字地图或雷达SAR图像。要实现这些功能,就需要数据处理平台对大量的回波信息进行复杂算法分析,并送出处理结果。TI公司推出的高性能多核DSP芯片TMS320C6678,可以构建现代雷达的数据处理平台,其优异的性能满足现代雷达的大型数据处理算法搭建要求。该平台多核并行处理的优势也可以扩展到如雷达组网、信号处理、大型数据链等多种应用,具有广阔的市场前景。

1 TMS320C6678芯片介绍

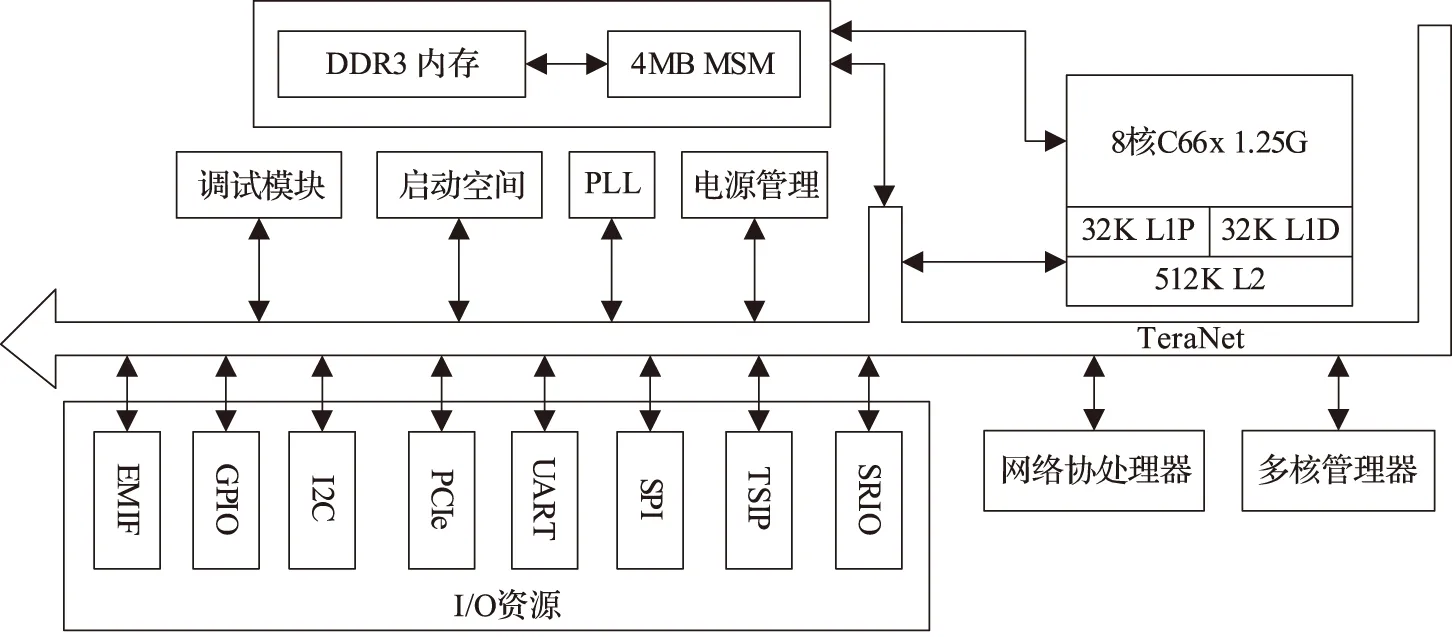

TMS320C6678是TI公司推出的高性能8核DSP芯片,采用了KeyStone架构,支持定点和浮点运算。其优势是片内整合了丰富的协处理器、高性能I/O和大量的运算资源,内部结构框图如图1所示[2]。

由图1可知,TMS320C6678是一个高度集成的多核DSP芯片,并且还具有以下特点[3-4]:

(1) 芯片集成8核DSP处理器,单核最高频率达1.25 GHz;

(2) 采用KeyStone高性能架构体系,将协处理器和I/O均融合到DSP核中,增强了芯片的扩展性和适应性;

(3) 增强型C66x内核,融合定点和浮点处理能力;

图1 TMS320C6678的内部结构

(4) 具备Semaphore硬件仲裁模块和资源共享机制,有利于多核协调访问共享资源,降低数据读写冲突的可能性;

(5) 丰富的外部接口功能,通过扩展后可以适应不同的接口需求。

2 平台的硬件设计

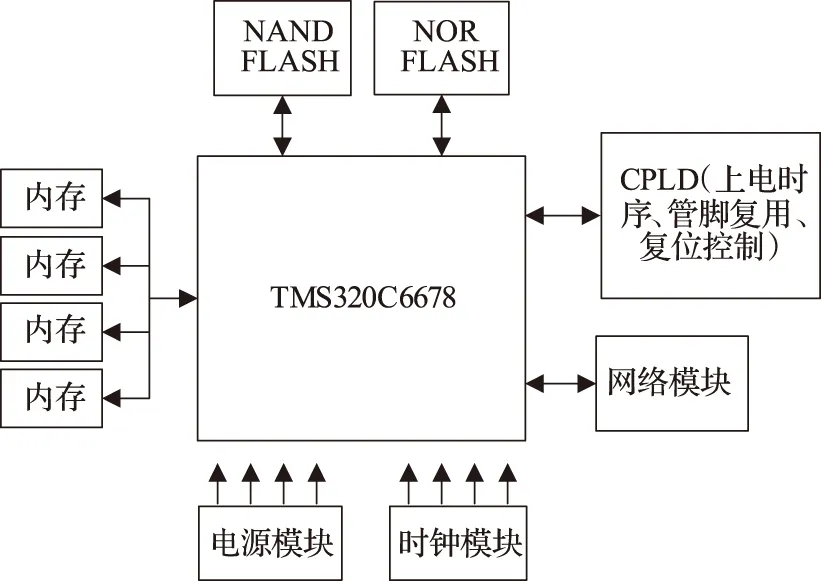

系统硬件总体框图如图2所示。

图2 数据处理平台系统搭建框图

考虑到后续模块的通用性和扩展性,将数据处理平台设计为标准XMC结构,即通过最小系统的构建方式引出所有外部的接口,方便后续大系统的自由搭建。数据处理平台的硬件设计部分主要包括电源模块、内存模块、网络和存储模块、时序配置模块等。

2.1 电源模块

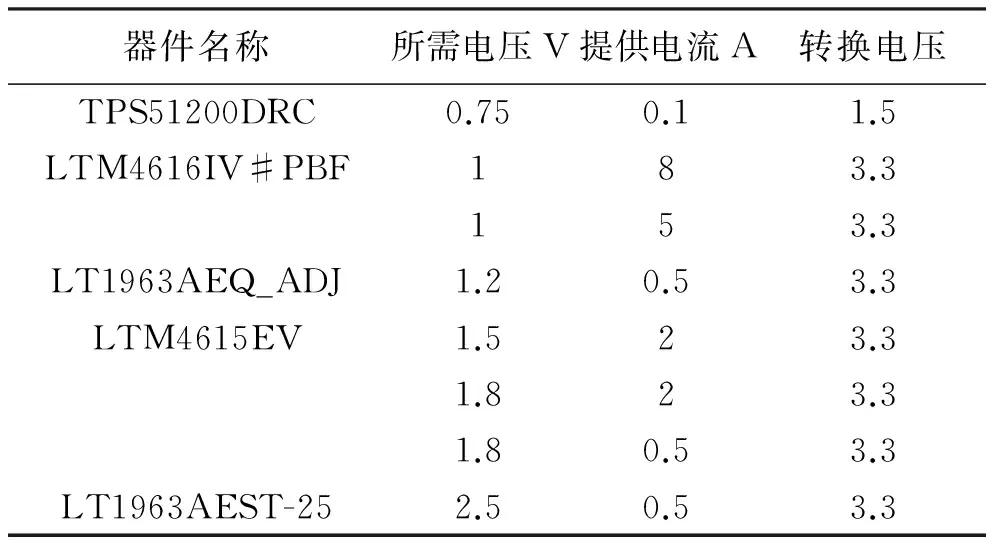

电源处理是决定硬件平台是否稳定的重要因素之一。XMC标准架构可以给模块提供+3.3V和+5V的电压,因此数据处理平台所需的其余电源均由电源转换芯片提供。为实现相关硬件功能,数据处理平台还需要+2.5V、+1.8V、+1.5V、+1V和+0.75V等5种电源。各电源分配如表1所示[6]。

表1 数据处理平台电源分配表

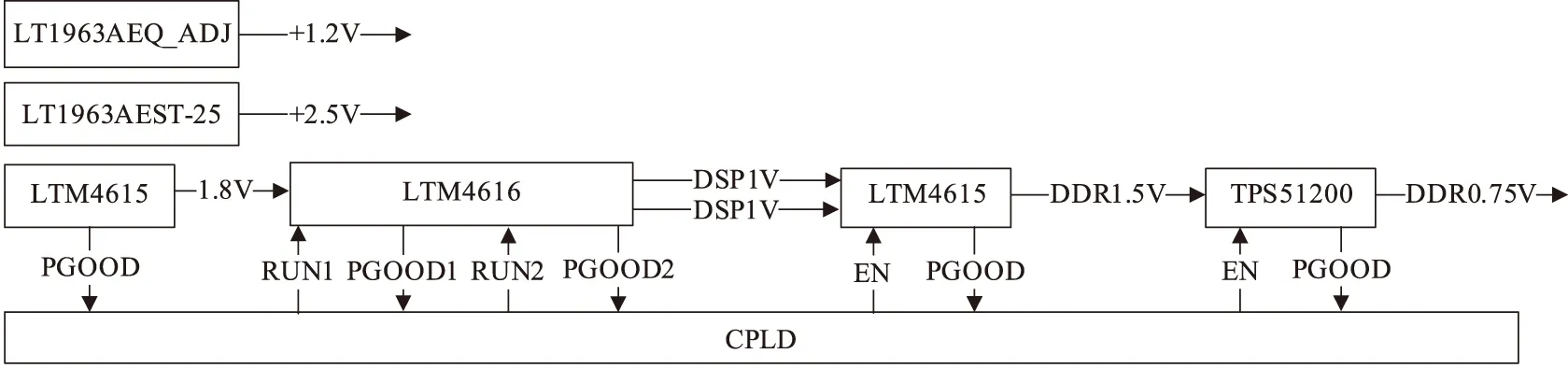

TMS320C6678启动时对各电源的上电时序有严格要求。因此,将各电源的输出稳定信号和输入使能信号接入CPLD进行控制,保证上电后DSP能正常工作。上电时序如图3所示。

2.2 内存模块

DDR3即第3代双倍数据率同步动态随机存取存储器,是电子设备工程联合委员会开发的新一代内存技术标准,其I/O总线时钟频率范围为800~2400 MHz。

图3 上电时序示意图

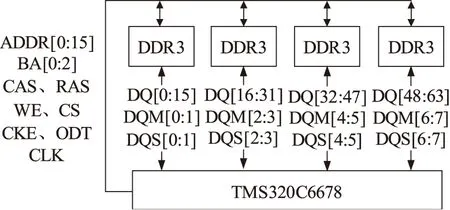

相较于DDR2标准,DDR3在功耗、工作频率和稳定性等方面都有较大的提高。在本次设计中,采用四片美光公司的512M内存,通过级联的方式,提供总共2G的系统存储容量。内存模块连接拓扑图如图4所示[5]。

图4 内存模块连接拓扑图

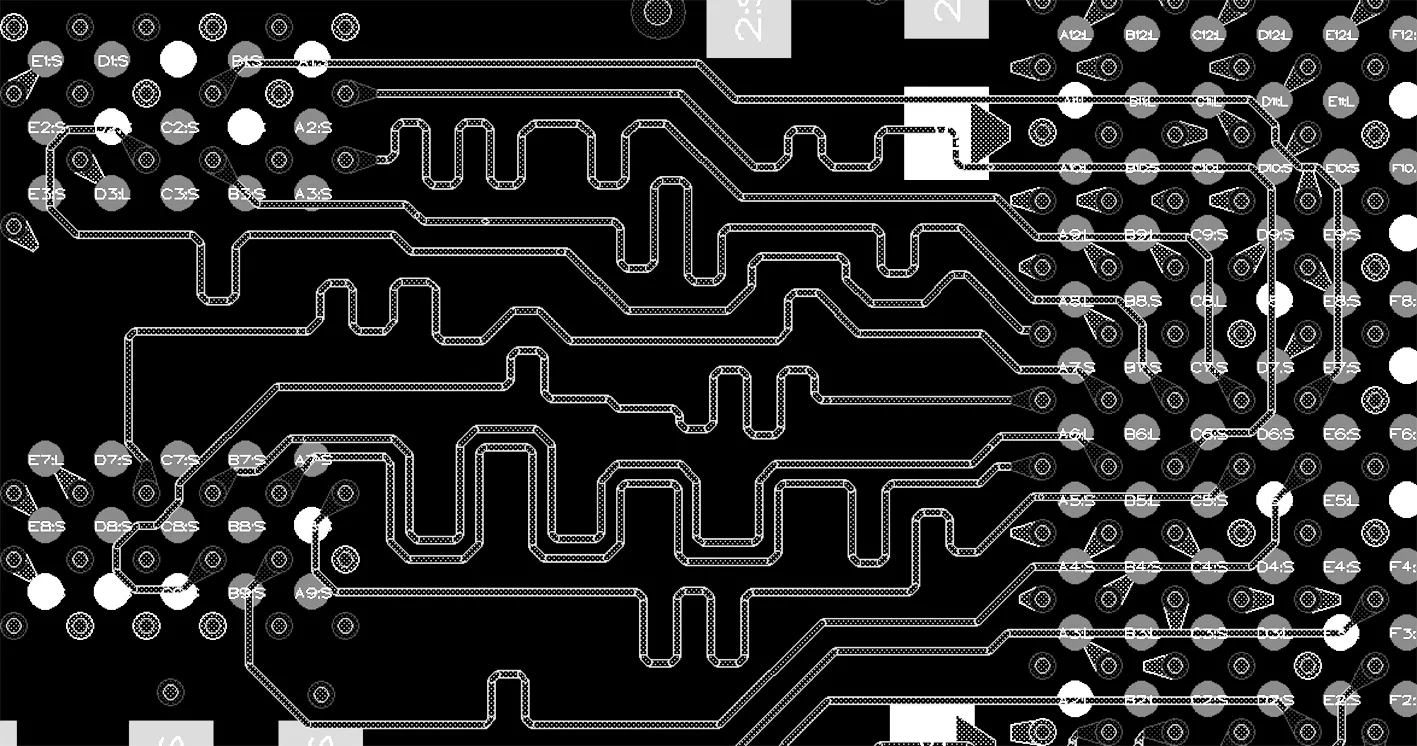

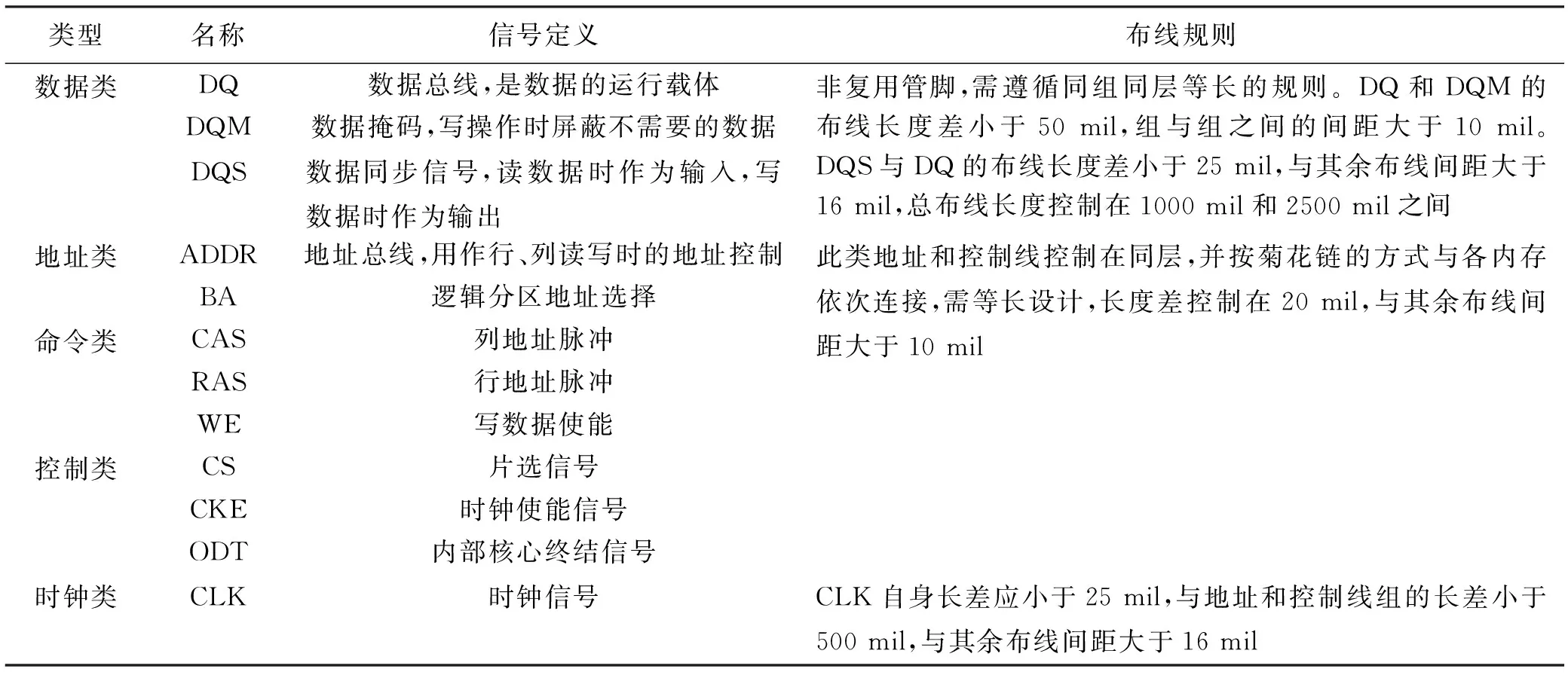

DDR3总线数据传输速率很高,传输电平低,易受到外界信号干扰,因此在设计时需严格遵循其布局、布线规则,保证信号传输质量。本次设计的布线规则如表2所示。数据组布线示意图如图5所示。

图5 数据组布线示意图

表2 DDR3总线布线规则

在DDR3应用中,需要将控制线上拉电阻到VTT,防止信号线终端产生反射。在本次设计中,考虑到印制板设计时可能产生的容差,将控制、命令和地址类信号进行RT端接(即上拉到VTT),确保信号完整性。

2.3 网络和存储模块

TMS320C6678 DSP芯片自带网络协处理器,支持2个物理网口扩展,增强了使用的灵活性。结合MARVELL的外围物理层控制芯片88E1111,可以搭建完整的网络通信架构。

88E1111自带SGMII接口,与DSP互联时无需增加额外的驱动芯片。在本设计中,将88E1111的配置引脚接入CPLD进行控制,既节约了配置电阻的布板面积又方便了配置。88E1111需要提供一个20 MHz的时钟输入,因此在外部接入一个晶体。需要注意的是,与DSP互联的数据收发差分对,需要在接收端端接一个100 nF的电容,隔离直流分量进行AC耦合。

考虑到数据处理平台在不同雷达平台中的功能扩展,在存储模块中同时使用了

NOR FLASH和NAND FLASH。NOR FLASH的容量较小,可以用来存储系统启动程序和部分小容量参数信息。NAND FLASH容量较大,可以存储大量的系统参数信息并实时记录试验数据[7]。

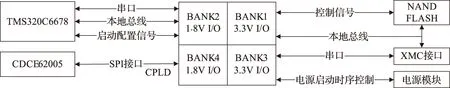

2.4 时序配置模块

在数据处理平台中,采用XILINX公司COOLRUNNER系列的CPLD:XC2C256-7FT256I,来做系统启动的配置和各I/O接口的转换,实现各种时序配置功能。该款CPLD包含4个BANK,每个BANK均可以独立配置I/O电压。由于TMS320C6678的I/O端口电压为1.8 V,其余芯片I/O端口电压为3.3 V,将BANK1和BANK3设定为3.3 V输出,BANK2和BANK4为1.8 V输出,这样就省掉了由于电压不一致而必须添加的驱动芯片,节约了布板面积,提高了系统的稳定性。CPLD模块的连接框图如6所示。

图6 CPLD模块连接框图

3 软件设计

TMS320C6678的8个内核相互独立。因此,当在进行软件开发时,为了最大限度地发挥其多核的效能,需要运用到核间同步的机制。核间同步的方式主要有以下4种[8]:

(1) 变量监听模式:在软件中通过监测volatile类型的变量变化情况,实现多核同步;

(2) 中断模式:多核之间通过中断的方式,实现同步;

(3) 事件通知模式:基于SYS/BIOS的多核同步通信模式;

(4) 消息传递模式:通过消息队列的方式,在传递同步信息的同时,可以传递少量参数信息。

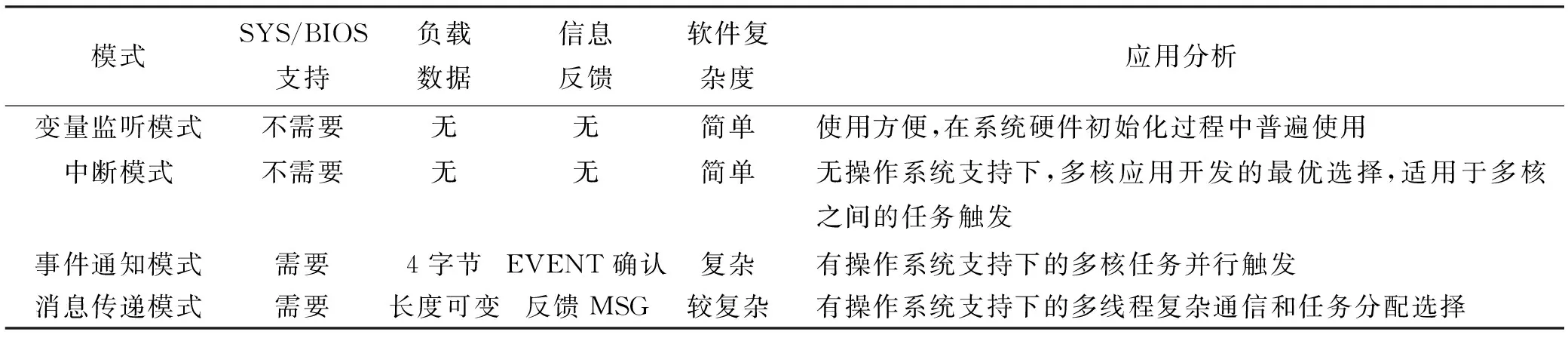

4种同步方式各有优劣,表3从几个方面进行了比较。

表3 核间同步模式分析表模式SYS/BIOS

3.2 多核DSP软件开发框架搭建

许诺向丁小慧坦白,自己是在结婚之后,才明白婚姻的真正价值,不是花好月圆时的锦上添花,而是他走在人生的阴暗面时,有她的扶持,当他寂寞的时候,有她愿意陪着他无所事事。是她对他的好,让他想变得更好,也让他爱上了她。

在多核DSP软件开发过程中,最重要的是均衡各核之间的任务量,即通过合理的软件框架划分,最大限度地发挥8核的并行处理效能,以便用最短时间完成数据处理工作。雷达的设计思路不一样,相同的数据处理算法需遵循的开发架构也不一致,并没有固定的映射关系。以下主要通过分析两种常用的软件框架介绍搭建软件框架的思路。

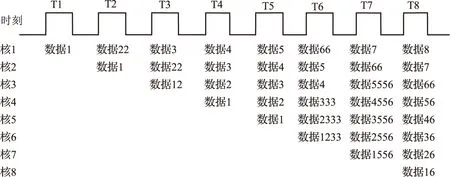

3.2.1 数据流框架

数据流框架即是流水线模式,是通过对算法处理流程的划分让每个核依次执行固定任务,最后一个核输出处理结果的形式。使用这种框架,内核之间对数据的处理是有先后顺序的,必须等前一个核处理完数据下一个核才能开始工作。使用数据流框架的关键在于算法处理时间的均匀划分。不合适的划分会导致某一个核数据处理时间过长,最终影响雷达系统的性能。当数据充满流水线顺序执行时,总体任务执行性能会得到较大提升。数据流框架处理流程如图7所示。

图7 数据流框架处理流程图

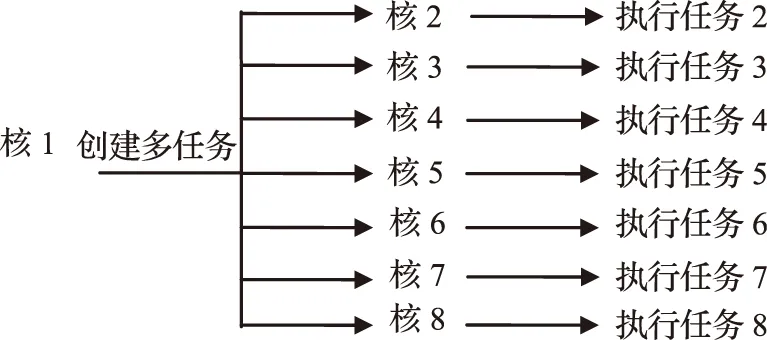

3.2.2 主从框架

主从框架即是使用其中一个核进行集中控制,创建多线程,将任务分流给其余核执行的过程。使用主从框架,必须有操作系统支持。这种方式对简单任务是适用的。当执行复杂任务时,难点在于如何均衡各从核之间的任务执行效率。只有能保证负载均衡和共享资源能够及时使用,才能实现整个软件的并行工作。

主从框架处理流程如图8所示。

图8 主从框架处理流程图

4 结果与分析

4.1 数据吞吐速率测试

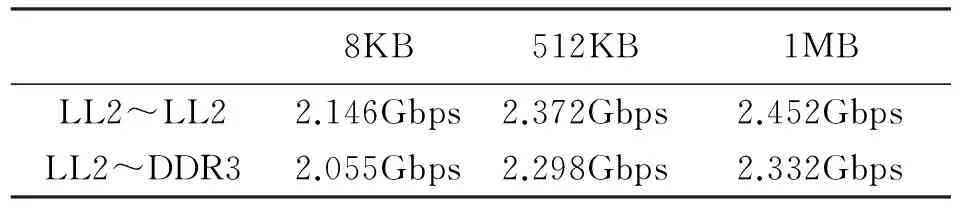

在雷达的SAR图像处理过程中,需要在DSP和存储器之间进行大数据的交互。数据吞吐的时间损耗即是一个关键指标。因此,着重对平台大数据搬移时间进行了测试,使用SRIO高速传输接口。测试结果如表4所示。

表4 数据传输速率测试表

在测试过程中发现,负载数据越小,传输的速率越慢。多核之间的LL2数据传输速率明显高于与外部DDR3的数据交互。因此,在实际软件设计过程中,频繁使用的数据应尽量在LL2之间进行交互,并尽量减少小块数据的传输,提高雷达系统数据实时处理能力。

4.2 功耗测试

在8核满负荷工作时,数据处理平台平均功耗约为15 W。通过外接散热片方式,传导散热,即可正常工作。

5 结束语

随着现代雷达技术的飞速发展,多核DSP的雷达数据处理平台也将成为发展趋势。本文介绍的即是其中一种应用于雷达设备中的多核DSP数据处理平台的设计方法。该平台以TI公司的多核DSP处理器TMS320C6678为核心,具有高性能、可扩展和低功耗等优点。此数据处理平台已经成功应用于某型号雷达设备中。本系统的研制成功也为开发下一代的雷达多核数据处理平台的研究提供了借鉴。

[1] 西北电讯工程学院《雷达系统》编写组.雷达系统[M].北京:国防工业出版社,1980:64.

[2] Texas Instruments.TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor[M].Texas,U.S.A,2012:11-63,92-208.

[3] Texas Instruments.C66x CPU and Instruction Set Reference Guide[M].Texas,U.S.A,2012:14-20.

[4] David Bell,Greg Wood.Multicore Programing Guide[M].Texas,U.S.A,2012:11-43.

[5] Micron Technology.1GB_DDR3_X4X8X16_D1[M].DDR3 SDRAM,2010:1-10.

[6] Texas Instruments.TMS320C6000 Optimizing Compiler v7.4 Users Guide[M].Texas,U.S.A,2012:11-27.

[7] Texas Instruments.KeyStone Architecture Gigabit Ethernet(GbE) Switch Subsystem User Guide[M].Texas,U.S.A,2013:20-34.

[8] 苏保禹.基于TI-C6678的多核DSP图像处理系统研究[D].中国科学院研究生院(光电技术研究所)硕士学位论文,2014:41-53.

Design of radar data processing platform with multicore DSP

ZHANG Li-ping

(China Southwest Research Institute of Electronics Technology, Chengdu 610036)

The radar data processing platform, as an important part of the radar, is generally used to analyze and fuse the target information sent back from the radar signal processor in modern radars. The target information processed is sent to the terminal display console for display after a series of complicated calculation. The design scheme of building the hardware platform is given with the TMS320C6678 as the core. The performance of the platform and the correctness of the work are verified through the actual test.

radar; data processing platform; embedded multicore; TMS320C6678

2016-09-10;

2016-10-03

张利平(1982-),男,工程师,研究方向:各种嵌入式平台的开发和显示系统的研究。

TN957.52

A

1009-0401(2016)04-0032-05