宽带雷达信号的低杂散采样系统研究*

2016-12-23潘明海

王 龙 潘明海 宋 聂

(1.雷达成像与微波光子技术教育部重点实验室(南京航空航天大学),南京,210016;2.南京航空航天大学民航飞行学院,南京,210016)

宽带雷达信号的低杂散采样系统研究*

王 龙1潘明海1宋 聂2

(1.雷达成像与微波光子技术教育部重点实验室(南京航空航天大学),南京,210016;2.南京航空航天大学民航飞行学院,南京,210016)

为了实现宽带雷达系统中雷达信号的低失真采集与处理,研究并设计了具有幅相误差校正功能的宽带低杂散采样系统。该系统采用宽带模数转换(Analog to digital converter, ADC)器件和高性能可编程逻辑阵列(Field programmable gate array, FPGA)的实现方案,并从低抖动采样时钟、低噪声电源和防串扰等方面进行了低杂散最优方案研究。为了改善系统的带内传输特性,利用优化算法设计了有限长冲激响应(Finite impulse response,FIR)数字校准滤波器。最后对设计的系统进行实验测试,结果表明系统瞬时带宽达到800 MHz以上,采样率1.8 GS/s,量化位数8位、杂散电平-50 dBc,性能指标满足系统在宽带雷达信号获取、宽带雷达目标成像和宽带雷达目标回波重构等领域的应用。

宽带采样系统;低杂散;幅相校正;FIR滤波器

引 言

由于超宽带雷达的高分辨率特性以及多功能、多目标探测、跟踪、识别和成像的能力,超宽带雷达越来越受到人们关注[1]。超宽带雷达研制中的关键技术之一便是实现宽带雷达信号的高速采样和实时存储。随着高速采样器件以及高性能可编程逻辑器件的快速发展,高速数字采样系统的研究进入新的阶段[2],在追求高宽带的同时,降低系统的杂散电平,提高系统的抗干扰能力[3]。从信号采样系统的信号带宽、采样精度和杂散电平等核心指标对现阶段系统的研究现状进行分析可以看出,由于高速率信号采样中的信号完整性问题以及硬件器件的限制,系统还无法实现各项指标较高的水平,如文献[4]中的采样系统带宽很宽,采样率达3.4 GS/s,但采样精度只有3位,杂散电平低于20 dBc;文献[5]研究的高精度信号采集系统量化位数14位,但采样率只有100 MS/s。目前可以看到的高速信号采样系统无法同时达到采样率和采样精度都很高的性能指标,大多是根据用途而偏向于其中一个指标的提高。在超宽带雷达系统应用中往往同时要求高带宽和高精度的系统性能,因此对超宽带雷达信号的高精度采样研究将是热门并且具有实际应用价值的工作。本文针对超宽带雷达应用中的这一需求,对宽带雷达信号的低杂散采样系统进行研究,以达到系统带宽、采样精度和杂散电平等指标的综合提高。

本文利用ADC采样器件和FPGA可编程逻辑器件设计了低杂散的宽带雷达信号高速采样系统,实现了对50~850 MHz宽带中频信号的高速采样和存储。为了在单个集成电路板上实现复杂、高度集成和高速高性能的信号采集和处理系统,本文采用高速采样电路低杂散设计,并通过数字域校准技术进一步改善系统的幅相传输特性。本系统的性能指标满足系统在宽带雷达信号获取、宽带雷达目标成像和宽带雷达目标回波重构等领域的应用。

1 宽带低杂散采样系统设计

为了实现高速、宽带和低杂散的高性能雷达信号采样系统,在系统设计中除了充分考虑器件性价比、电路系统尺寸和系统整体性价比外,重点研究了系统的低杂散采样设计。

1.1 宽带低杂散采样系统的方案

为了实现对宽带雷达信号的高速采集,本文在设计中采用高性能的ADC采样器件和FPGA信号处理器件,以双通道采样[6]和多路并行传输的技术方案来实现。系统的设计原理如图1所示。

图1 宽带雷达信号低杂散采样系统原理Fig.1 Schematic block diagram of low spurious sampling system for wideband radar signal

为了实现对800 MHz带宽信号以1.8 GS/s速度进行采样,本文采取双通道采样技术,在时钟上升沿对I通道信号采样,在时钟下降沿对Q通道信号进行采样,从而对时钟速度要求降为原来的一半,大大降低了硬件电路中时钟信号管理和传输的压力。当系统工作在单通道采样模式时,每个通道单独采集雷达信号,信号带宽降为400 MHz,但能同时处理具有正交性的两路信号,同时得到信号的幅度和相位,满足更多场合的应用。

在系统的ADC单元和FPGA单元间的数据传输中,数据速度达到1.8 GS/s,如此高的速度使得信号传输的准确性很难保证,信号线之间的串扰以及PCB布线失误在高速信号传输中的影响将会表现得十分突出,高速度成为系统设计中的一大难题。在本文设计中,采取4条数据总线并行传输的技术方案,以原来速度的1/4实现在ADC单元和FPGA单元之间1.8 GS/s信号的低失真快速传输。在FPGA中为了实现对4路450 MS/s信号的处理及存储,系统采用1:4串并转换的技术方案,使得信号速度再次降为1/4,从而解决了本设计选用FPGA器件300MHz数据处理速度的限制,但是付出了增加硬件资源的代价。

1.2 宽带采样系统的低杂散设计

评价宽带采样系统性能的重要指标之一就是系统的杂散特性。一般情况下随着系统处理带宽和采样速率的提高,系统的杂散性能会不断恶化,因此在宽带高采样率采样系统设计中的关键之一就是降低采样系统杂散。影响采样系统杂散的主要因素有采样时钟的抖动[7,8]、电源引入的噪声以及高速率信号传输时的串扰以及抖动失真等。本文在采样系统的硬件设计中,结合产生杂散的主要原因进行设计,使得系统的杂散性能进一步提高。

1.2.1 低抖动采样时钟设计

宽带高速采样系统对采样时钟非常敏感,但由于采样时钟产生电路存在热噪声、相位噪声等,所以采样时钟肯定存在抖动。根据文献[9,10]对不同分布、不同形式噪声产生时钟抖动对采样系统性能的分析,可以得到性噪比SNR与时钟抖动tjitter的关系式

(1)

(2)

故可以得到时钟抖动的表达式

(3)

根据时域抖动与频域相位噪声的对应关系,也可以得到采样时钟相位噪声的表达式

(4)

1.2.2 高效低噪声电源设计

随着宽带高速采样系统分辨率的提高,系统对噪声也更加敏感,系统分辨率每提高一位,系统对噪声敏感度就会提高一倍。因此,对于ADC采样系统设计,必须考虑一个常常被遗忘的噪声源——电源噪声,如果系统电源噪声严重,则此噪声会提高转换器噪底,从而限制整个系统杂散的降低。

开关稳压器由于很高的电压转换效率(通常90%以上)获得广泛应用,但带来的问题是噪声会通过电源纹波直接耦合到转换器,从而影响ADC转换性能。结合低压差线性稳压器(Low dropout regulator, LDO)低纹波和低噪声的良好性能以及低效率的缺点(通常为30%~50%),通常采用LDO和DC-DC相结合的设计方法。例如需要将5 V的输入电压降压到1.5 V的电压,可以先使用DC-DC将5 V电压降到1.8 V,再采用LDO将1.8 V降到1.5 V,通过LDO和DC-DC两级变压设计,可以有效提高变压效率,降低电源噪声。

在电源设计中,为了确定供电轨处于何种噪声水平才能使ADC实现预期性能,本文通过稳压器供电噪声和模数转换器噪底大小进行比较判断。模数转换器的噪底可通过量化位数、满量程电压、信噪比SNR以及采样速率求出。一般情况下,模数转换器厂商还会提供器件的电源抑制比(Power supply rejection ratio,PSRR)指标,它是电源电压的变化与由此产生的ADC增益或失调误差的变化之比值,表征了ADC抗电压噪声的能力。因此在电源设计中,本文通过计算得到的噪底大小加上PSRR来确定供电轨的上限噪声参数。在选择开关稳压器时,根据手册提供的噪声和纹波指标以及开关频率进行计算与仿真设计,在满足上限噪声参数的要求下选择合适的开关频率已达到最高的电源转换效率。电源电路还需考虑滤波、去耦以及磁珠隔离等设计,虽然不能完全消除电源噪声,但可以通过采取有效措施使得电源噪声对系统的影响降到最低。

1.2.3 信号传输防串扰设计

图2 低杂散设计中的串扰分析 Fig.2 Analysis of crosstalk in the design of low spurious

在硬件电路设计中,电路的物理长度L和信号波长λ的比值L/λ称为电长度,该值的大小对电路布局以及信号间串扰的分析有着重要影响。当电长度的值足够小时,电路就可以认为是集总参数电路,从而利用最基本的电路理论进行系统信号分析,通常将电长度的值1/20认为是从集总参数电路到分布参数电路的分界点[11]。为了在PCB板上实现高达GHz信号较小的电长度值,系统设计中在电路布局布线时器件、信号传输线互相距离很近,因此很容易造成串扰。 设两根传输线的宽度为w,中心间距为D,两根导体的公共返回路径为地参考平面,导体到上下两参考平面的距离分别为h2,h1,则信号传输线在地参考平面上的归一化电流密度分布如图2所示[12]。

由图2可以看出攻击线上的信号会在受害线上产生耦合电流,从而产生串扰信号,该串扰信号也可能反过来对攻击线产生串扰,这会扰乱信号线上的信号波形。当h1与h2相等时在参考面上产生的电流密度可表示为[13]

(5)

在高速数字系统设计中,通过选取合适的导线间距将能够显著减小攻击线到受害线上的耦合电流,从而减小串扰。如从图2所示的电流密度分布可以看出D越小则耦合电流越大,D越大则耦合电流越小,本文根据电流分布规律合理地设计电路布局,从而减小串扰。

1.2.4 低电压差分(LVDS)传输设计

通常的信号传输是单端传输,即每个信号有一个单独的导体,这种单端传输会产生严重的共模噪声,特别在信号速度很高的时候,噪声特别大,信号失真严重。而LVDS传输是在两条传输线上传输相位相反的信号,在接收端,一个差分放大器以两条线上的电压差来恢复信号,从而极大的抑制了共模噪声,并且由于差分传输电压幅度低,可以传输更高的信号速率,提供了良好的信号完整性[14]。

如果差分对上传输的信号波形记为v(t),则两个新的反相波形可以定义为

(6)

式中uo是一个恒定的电压。电压v1和v2分别加在一对对称耦合传输线的一端,如图3所示。此时偶模电压和奇模电压分别为

图3 对称耦合差分传输示意图Fig.3 Schematic diagram of symmetric coupled differential transmission

(7)

偶模电压上仅含有直流分量,它不会在寄生电抗上产生噪声,而奇模电压则是加权后的信号。

如果一对传输线是紧耦合,则一个外部噪声源就会以共模噪声的形式同等地加到两条传输线上。在远端模式电压上叠加一个共模噪声可得

(8)

式中v′是奇模的相速。则远端的终端电压为

(9)

在远端,用一个差分接收器仅检测两条传输线上的信号差,得到输出为

(10)

因此,差分传输可使信号以奇模相速传输而不受共模噪声的影响。在本文设计中,高速的时钟信号传输以及数据传输线均采用LVDS传输技术,从而很好地减低系统的信号杂散。

2 系统幅相特性的数字校准技术

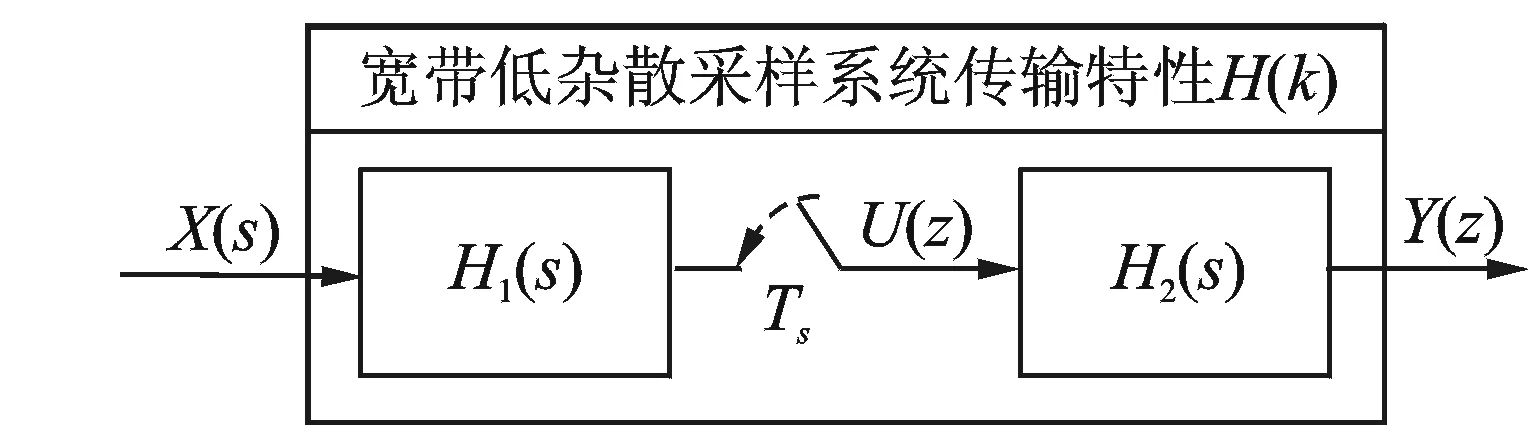

在宽带雷达信号高速采样系统中,系统通带内频谱的幅度不平坦度及相位误差来源于ADC器件对不同输入频率的幅相误差以及系统中各个模块、信号传输线对不同频率信号响应的幅相误差积累的结果,并且这些因素很难人为消除。为了提高系统对宽带输入信号的处理质量,本文将采样序列通过数字校准滤波器对带内频谱的幅相误差进行校准,从而保证良好和稳定的系统性能。宽带雷达信号高速采样系统的数字域幅相校准原理如图4所示[14]。

图4 采样系统的幅相校准原理 Fig.4 Schematic block diagram of the amplitude and phase correction of the sampling system

图4中X(s)为雷达输入信号x(t)的拉普拉斯变换,U(z)为系统校正之前的采样序列u(n)的Z变换,其系统传输函数为H1(s),Y(z)为系统经过校正处理后输出的采样序列y(n)的Z变换。设由U(z)到Y(z)的数字校准滤波器的传输函数(幅相误差补偿函数)为H2(z),则有[15]

(11)

(12)

(13)

(14)

由于输入信号x(t)和采样序列y(n)均为实数,根据数字信号处理知识可得X(k)和Y(ejkTs)在带内都是共轭对称函数,可证得H2(ejkTs)也是共轭对称函数,因此在本文中用实系数FIR滤波器逼近数字校准滤波器。

(15)

(16)

根据文献[18]给出的引入旋转变换因子方法

(17)

FIR滤波器设计可表述为线性优化问题

(18)

(19)

本文对于式(18)的最优解[19,20]求解过程不再赘述。

3 系统实验测试

本文在系统设计完成后对系统性能进行了测试。在数据采样系统中,数据采集性能一般用采样信号的杂散分量来衡量,通常以无杂散动态范围SFDR表示(dBc)。SFDR指的是是信号的均方根值与最差杂散信号(无论它位于频谱中何处)的均方根值之比,表征了可以与大干扰信号(阻塞信号)相区别的最小信号值。本文基于SFDR指标的测试结果如图(5~9)所示。系统输入单频信号,以满足奈奎斯特采样频率的时钟信号进行采样,得到的数字信号的频谱如图5所示,从图5可以看出,系统对于50MHz到850MHz的信号都具有良好采样和处理性能。

图5 单频输入信号的系统响应Fig.5 System response of single frequency input signal

图6 系统SFDR与输入信号频率曲线图图7 系统SFDR与采样频率关系曲线图Fig.6 SFDR vs.input frequency Fig.7 SFDR vs.sampling rate

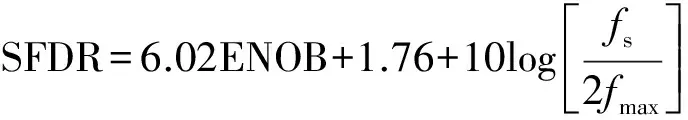

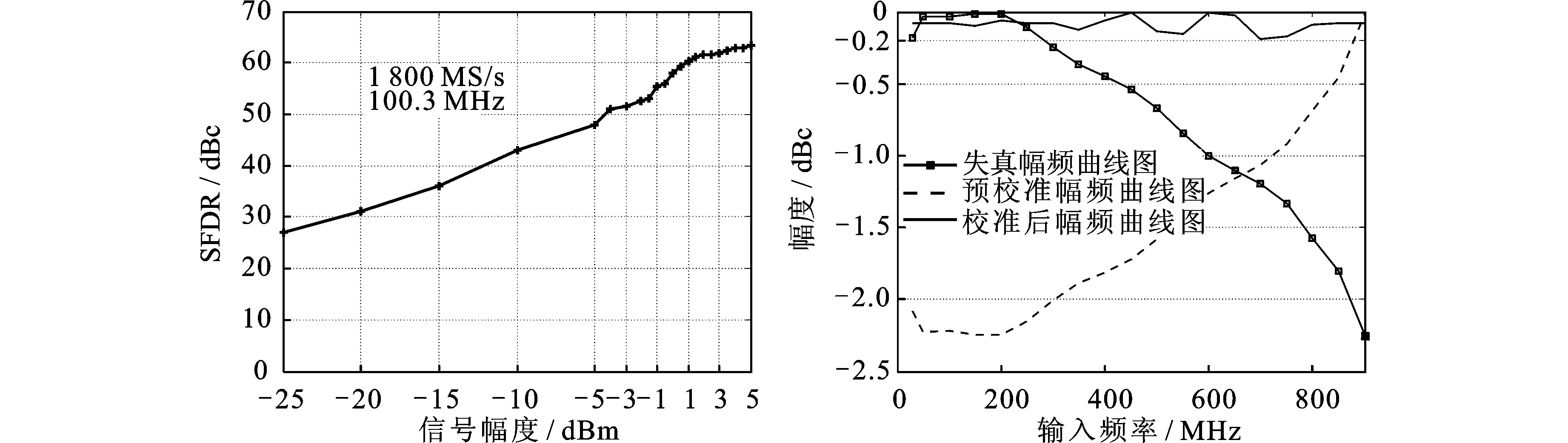

图8 系统SFDR与输入信号功率曲线图图9 FIR滤波器数字校准曲线图Fig.8 SFDR vs.input amplitudeFig.9 Curve of FIR digital filter correction

图7为杂散电平与采样频率的曲线图,对于一个固定频率、固定功率输入的信号,随着采样率的增加,系统输出的杂散电平也升高,但会带来数据量大的问题,并且但硬件电路的性能也限制了采样率的进一步提高。所以在实际应用中在杂散电平满足要求的情况下选择尽可能小的采样频率以减少数据量,也可以利用带通采样来达到这一目的。图8所示为信号输入功率与杂散电平的关系曲线图可以看出,输入信号功率在-5~5 dBm范围里面保持着良好的杂散电平性能,当输入信号功率不断降低时,系统输出的杂散电平也不断降低。由于系统的最高输入功率限制是5 dBm,所以本系统测试的最高输入功率为5 dBm,在实际应用中,一般通过功率放大器将输入雷达信号功率放大到系统的工作功率范围中。图9所示为系统幅频曲线、FIR校准滤波器的幅频曲线以及校准后系统的归一化幅频曲线图。从图中可以看出,系统对宽带信号的响应输出幅度随着频率增加而下降,使得系统对宽带雷达信号的采样处理会出现失真。为了改善宽带系统的传输特性(带内平坦度),采用FIR数字校准滤波器进行校准,校准后系统的带内归一化不平坦度小于0.2 dB,满足系统应用的要求。虽然采用FIR校正能够改善系统的传输特性,提高系统对宽带信号的处理质量,但也会占用硬件资源,造成数据运算量的增加,并且当系统的相关参数设置改变后,该FIR滤波器需要做对应的调整,实时性不高。

4 结束语

本文研究设计了基于ADC和FPGA的宽带雷达信号的高速低杂散采样系统。为了提高系统的采样保真度,降低杂散,重点从方案设计、低抖动采样时钟设计、高效低噪声电源设计、防串扰设计和LVDS设计等几个方面进行了研究。另外,为了改善系统的传输特性,设计了FIR数字校准滤波器,解决了系统对宽带信号输入的幅相误差校准技术。最后通过实验测试验证,系统在50~850 MHz的工作带宽内能够达到50 dBc的杂散电平指标要求,采样精度达到8位,能够很好地用于宽带雷达信号获取、宽带雷达目标成像以及宽带雷达目标回波重构。在本文的后续研究中,作者将对压缩感知技术[21]在雷达目标信号的高速采集中的实现进行研究。系统存储时通过数据压缩技术,能够有效增加系统存储的目标信息容量,同时也能够缓解对系统运算性能的要求,这将是下一步研究的重点。

[1] Rahayu Y,Rahman T A,Ngah R,et al.Ultra wideband technology and its applications[C]∥Wireless and Optical Communications Networks 2008 WOCN'08,5th IFIP International Conference on.Surabaya:IEEE,2008:1-5.

[2] Xia Wenyue,Yuan Haiwen.A development platform for complex data acquisition system[C]∥Electronic Measurement & Instruments (ICEMI),10th International Conference on.Chengdu: IEEE,2011:321-324.

[3] Olivier K,Cilliers J E.Design aspects and characterised performance of a wideband DRFM for radar test and evaluation[C]∥Radar Systems (Radar 2012),IET International Conference on.Glasgow,UK:IET,2012:1-4.

[4] Zhang Min,Zhang Youtao,Li Xiaopeng,et al.3.4 GS/s 3 bit phase digitizing ADC and DAC for DRFM[C]∥2009 IEEE 8th International Conference on ASIC.Changsha:IEEE,2009:226-229.

[5] Pullia A.Interfacing low-noise charge-sensitive preamplifiers to high-resolution flash ADCs[C]∥Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC).Valencia:IEEE,2011:880-884.

[6] Liu Haibo,Teng Long,Zeng Dazhi.Design of a two-channel ultra high frequence data acquisition system based on FPGA[C]∥Radar,CIE′06.International Conference on.Shanghai: IEEE,2006:1-3.

[7] 李和平,王岩飞.高速高精度ADC系统研究[J].数据采集与处理,2008,23(S):208-211.

Li Heping,Wang Yanfei.High speed and high resolution ADC system[J].Journal of Data Acquisition and Processing,2008,23(S):208-211.

[8] 张尚良,邹月娴.TIADC高速数据捕获和时间失配补偿的FPGA实现[J].数据采集与处理,2011,26(5):601-608.

Zhang Shangliang,Zou Yuexian.FPGA implementation of data acquisition and timing mismatch compensation for TIADC system [J].Journal of Data Acquisition and Processing,2011,26(5):601-608.

[9] Da Dalt N,Harteneck M,Sandner C,et al.On the jitter requirements of the sampling clock for analog-to-digital converters[J].Circuits and Systems I:Fundamental Theory and Applications,IEEE Transactions on,2002,49(9):1354-1360.

[10]Zanchi A,Samori C.Analysis and characterization of the effects of clock jitter in A/D converters for subsampling[J].Circuits and Systems I:Regular Papers,IEEE Transactions on,2008,55(2):522-534.

[11]Schmitt R.Electromagnetics explained:A handbook for wireless/RF,EMC,and high-speed electronics[M].USA:Newnes,2002:8-14.

[12]Olivier K,Cilliers J E,Du Plessis M.Design and performance of wideband DRFM for radar test and evaluation[J].Electronics Letters,2011,47(14):824-825.

[13]Holloway C L,Kuester E F.Closed-form expressions for the current densities on the ground planes of asymmetric stripline structures[J].Electromagnetic Compatibility,IEEE Transactions on,2007,49(1).49-57.

[14]Young B.Digital signal integrity:Modeling and simulation with interconnects and packages[M].USA:Prentice Hall PTR,2000:391-394.

[15]Chen Shuxuan,Jiang Limin,Xiang Maosheng.Channel error correction for wideband SAR—A joint multiple subpulses processing method[J].Journal of Electronics (China),2011,28(1):134-140.

[16]宋千,陆必应,梁甸农.采集系统通道传输特性校正[J].数据采集与处理,2002,17(1):85-89.

Song Qian,Lu Biying,Liang Diannong.Correction to transform function of data acquisition channel[J]. Journal of Data Acquisition and Processing,2002,17(1):85-89.

[17]Lee J H,Chen C K,Lim Y C.Design of discrete coefficient FIR digital filters with arbitrary amplitude and phase responses[J].Circuits and Systems II.Analog and Digital Signal Processing,IEEE Transactions on,1993,40(7):444-448.

[18]Burnside D,Parks T W.Optimal design of FIR filters with the complex Chebyshev error criteria[J].Signal Processing,IEEE Transactions on,1995,43(3):605-616.

[19]华容.一种混沌粒子群嵌入优化算法及其仿真[J].数据采集与处理,2010,25 (1):102-106.

Hua Rong.Chaos embedded particle swarm optimization algorithm and its simulation [J].Journal of Data Acquisition and Processing,2010,25 (1):102-106.

[20]张俊杰,仰继连.蚂蚁算法在FIR数字滤波器优化设计中的参数[J].数据采集与处理,2013,28 (3):336-341.

Zhang Junjie,Yang Jilian.Parmeters in FIR digital filters optimal design based on ant algorithm[J].Journal of Data Acquisition and Processing,2013,28 (3):336-341.

[21]张弓,杨萌,张劲东,等.压缩感知在雷达目标探测与识别中的研究进展[J].数据采集与处理,2012,27(1):1-12.

Zhang Gong,Yang Meng,Zhang Jindong,et al.Advances in theory and application of compressed sensing in radar target detection and recognition[J].Journal of Data Acquisition and Processing,2012,27(1):1-12.

王龙(1991-),男,硕士研究生,研究方向:射频仿真与信号处理,E-mail:wang2012 5@126.com。

潘明海(1962-),男,博士,教授,博士生导师,研究方向:射频仿真与信号处理。

宋聂(1989-),女,硕士研究生,研究方向:交通运输优化算法设计。

Low Spurious Sampling System of Wideband Radar Signal

Wang Long1, Pan Minghai1, Song Nie2

(1. Key Laboratory of Radar Imaging and Microwave Photonics (Nanjing University of Aeronautics and Astronautics), Ministry of Education, Nanjing, 210016, China;2. College of Civil Aviation, Nanjing University of Aeronautics and Astronautics, Nanjing, 210016, China)

In order to realize low distortion acquisition and processing for wideband radar signal in the wideband radar system, a wideband and low spurious sampling system with amplitude and phase correction is studied and designed. The system uses the implementation scheme of wideband analog to digital converter (ADC) device and high performance field programmable gate array (FPGA) device, which is researched from low jitter sampling clock, low noise power, anti crosstalk for the optimal low spurious performance. To improve the band transmission characteristics of the system, a finite impulse response(FIR) filter is designed based on optimization algorithm. Finally, the designed system is tested in lab, and the experiments results prove that the spurious-free-dynamic-range (SFDR) of the system is characterized as -50 dBc worst-case over an instantaneous bandwidth of more than 800 MHz, sampling rate of 1.8 GS/s, quantization length of 8 bits. System performance levels meet the application requirements of wideband radar signal acquisition, wideband radar target imaging and wideband radar target echo reconstruction.

wideband sampling system; low spurious; amplitude and phase correction; FIR filter

国家自然科学基金(61071164,61271327)资助项目;江苏高校优势学科建设工程资助项目。

2014-05-20;

2015-06-12

TP274

A