基于FPGA的DDR3 SDRAM控制器设计及实现

2016-12-22进张览刘

韩 进张 览刘 锴

(1.山东科技大学计算机科学与工程学院,山东 青岛 266590;2.山东高云半导体科技有限公司,山东 济南 250000)

基于FPGA的DDR3 SDRAM控制器设计及实现

韩 进1张 览1刘 锴2

(1.山东科技大学计算机科学与工程学院,山东 青岛 266590;2.山东高云半导体科技有限公司,山东 济南 250000)

文章基于Verilog语言设计并实现了一款基于高云FPGA芯片的DDR3 SDRAM控制器系统。本设计以GW2A55作为核心,参照JESD79-3F工业标准定义的DDR3 SDRAM时序操作、状态转换、接口定义等规范,实现了控制器的设计。设计主要分为控制层和物理传输层两个逻辑层级。通过综合验证本设计数据传输接口的速率可达到800Mhz,高负载运行下错误数据校准率为100%,芯片逻辑资源占用率低于6.5%,因此能够满足用户对高速数据传输以及可靠性和低资源占用的要求,同时具备同家族芯片可移植性强的优势,并给出了系统功能仿真的验证结果。

FPGA;高云GW2A55;DDR3 SDRAM控制器;JESD79-3F

1 引言

DDR3 SDRAM是由 JEDEC在 DDR SDRAM 的基础上进行开发的内存技术标准,相对于 DDR SDRAM,其优势非常明显,使用SSTL 1.5作为核心电压具有更低的功耗,采用“Fly-by”拓扑结构提高了信号完整性,具有8n-bit预取结构且在时钟的上下沿均传输数据,从而大大提高了传输速率。但是由于DDR3 SDRAM操作时序繁多,模式寄存器参数众多,工作状态转换复杂,需要有专门的控制器对它的读取、写入、刷新、预充电等进行控制。本设计目的就是充分利用FPGA逻辑资源,设计一种合理、可靠、符合实际应用且成本低的DDR3 SDRAM 控制器。论文给出整个控制器的系统设计方案,并搭建了testbench用于验证设计的有效性,同时给出读写数据的RTL级仿真测试结果。

2 系统硬件设计

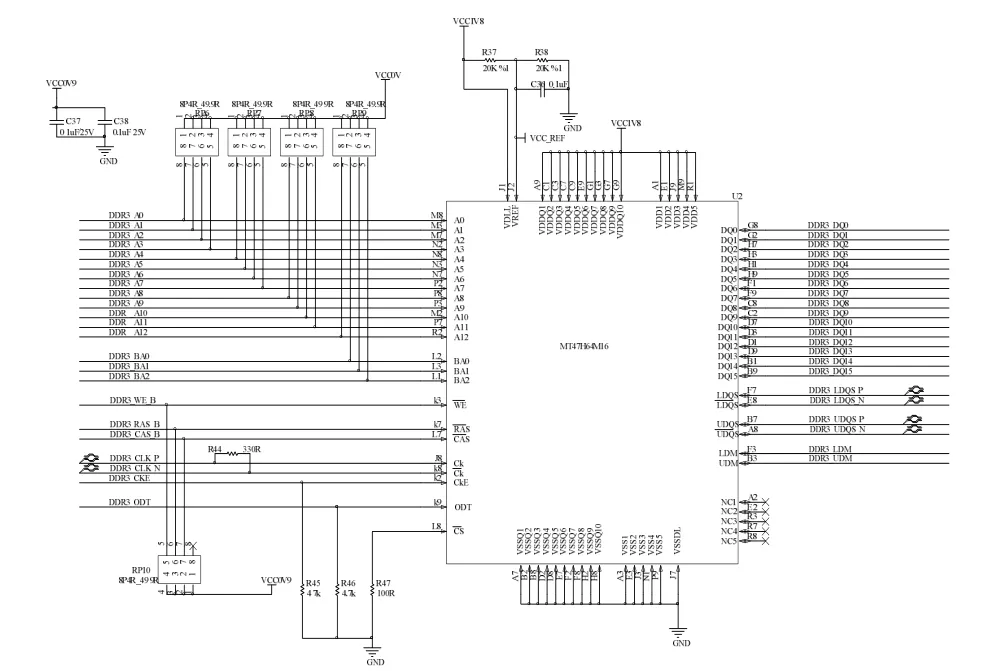

本设计的硬件平台使用高云半导体55nm 制程PBGA484封装的GW2A55芯片,拥有320个用户可用管脚,具有低功耗、高性能和丰富的逻辑资源,且支持DDR3 SDRAM所使用的所有单端和差分电平标准。搭载GW2A55的开发板配置有外置镁光 128MB X8位 DDR3 SDRAM 存储芯片MT47H64M16HR-3,PCB上与GW2A55使用点对点连接,其电路连接原理图如图1所示。

图1 DDR3 SDRAM连接管脚图

GW2A55产品的I/O 包括8个Bank,每个Bank有独立的I/O 电源VCCO。为支持SSTL、HSTL 等I/O 输入标准,每个Bank还提供一个独立的参考电压VREF。GW2A 系列FPGA 产品不同的Bank支持不同的片上电阻设置,包括单端电阻和差分电阻两种。单端电阻用于SSTL、HSTL的输入输出,差分电阻用于LVDS输入。开发板中提供了一个外部输入50MHz晶振和一个100MHz晶振,这两个时钟均可以作为FPGA内部PLL的时钟输入。通过PLL的分倍频可以输出不同的时钟并经过通用IO输出。时钟原理图如图2所示。

图2 时钟电路图

为了方便FPGA程序调试,在FPGA外面加了一个硬复位电路,通过按键K8、R16、C8电路实现。SYSRST_N对应FPGA管脚为N19。电路原理图如图3所示。

图3 复位电路连接图

3 系统软件设计

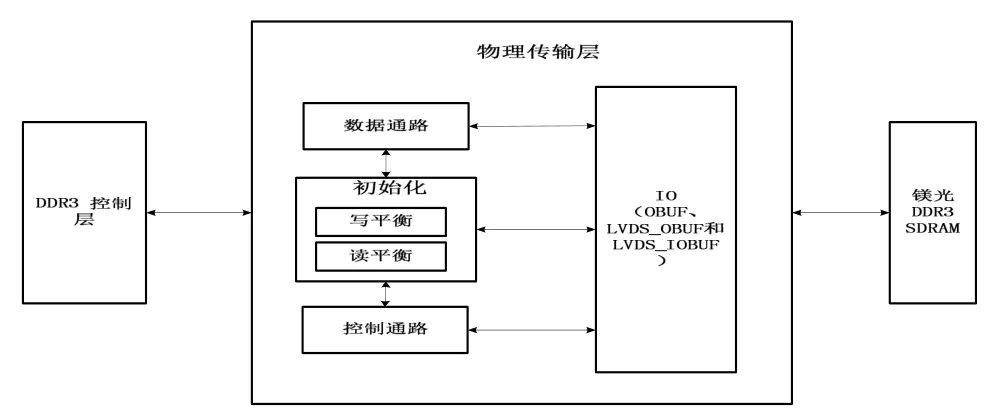

控制器屏蔽了内存操作的复杂性,用户只需要对控制器提供的接口进行简单的时序操作就可以对内存进行高效的读写。DDR3 SDRAM控制器逻辑体系结构主要由物理传输层及控制层构成,同时也包含时钟模块。用户层将内存访问请求发送到控制层,控制层对用户请求进行处理后再发送到物理传输层,最终由物理传输层按照内存的时序操作要求将命令、地址、数据传输至内存。物理传输层也会接受来自内存的信号,并将信号处理后发送至控制层,然后将信号转换成用户能识别的信号格式发送到用户层。控制器由Verilog语言实现,软件开发环境使用高云半导体自主研发的新一代FPGA开发环境,支持 GW2A系列FPGA产品,能够完成综合、布局、布线、产生数据流文件及bit流下载等一站式工作。控制器逻辑结构设计图如下图4所示。

图4 控制器逻辑结构框图

3.1 控制器控制层设计

DDR3 SDRAM控制器控制层主要完成以下功能:

①将来自用户的对 DDR3 SDRAM的操作请求进行转换,包括激活、读、写、自动预充电读、自动预充电写以及预充电等命令。

②地址空间映射,将用户发送的地址映射到相应的Bank、Row、Col,进入、退出自刷新模式。

③支持Burst Mode为4n、8n,以及OTF。

④支持ECC数据校验(数据位宽为64位时)。

控制层介于用户层和物理传输层之间,控制层的内部采用的是模块化设计,依照控制层要完成的功能以及相关的特征需要对控制层按照不同功能进行划分包括如下功能模块:Rank及Bank管理模块、数据管理模块、初始化管理模块、Core核心处理模块、ECC数据校验模块、数据通道模块及FIFO模块。控制层逻辑框图如图5所示。

图5 控制器控制层逻辑框图

3.2 控制器物理传输层设计

物理传输层用于连接控制层和DDR3 SDRAM。物理传输层与控制层之间的接口符合 DDR PHY Interface(DFI)工业标准,同时兼容DDR2 SDRAM(通过Parameter进行配置),最高支持800Mhz的数据传输速率,DQ(物理传输层数据位)可以配置成8至72之间各种不同位宽,支持Burst Length4、Burst Length8和OTF模式,支持CWL、CL和AL等参数不同值的配置。

DDR3物理传输层主要完成以下工作:

①接收来自DDR3 SDRAM内存控制器控制层的命令,对DDR3 SDRAM进行数据读写操作。

②完成DDR3 SDRAM的初始化,对DDR3 SDRAM各个模式寄存器进行配置。

③完成初始化过程中DDR3 SDRAM的时钟和复位信号的处理。

为了满足信号的完整性要求,时钟、地址、命令在 PCB版走线时可采用“Fly-by”拓扑结构,但会造成DQS和时钟信号之间的歪斜,因此物理传输层必须支持写平衡。写平衡就是完成自动补偿各个 DQS信号组和时钟信号组之间的歪斜。时钟信号组和各个DQS信号组组内的信号不用调整,因为内存芯片PCB走线时采用分组对齐的策略,组内的信号都是对齐的。同时,也必须支持读平衡,读平衡则是为了使得DQ能够被正确的捕获到,主要是根据DQS的相位来调整用于捕获DQ的时钟相位。物理传输层的逻辑结构如图6所示。

图6 物理传输层

控制通道需要完成地址、命令时钟域的转换,然后将控制层的命令、地址信号转化成符合DDR3 SDRAM命令格式的信号,最后调用 ODDR硬核按照操作时序发送给 DDR3 SDRAM。数据通道用来处理用户数据,将数据转化成内存芯片能识别的数据格式。每一个数据通道能够处理一位DQS和8位DQ,调用多少个通道由DQS及DQ的宽度决定。该模块工作时会调用 FIFO对发送和接受的数据进行时钟域的转换,然后调用输入解串器ISEDES4、输出解串器OSERDES4和处理DQS的硬核模块,最终使用IO口完成数据的发送和接受。物理传输层的初始化模块配合控制层完成 DDR3 SDRAM的初始化工作,同时也包括写平衡、读平衡两个重要的处理过程。

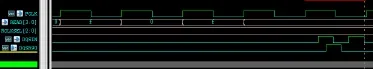

在GW2A55中,控制器是使用DQS硬核的输出DQSW0来产生DQS信号的,在DQS硬核模块中DQSW0会根据输入 WSTEP[7∶0]的值产生延迟,因此调整 WSTEP[7∶0]的值可以调整DQS的相位,也就可以实现写平衡调整。如图7、图8是写平衡的调整图。

图7 写平衡调整之前

图8 写平衡调整之后

从仿真波形中可以看到,写平衡调整之前到达 DDR3 SDRAM端的CK和DQS之间有歪斜,写平衡通过调整DQS的延时使得最终DQS和CK对齐。DDR3 SDRAM在PCB布线时遵守分组对齐的原则,所以DQS与CK的对齐保证了数据信号线和控制信号线的对齐。

读平衡的目的之一是恢复出正确的 DQSR90,物理传输层会用DQSR90捕获DQ,主要是通过调整DQS硬核模块中的 RCLKSEL[2∶0]和 READ[3∶0]的值来实现。如图 9、图 10所示是读平衡的仿真波形,由图可以看出经过读平衡调整之后DQSR90才是DQSIN经过90度相位延迟之后的信号,此时DQSR90的边沿刚好在DQ数据的中间,数据的稳定性最强,所以系统就会用这个时钟来捕获正确的DQ。

图9 读平衡之前

图1 0 读平衡之后

3.3 时钟模块

图11 时钟设计图

控制层与物理传输层的时钟比例为固定的 1∶4,从 PCB板上引入的时钟CLK经过PLL之后生成了同频的clk_x1、4

倍频的clk_x4、clk_x4_p,clk_x4经过CLKDIV模块之后被2分频生成了clk_x2。物理传输层内部会用到clk_x1、clk_x2、clk_x4、clk_x4_p这四个时钟,控制层工作在clk_x1时钟域,且发送给物理传输层的所有信号都应该与 clk_x1同步。PLL的倍频倍数根据需要进行调整,比如PCB板载50Mhz时钟源,需要使用800Mhz的数据传输速率,那就需要对50Mhz进行8倍频产生400Mhz的时钟信号,时钟信号上下沿均采样数据,则就会产生所需要的800MHz的数据传输速率。

4 仿真验证结果

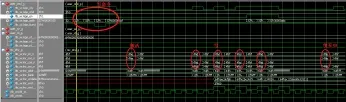

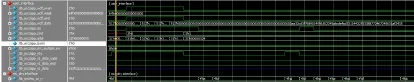

功能仿真是FPGA软件设计和应用中的重要一步,设计完成之后需要对其进行RTL级功能仿真,来验证本设计是否与预期一致,以及是否符合设计规范,同时也可以检查设计中的不足之处来予以改进。以下是搭建testbench之后实际的仿真结果。如图12所示为写数据仿真结果。

图12 写同Bank同行仿真结果图

在图12中,给出了连续4次写同一个Bank的同一行的情况。由控制层首先生成一个激活命令,激活该行,然后后面生成四个写命令,完成之后跟一个预充电命令。

如图13所示为带预充电、不带预充电的写操作及含有数据掩码的仿真结果。

图13 预充电及数据掩码仿真结果

图13给出了写同一个Bank不同行的情况。由控制层首先生成激活Bank及行的命令,然后生成带预充的写命令(地址位A10为1),最后行地址增加激活同Bank及不同行,生成不带预充电的写命令。图中的第二个写操作给出的数据掩码为8’h09,可以观察到在控制层的mc_wrdata_mask信号中也出现了该值。

如图14所示为读数据仿真结果图。

图14 读数据结果图

从图14仿真结果图中可以看出用户层给出了读请求,在控制层解析产生了相应的命令并传递给了物理传输层,最终由DDR3 SDRAM相应用户请求读出用户之前写入的数据。

如图15给出了Burst Mode为4,ECC为“ON”的情况下,写入数据的仿真图,64位的数据在经过ECC校验之后,生成8bit校验码,将一共72bit数据发送给物理传输层。

图15 ECC校验仿真图

5 结语

通过对JESD79-3F规定的DDR3 SDRAM规范、操作时序、特性以及物理结构进行分析,将控制器分成控制层及物理传输层两层逻辑结构,使用Verilog语言实现了控制器的设计,同时对设计进行了功能仿真,结果证明了设计的可行性,能够满足对DDR3 SDRAM的高速读写操作。该设计可在所有高云GW2A家族芯片之间进行高效的移植,缩短了软件设计的开发周期,降低了开发成本。

[1] 王巍.高性能FPGA系统:时序设计与分析[M].北京∶高等教育出版社,2014∶58-102.

[2] 杨军.基于FPGA的DDR3控制器IP设计与研究[D].南京∶南京航空大学,2015:44-59.

[3] 刘梅.DDR3 SDRAM 控制器物理层DLL的设计与实现[D].长沙∶国防科技大学,2011∶11-18.

[4] 张永志.DDR2 内存控制器的模块设计和验证平台技术研究[D].合肥∶合肥工业大学,2010∶33-36.

Design and implementation of DDR3 SDRAM controller based on FPGA

Using Verilog -HDL, Design and Implementation of DDR3 SDRAM Controller Based on Gowin FPGA, development Board useing GW2A55 as the core chip of the design. Refersto JESD79-3F Industry Standard which definition DDR3 SDRAM Operation Timing, finally Implementing the design.The design,data rate 800Mhz,calibration rate 100%,occupancy rate 6.5%,can meet the requirement of high-speed data transmission, system reliability, low resource utilization, high portability, at last given the waveform result of simulation.

FPGA; Gowin GW2A55; DDR3 SDRAM controller; JESD79-3F

TP399

A

1008-1151(2016)10-0001-04

2016-09-10

山东省自然科学基金资助(ZR2015DM013)。

韩进(1968-),女,山东青岛人,山东科技大学计算机科学与工程学院教授,博士,硕士生导师,研究方向为嵌入式计算机控制、计算机系统结构、电子电路;张览(1990-),男,山东菏泽人,山东科技大学计算机科学与工程学院硕士研究生,研究方向为嵌入式系统技术;刘锴(1986-),男,山东烟台人,山东高云半导体科技有限公司高级软件工程师,硕士研究生,研究方向为嵌入式系统技术。