IEEE1588V2路径延迟自动测量和非对称性补偿

2016-12-19黄华明

黄华明

(上海贝尔股份有限公司,上海201206)

IEEE1588V2路径延迟自动测量和非对称性补偿

黄华明

(上海贝尔股份有限公司,上海201206)

介绍了基于I EEEl 588V2的精确时钟同步协议(PTP)系统中为提高普通主时钟与普通从时钟之间时间的同步精度。与此同时,简化设计了一种自动补偿方法,该方法对电路路径延迟的自动测量以及对电路路径延迟造成的不对称性进行硬件上的自动补偿。

I EEE1588V2;精确时钟同步协议;普通时钟;非对称性;补偿

0 引言

精确时钟同步系统的实现是基于IEEE1588V2协议标准的[1],但在IEEE1588V2协议标准中有一个时钟同步算法的前提假设,即在计算从时钟与主时钟的时间偏差时假定主时钟到从时钟的路径延迟等于从时钟到主时钟的路径延迟。而实际上,这种在网络时钟上的主到从以及从到主的双向路径延迟是不可能恰好相等的。幸运的是,在某一种特定的实际应用中,这样的双向路径延迟差总是固定的并且是可以被补偿的。但是,对这种固定的双向延迟差补偿的前提是我们要提前知道这个差值,并且这种固定双向延迟差会随着应用环境的变化而具有一定的离散性。所以,应用环境发生变化后,我们需要重新获取双向延迟差值,并重新补偿。本文描述的方法是通过硬件实时相位检测的办法,在主时钟到从时钟的路径以及从时钟到主时钟的路径上,自动准确地测量设备内部打时戳点与物理端口之间的电路延迟值,并自动计算延迟值的差。这样,即使应用环境发生变化,硬件电路也会实时检测电路延迟值并计算差值。所以,这种方法不仅能够消除由于电路延迟不对称性引起的时间同步误差,而且还大大简化了电路延迟的测量,实现了测量和路径不对称补偿的自动化。

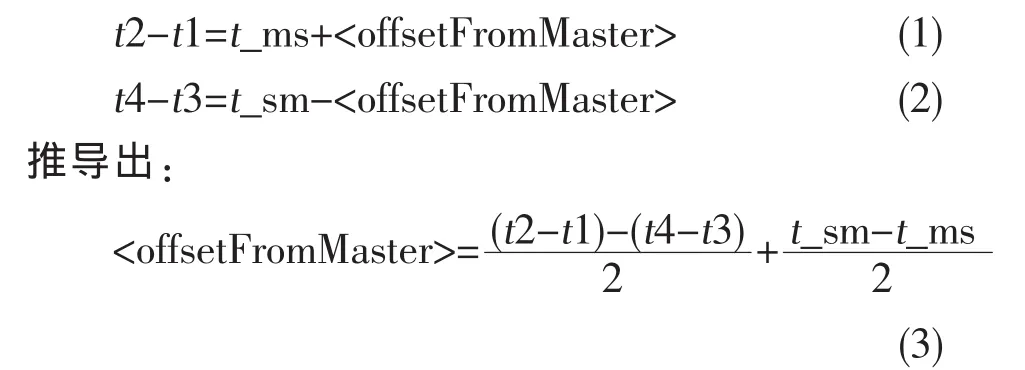

1 IEEE1588V2工作原理

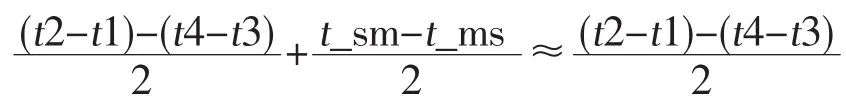

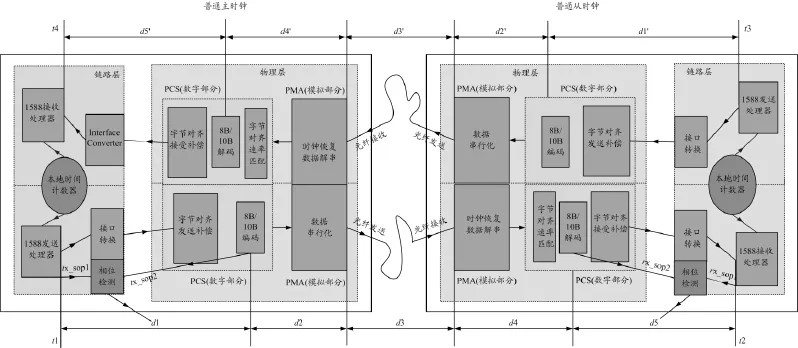

图1所示为PTP时钟同步原理,IEEE1588V2时间事件消息SYNC/Delay_Req/Delay_Resp在普通主时钟与普通从时钟之间进行信息交换,按照one-step模式的时间同步机制如下。t1:当SYNC消息离开主时钟的时刻,基于普通主时钟的本地时间。t2:当SYNC消息到达从时钟的时刻,基于普通从时钟的本地时间。t3:当Delay_Req消息离开从时钟的时刻,基于普通从时钟的本地时间。t4:当Delay_Req消息到达主时钟的时刻,基于普通主时钟的本地时间。t_ms:普通主时钟到普通从时钟的路径延迟。t_sm:普通从时钟到普通主时钟的路径延迟。当一个完整的消息交换周期完成后,普通从时钟获取到所有需要的4个时刻点t1、t2、t3、t4,依据这4个时刻点,即可以通过如下算式计算出从时钟与主时钟的时间差(offsetFromMaster),达到主从时间同步的目的。

图1 PTP时钟同步原理

任何t_ms和t_sm值的不对称都会导致offset-FromMaster计算的误差。而实际上,t_ms和t_sm的差别肯定是存在的。但如果t_ms和t_sm值是固定且已知的,那么我们就可以通过补偿的办法,使得t_ms和t_sm值相等。

本文主要描述如何通过硬件自动测量t_ms和t_sm的值并自动补偿。由于图1中t_ms和t_sm都包括主时钟与从时钟之间的连线延迟及主时钟与从时钟内部电路引起的延迟,而主时钟与从时钟之间的连线延迟总是固定并可预知的,所以在下文中主要讨论主时钟与从时钟内部电路所引起的延迟测量及不对称自动补偿。

2 基于硬件测量和自动补偿的实现方法

本文关注的重点是在实现IEEE1588V2时钟相位同步算法中,双向路径延迟不对称导致的从时钟同步主时钟产生的时间偏移计算偏差问题,而如何自动计算这种路径延迟的不对称并自动补偿[2],在提高同步精度的同时又能简化系统设计,则是我们研究的核心。

在一个系统的实际应用场景中,路径延迟主要包括链路侧电路(由FPGA实现)到物理侧电路(由ASIC芯片实现)的延迟、物理侧电路到物理传输端口(光/电物理接口)的延迟及传输通道(光纤/电缆)的延迟。

图2 原始系统实现方案

2.1 原始设计

图2中,算法依赖的各时刻点及路径延迟表示如下。t1:SYNC消息离开普通主时钟链路侧IEEE1588V2处理器时刻点获取的本地时间。t2:SYNC消息到达普通从时钟链路侧IEEE1588V2处理器时刻点获取的本地时间。t3:Delay_Req消息离开普通从时钟链路侧IEEE1588V2处理器时刻点获取的本地时间。t4:Delay_Req消息到达普通主时钟链路侧IEEE1588V2处理器时刻点获取的本地时间。d1:普通主时钟中,链路侧IEEE1588V2处理器消息离开点到物理侧编码电路之间的延迟。d2:普通主时钟中,物理侧编码电路到物理输出端口之间的延迟。d3:普通主时钟到普通从时钟光纤/电缆传输延迟。d4:普通从时钟中,物理输入端口到物理侧解码电路之间的延迟。d5:普通从时钟中,物理侧解码电路到链路侧IEEE1588V2处理器消息到达点之间的延迟。d1′、d2′、d3′、d4′、d5′是d1、d2、d3、d4、d5的反向路径延迟,含义是类似的。也就是说,普通主时钟到普通从时钟的路径总延迟t_ms=d1+d2+d3+d4+d5;普通从时钟到普通主时钟的路径总延迟t_sm=d1′+d2′+d3′+d4′+d5′。我们以t_ms为例来分析路径延迟,t_ms中的d2、d4由物理侧芯片的PMA电路引起,d3由光纤/电缆传输引起。这种物理层面处理延迟对于不同的应用场景尽管电路延迟值有差别,但是都是固定的并且能够预先精确测量计算出来的,所以在此我们不予讨论。而t_ms中的d1、d5是由物理侧及链路侧的处理电路引起的,对于不同物理侧电路中时钟切换和编解码的实现以及不同链路侧电路中接口转换和相关功能处理的实现,这个延迟值不是固定的,且离散性较大,最终导致整个路径延迟t_ms的变化较大。

2.2 改进型设计

如图3中所示,在物理侧电路设置一个时间计数器,把消息离开/到达的时刻点位置放置在物理侧的电路中,t1和t2值是基于物理侧电路获取的。这样,消除了d1、d5电路延迟的影响。但是,IEEE1588V2时钟收敛算法是工作在链路侧的。算法收敛后,把主从时钟的时间偏移<offsetFromMaster>设置到链路侧时间计数器上进行时间偏差矫正。所以,在这种改进型设计中,在链路侧与物理侧之间必须有一组时间同步接口信号,将物理侧时间计数器同步到链路侧时间计数器上。这种改进设计尽管消除了d1、d5电路延迟的影响,但增加了电路实现的复杂度,并带来额外的硬件消耗。

图3 改进型系统实现方案

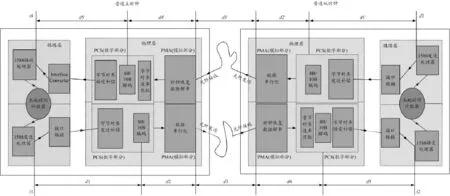

2.3 延迟自动测量补偿技术

延迟自动测量和补偿设计是在原始系统实现方案的基础上,在链路侧增加一个相位检测电路模块,在链路侧电路与物理侧电路之间增加一根物理连接信号线,如图4所示。

在普通主时钟侧,当消息离开链路侧IEEE 1588V2处理器时,记录时刻点t1,同时将发送消息的起始点(记作tx_sop1)送给相位检测模块。当消息离开物理侧编码电路时,通过链路侧与物理侧之间的连接信号线将回送消息的离开起始点(记作tx_sop2)送给相位检测模块。相位检测模块利用tx_sop1和tx_sop2两个标记信号,可自动、快速、精确地计算出路径延迟d1的值。

同理,在普通从时钟侧,当消息到达物理侧解码电路时,通过链路侧与物理侧之间的连接信号线回送消息的到达起始点(记作rx_sop2)送给相位检测模块。当消息到达链路侧IEEE1588V2处理器时,记录时刻点t2,同时将消息到达的起始点(记作rx_sop1)送给相位检测模块。相位检测模块利用rx_sop1和rx_sop2两个标记信号,可以自动、快速、精确地计算出路径延迟d5的值。

最后,通过相位检测模块动态地改变路径的不对称延迟补偿值,达到t_sm和t_ms的自动测量及补偿的目的。

图4 延迟自动测量和补偿系统实现方案

3 结果及分析

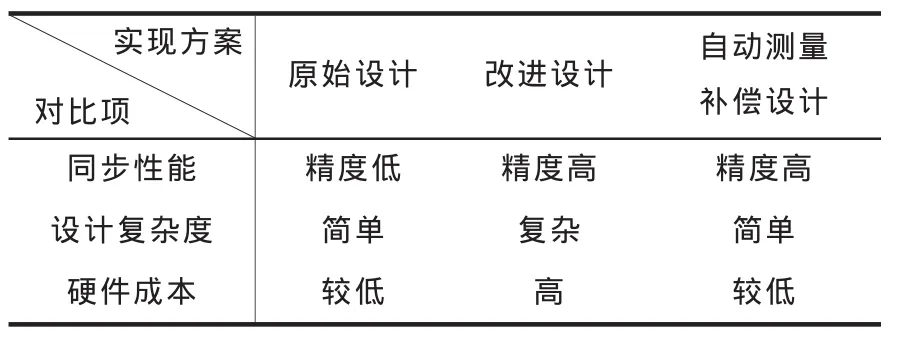

本文描述的新设计方案能够自动测量整个路径延迟中d1和d5的值,为路径非对称性延迟实现了自动化的快速补偿,同时也提高了IEEE1588V2时钟同步收敛算法的精度。另外,相对于其它的改进型设计,本文的方案减少了物理侧与链路侧的系统时间同步功能开发,降低了系统的设计复杂度,同时也减少了物理侧与链路侧芯片接口的连接数量,这些都降低了整个系统的实现硬件成本。表1为几种系统设计方案的对比。

表1 几种系统设计方案对比

4 结束语

基于FPGA的实现,本文提出了一种延迟自动测量和补偿系统实现方案,此项技术被广泛应用于OTN/ PTN网络设备的多种接口板卡上。实际系统同步测试结果表明,本方案将原来时间的同步性能在一个时钟节点上的误差由原先的30ns提高到现在的8ns,同时减少了约80%的路径延迟测量及补偿设置的工作量。

[1]中国移动高精度时间同步1588v2时间接口规范[S].中国移动通信有限公司发布,2010年.

[2]WEN L,ZHANG J,CHEN K.Method and Device for Implementing Automatic Compensation for Asymmetric Delay of 1588 Link.United States Patent Application 20140146811[P].2014.

Path delay auto measure for asymmetry compensating in IEEE1588V2

HUANG Hua-ming

(Alcatel-Lucent Shanghai BellCo.,Ltd.,Shanghai 201206,China)

The paper introduces one way ofimproving the synchronizing precision and simplifying the way of improving synchronizing precision between ordinary clocks(OC)master and ordinary clocks slave in PTP system based on the IEEE1588V2 protocol.The way is the circuit path delay auto measure and auto compensate for asymmetry in the IEEE 1588V2 system by hardware.

IEEE1588V2,PTP,OC,asymmetry,compensate

TN91

A

1002-5561(2016)02-0056-04

10.13921/j.cnki.issn1002-5561.2016.02.017

2015-08-25。

黄华明(1976-),男,FPGA研发工程师,长期从事固网传输芯片开发。