基于CPLD的面阵CCD驱动

2016-12-19赵锡年高鹏飞

赵锡年,瑚 琦,高鹏飞

(上海理工大学 光电信息与计算机工程学院,上海 200093)

基于CPLD的面阵CCD驱动

赵锡年,瑚 琦,高鹏飞

(上海理工大学 光电信息与计算机工程学院,上海 200093)

为实现对面阵CCD的驱动,采集实时图像,设计了电源驱动和数据转换系统。系统采用复杂可编程逻辑器件(CPLD)对一款薄型背照式面阵CCD进行驱动。使用Verilog硬件描述语言(HDL)编写CPLD控制模块,控制CCD的信号采集、信号转移和信号传输。根据CCD的数据手册,设计CCD所需的电源,以便对其进行驱动。利用A/D芯片中的相关双采样(CDS)特点,对输出的视频信号进行处理,过滤视频信号中的复位噪声和1/f等低频噪声,提高系统的信噪比。该系统采用CPLD作为核心控制器件,充分利用了CPLD高速并行且"可编程"的特点,和CCD对环境变化的高度敏感,使得信号采集和传输的速率均较快,且输出视频信号稳定。

薄型背照式面阵CCD;复杂可编程逻辑器件;Verilog HDL

电荷耦合器件(Charge-Coupled Device,CCD)又称图像传感器,广泛应用于天文观察、卫星成像、医学摄像等领域[1]。CCD的基本功能就是将光照射到CCD硅片上产生的电荷进行存储与转移[2],而在存储和转移过程中,常用的CCD一般均存在着易受外界干扰,工作不稳定等缺点,但本文采用薄型背照式CCD。背照式CCD避免了正面结构的吸收损失,其峰值量子效率可达90%以上[3]。同时,在较大程度上避免了外界的干扰等问题。此系统主要是根据S10420-1106-01系列CCD手册,设计CCD的供电模块,并采用CPLD为核心控制模块,控制驱动CCD信号采集、信号转移和信号读取的时序。系统充分利用了CPLD高速并行且“可编程”的特点,简化了硬件设计的难度,能实现CCD的高速采集,成本也大幅降低[4]。此外,系统在信号处理部分,采用相关双采样CDS技术,此方法不仅可较好地滤除复位噪声,且对TDI-CCD传感器的水平时钟驱动及电源地线耦合串扰噪声、传输放大器的白噪声和1/f噪声等成分也有一定的滤除作用[5]。

1 总体设计

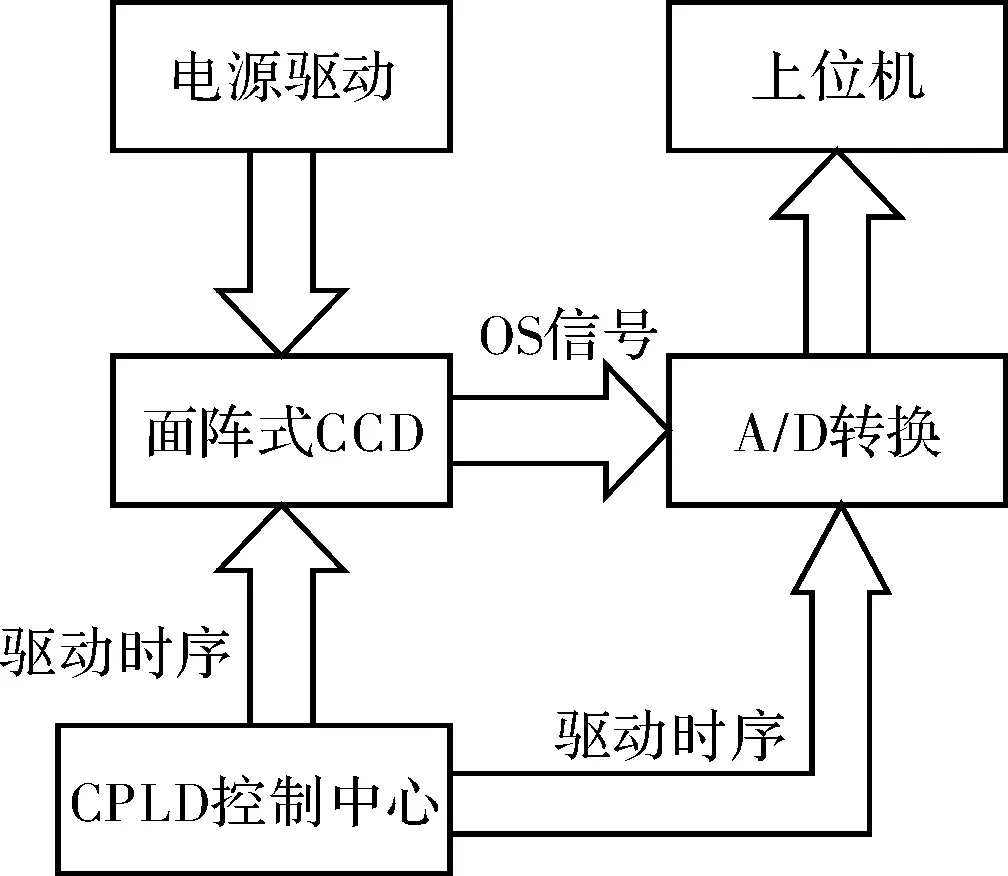

此系统的设计包含了硬件设计和软件设计,但在模块上,又分为电源驱动模块和A/D转换模块。整体采用Altera CPLD为控制核心,控制驱动CCD的垂直位移信号、水平位移信号、累积信号、转移信号和复位信号的输出波形,以及驱动A/D转换芯片的时序波形。其次,电源模块是以5 V电源通过电源转换芯片获得CCD所需的各种电压及CPLD的驱动电压;A/D转换模块是将CCD采集得到的信号OS转换为数字信号,便于上位机的处理。系统框图如图1所示。

图1 CCD采集系统框图

1.1 参数说明

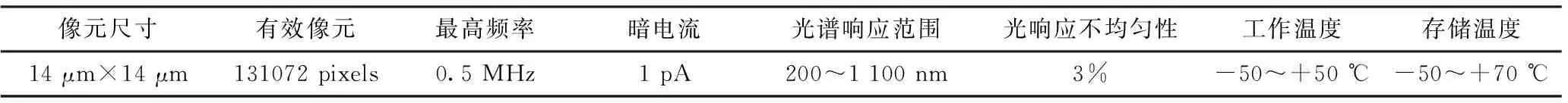

系统所驱动的CCD是Hamamatsu公司的S10420-1106-01系列薄型背照式CCD,作为感光元件,具有更加优良的感光度和噪声低、响应频谱宽等优点,其主要特性参数如表1所示。

表1 CCD主要特征参数

S10420-1106-01系列CCD是一款面阵式CCD,其驱动方式一般有IC驱动、EPROM驱动、DSP驱动、单片机驱动和FPGA/CPLD驱动几种。由于可编程逻辑器件(PLD)设计法实现的系统集成度高、速度快、可靠性好[6],故本系统使用PLD驱动。其工作原理是利用CCD先进行图像信号采集,即对CCD进行曝光,利用像元将光信号转换为电信号,然后通过时序驱动将CCD上所有电信号先纵向转移到厚硅层(Dead Layer),再将每一列收集的电信号传输出去。

1.2 软件设计

软件设计主要分两部分:CCD和A/D转换的时序驱动。

根据S10420-1106-01系列CCD数据手册,CCD的驱动时序主要包含Integration time、Vertical binning period和Readout period这3个阶段[7],具体时序如图2所示。

图2 CCD时序图

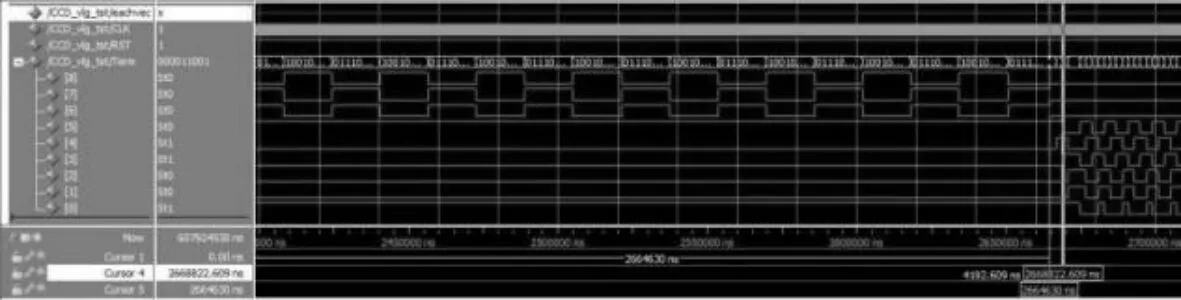

参照数据手册的要求,实现了如图2所示的驱动时序,然后通过Modelsim软件对其进行仿真验证。Modelsim软件是一款优秀的HDL语言仿真软件,其能够提供友好的仿真环境,是FPGA/ASIC设计的首选仿真软件[8]。得到3个阶段的时序具体如图3所示。

图3 Modelsim仿真时序

这里只列出了Vertical binning period和Readout period两段时序的转换阶段。主要是整个时序的周期过长,无法全面且细致的截图,且Integration time和Readout period基本相似,故而只列出转换阶段的时序,表达信号直接的关系。其中,系统时钟频率为50 MHz,Term[8]、Term[7]表示的是P1V、P2V信号,相互之间相差180°,频率为125 kHz;Term[6]表示的是TG信号,与P2V信号同步;Term[5:2]表示的是P1H、P2H、P3H和P4H信号,相互之间相差90°,频率为250 kHz;Term[1]表示的是SG信号,与P4H信号同步;Term[0]表示的是RG信号,只在Readout period阶段有效。

CCD驱动结束后,其输出的OS信号即采集得到的图像信号,且每个像素中均包含复位电平、参考电平和视频信号电平。通常在电荷包转移和复位的过程中,每个电平均会掺入一些噪声。若在输出电荷包之前和输出电荷包之时,在同一像素周期内进行前后两次采样或差分平均,这样两次采样的KTC噪声相差微小,再将两次采样值相减,KTC噪声就被从输出信号中抑制了,且两次采样的间隔越短,复位噪声的抑制能力则越强,这便是相关双采样法[9]。而实验证明,相关双采样对这样的噪声处理是最为有效的手段,故而选择AD9826芯片作为A/D转换芯片。AD9826可配置成6种不同的操作模式,且根据CCD输出的形式选择其中的1-Channel CDS模式。CDS驱动时钟信号为CDSCLK1和CDSCLK2,二者均在下降沿处采集信号[10]。CDSCLK1为第一次采样触发信号,CDSCLK2为第二次采样触发信号。在ADCCLK下降沿处采样经过CDS处理后的电平信号。

1.3 硬件设计

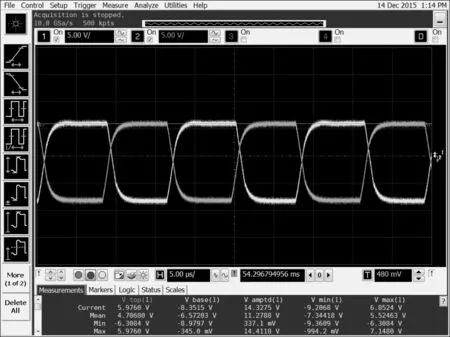

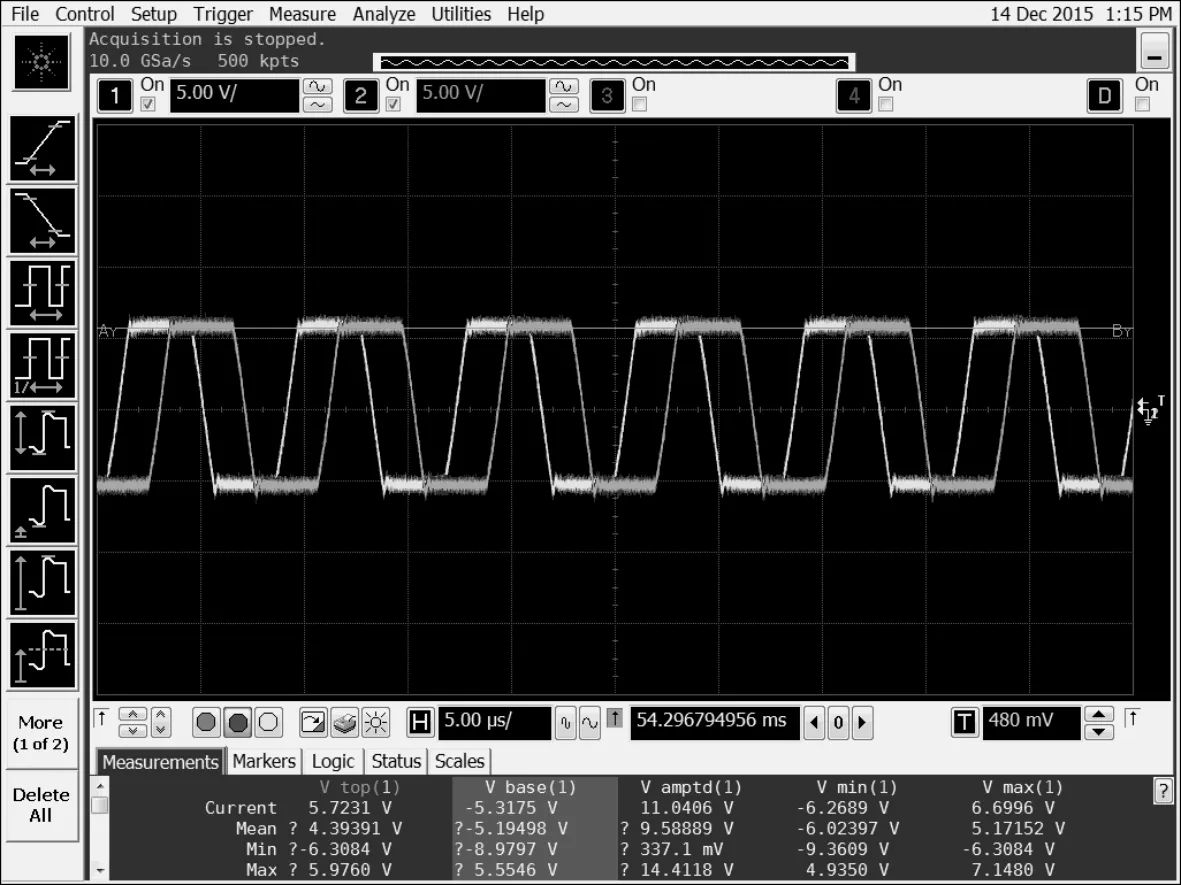

根据数据手册可知,驱动S10420-1106-01系列CCD,所需的电源种类较多,如水平和垂直方向的测试点所需的-8 V电源,溢出门需要的+12 V电源,输出门需要的+5 V电源,输出晶体管漏极需要的+24 V电源,以及对运放供电的±15 V电源和对CPLD供电的+3.3 V电源。这些电源均使用+5 V电源升压或降压产生。其次,CPLD输出的时序波形幅值均是+3.3 V的,故而需使用运放对其放大,然后和-8 V电源叠加或是与+5 V电源相减产生所需时序波形和相应的电位。PV信号的时序波形和PH信号其中两个时序波形,如图4和图5所示。

图4 P1V和P2V的时序波形

图5 P1H和P2H的时序波形

电源驱动模块驱动CCD成功后,CCD则可正常输出图像的模拟信号OS。但实际中得到的信号较为微弱,基本看不出复位电平、参考电平和视频信号电平的变化,所以在AD9826之前再添加一个运放,对其信号进行放大,以便于处理。在电源驱动过程中,CCD信号采集难免掺杂诸多噪声。因此,在A/D模数转换模块采用AD9826,并利用其相关双采样(CDS)的特性,可滤除诸多噪声。

2 实验结果与分析

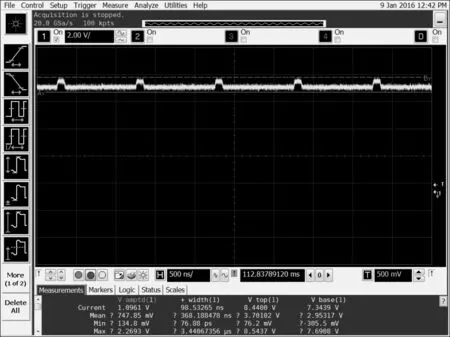

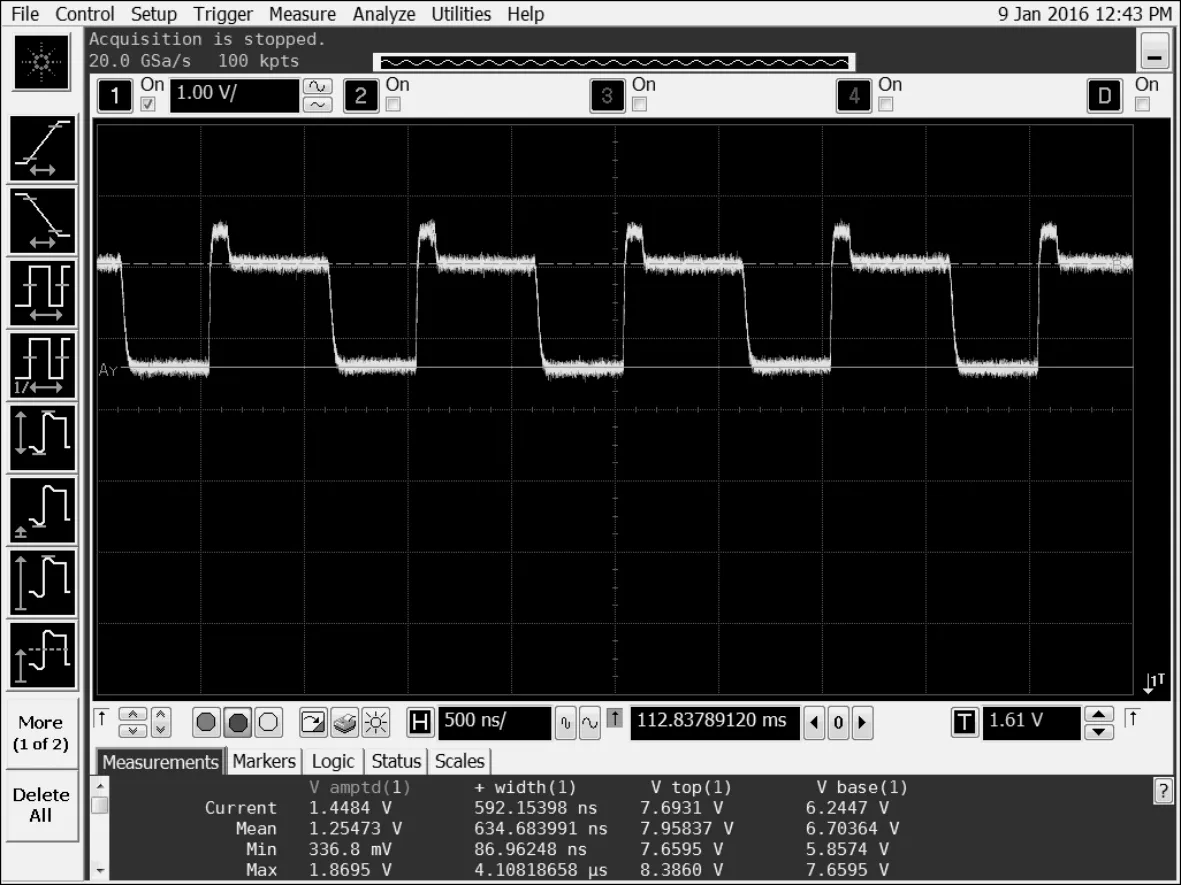

成功驱动S10420-1106-01系列CCD之后,需要对其输出的信号进行观察和分析。根据CCD的特性可知,CCD对于光照环境和暗室环境,采集得到的信号分别是处于饱和与非饱和状态。对于这两种状态的截图分别如图6和图7所示。从图7非饱和状态的信号输出图中可分辨出信号的复位电平、参考电平和视频信号电平,然后A/D再对参考电平和视频信号电平取电位差,即可得到该像素采集到的图像信号。最后,将获得的电位差发送给上位机,再利用上位机复原出原先采集的图像。通过信号的饱和状态与非饱和状态的波形图可以看出,此系统已成功驱动了该款CCD,且采集的图像信号噪声较小,故此方案具有可行性且精度高。

图6 饱和状态

图7 非饱和状态

3 结束语

总体而言,此次设计的S10420-1106-01系列CCD驱动系统性能较好。CCD采集到的信号噪声较小,基本在可接受的范围内,且环境变换在一定的范围内系统工作较为稳定,这主要得益于此CCD是一款薄型背照式CCD,在信号采集的初期就过滤了较大部分的光噪声。同时,系统充分利用了CPLD高速并行且“可编程”的特点和CCD对环境变化的高度敏感,使得信号采集和传输的速率均较快。此外,本设计具有一定的通用性,对于相似的CCD,只需对其电源驱动模块和相应的程序稍作修改即可。

[1] 王庆有.图像传感器应用技术[M].2版.北京:电子工业出版社,2013.

[2] 颜伟彬.CCD信号数据采集及处理[D].武汉:华中科技大学,2004.

[3] Schaefer A R,Varain R H,Cover J,et al.Megapixel CCD thinning/backside progress at SAIC [J].SPIE,1992,16(5):41-49.

[4] 于庆广,张晓明,王浩,等.CCD视频采集系统设计和实现[J].仪器仪表学报,2006,27(z2):1365-1366.

[5] 张林,李永新,胡学友.基于相关双采样技术的CCD视频信号处理研究[J].宇航计测技术,2007,27(2):33-37.

突发数据流带来的溢出情况。在通信用集成电路方面有降低功耗及后续设计难度的意义。

参考文献

[1] 黄小猛,林闯,任丰源.高速传输协议研究进展[J].计算机学报,2006,29(11):1901-1908.

[2] 徐勇军.集成电路功耗估计及低功耗设计[D].北京:中国科学院计算技术研究所,2006.

[3] 蒋文栋.数字集成电路低功耗优化设计研究[D].北京:北京交通大学,2008.

[4] 邓亮,赵进,王新.网络编码下的编码开销-链路开销联合优化[J].计算机研究与展,2010,47(3):390-397.

[5] 邓亮.网络编码优化研究[D].上海:复旦大学,2008.

[6] 张威威.晶振老化漂移的建模与补偿[D].西安:西安电子科技大学,2012.

[7] 郭淦.高速串行通信中的时钟恢复技术[D].上海:复旦大学,2005.

[8] 薛畅,王建赜,纪延超,等.具有高动态性能和锁相精确度的改进PLL设计[J].电机与控制学报,2014,18(8):116-120.

[9] 胡波,李鹏.异步FIFO在FPGA与DSP通信中的运用[J].电子科技,2011,24(3):53-55,61.

[10] 胡上,陈小林,王祝盈,等.具有良好压控特性的压控晶体振荡器的设计[J].宇航计测技术,2009,29(6):60-65.

Driving the Area Array CCD Based on CPLD

ZHAO Xinian,HU Qi,GAO Pengfei

(School of Optical-Electrical and Computer Engineering, University of Shanghai for Science and Technology,Shanghai 20093, China)

In order to implement the driven of area array CCD and collect real-time image,we have designed a power driven and data conversion system. Based on the extensive use of CCD, this system drives a back-thinned area array CCD by the complex programmable logic device(CPLD). The CPLD control module is written in Verilog hardware description language (HDL), which is used to control the CCD’s signal acquisition, signal transfer and signal transmission. According to the CCD data sheet, designing some power which the CCD needs to drive the CCD. Handling the output video signal and removing the low frequency noise such as reset noise and 1/f in filtered video signal and improving the SNR of system by the characteristics of the correlated double sample (CDS) of A/D chip. The system uses the CPLD as the core control device and makes full use the characteristics of CPLD, such as the high-speed parallel , "programmable" and the highly sensitive to the environment changing to make the speed of the signal acquisition and transmission speed be fast, and to make the output video signal be stable.

back-thinned area array CCD; complex programmable logic device; Verilog HDL

2016- 01- 15

赵锡年(1991-),男,硕士研究生。研究方向:光电检测,嵌入式应用等。

10.16180/j.cnki.issn1007-7820.2016.11.011

TN386.5

A

1007-7820(2016)11-035-04