基于FPGA的PClE总线DMA传输的实现

2016-12-06张鹏泉褚孝鹏曹晓冬范玉进

张鹏泉,褚孝鹏, 曹晓冬,范玉进,汪 振

(天津光电集团公司,300211)

基于FPGA的PClE总线DMA传输的实现

张鹏泉,褚孝鹏*, 曹晓冬,范玉进,汪 振

(天津光电集团公司,300211)

为了实现不同应用条件下对高速数据传输的不同要求,本文提出一种基于FPGA的PCIE DMA传输结构及其实现方法,可以利用不同的工作模式灵活应对不同的高速数据传输需求,有效地将上位处理器从数据传输工作中解放出来,具有移植性强,传输效率高,数据负荷长度灵活等特点。

FPGA;PCLE;DMA传输

随着电子器件运算速度的高速发展,尤其是在宽带高速信号采集、数据高速存储、图像处理等领域,新出现的器件和设备对数据的传输速度和带宽有了更高的要求。PCI Express总线作为第三代I/O总线的代表,能够通过差分链路来提供高性能、高速、点到点的串行双工数据传输,可以对单板上的分层总线结构提供最理想的支持,已经被广泛应用到计算机与各种外设组件之间的互连领域。

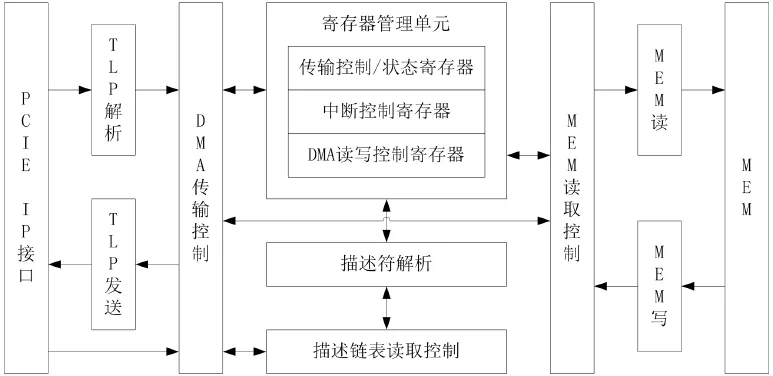

图1 DMA控制器结构图

目前,市场上可以使用的PCIE桥接芯片种类较少,且往往受到链路宽度的限制,所以单纯使用桥片与USB3.0等其它总线相比并不具有明显优势。另一方面,目前主流的FPGA供应商均支持PCIE IP核,基于FPGA的设计可增大系统灵活性,稳定性,板卡的速度快,可扩展性强,系统集成度高,所以使用FPGA实现PCIE链路成为越来越多开发者的首选。本文提出一种基于FPGA的PCIE DMA传输控制器的实现方式,可以灵活适应不同速率、不同链路带宽的IP核设置,具有移植性强,传输效率高,数据负荷长度灵活等特点,可以有效地将上位处理器从数据传输工作中解放出来,为数据的高速传输与高效处理提供了优秀的技术支持。

图2 DMA传输控制单元结构图

图3 描述符链表结构

图4 直接传输读TLP及中断控制信号

图5 直接传输写TLP

DMA控制器实现了3种传输模式,直接传输模式,直接DMA传输模式和描述符DMA传输模式,其结构如图1所示。直接传输模式由上位处理器直接发起读/写TLP,由端点FPGA执行,此种模式适用于数据传输量较小的寄存器读写或者数据传输地址和长度相对度固定的批量数据传输。直接DMA传输模式由上位处理器发起并提供必要的控制信息,由端点FPGA发起读/写TLP,实现数据交换,此种模式适用于传输数据的地址和长度相对固定,但需要多次传输或数据量较大的情况。描述符DMA传输模式则由上位处理器建立描述符,其中包含传输地址、长度、方向等信息,然后将描述符组成描述符链表,将链表的起始地址、长度等信息提供给端点FPGA;端点FPGA则依次读取链表中的描述符,解析后发起读/写TLP,完成传输操作,直到链表结束,此种模式适用于传输数据的地址不断变化,传输数据较少且传输次数较多的情况。

DMA传输控制器的核心处理环节为DMA传输控制,其结构如图2所示,主要功能包括:

1)根据PCIE IP核提供的基址维护一个1KB的控制状态寄存器地址空间;

2)所有对寄存器地址空间的读/写操作均认为是直接读写模式,且数据长度固定为1DW;

3)确保读/写过程的独立性;

4)根据寄存器的状态进行数据传输逻辑和时序控制;

5)读操作中的完成维护。

DMA传输控制器的关键数据结构为描述符链表,其结构如图3所示。其中,所有地址均采用DW对齐方式,源地址为读取数据的起始地址,目标地址为存储数据的起始地址,链接地址为下一个描述符的起始地址。在传输控制信息中,则包括了以DW为单位的传输数据长度,传输方向和首尾DW中以字节为单位的数据有效标志位。

根据以上设计思路,由上位处理器发起的直接传输读TLP及其中断控制信号如图4所示,直接传输写TLP如图5所示。

在PCIE×8链路条件下,由上位PC机发起,由端点FPGA执行的描述符DMA传输模式数据速率测试如表1所示。

如表1所示,在回环测试中数据量一定的条件下,随着数据报文长度增加,报文数据数量减小,处理器干预传输的次数减小,整体的数据传输速率呈上升趋势,且随着上位处理器的速率提高有进一步跃升。

综上所述,本文基于FPGA所实现的DMA传输控制器,不依赖于特定的FPGA平台,速率和链路带宽均可灵活配置。同时,可以利用不同的工作模式灵活应对不同的高速数据传输需求。目前,该设计已经在多个产品平台中获得应用,效果良好。

[1]王齐.PCI Express 体系结构导读.机械工业出版社.2010.3

[2]刘军伟.多种高速串行总线的对比研究与分析.电子测试.2016.03

[3]李晓宁,姚远程,秦明伟.基于PCIe的高速接口设计.微型机与应用,2016,35(1):27~29,32

[4]肖明国 ,董明利,刘锋,娄小平,祝连庆.基于PCIe总线的数据采集卡设计与实现.计算机测量与控制.2016.24(3)

Implementation of PCIE bus DMA transmission based on FPGA

Zhang Pengquan,Zhu Xiaopeng*,Cao Xiaodong,Fan Yujin,Wang Zhen

(Tianjin photoelectric group company,300211)

In order to realize different application conditions of high-speed data transmission requirements is proposed in this paper a based on FPGA PCIe DMA transmission structure and its realization method,you can use different operation modes of the flexible respond differently to the high-speed data transmission requirements,effectively will host at the processor to be liberated from the data transmission,has strong portability,high transmission efficiency,the length of the data load flexible features.

FPGA;PCLE;DMA transmission

表1 描述符DMA传输模式数据速率测试表