低功耗高速时钟数据恢复电路①

2016-12-05孟时光杨宗仁

孟时光 杨宗仁

(*计算机体系结构国家重点实验室(中国科学院计算技术研究所) 北京 100190) (**中国科学院计算技术研究所 北京 100190) (***中国科学院大学 北京 100049)

低功耗高速时钟数据恢复电路①

孟时光②******杨宗仁***

(*计算机体系结构国家重点实验室(中国科学院计算技术研究所) 北京 100190) (**中国科学院计算技术研究所 北京 100190) (***中国科学院大学 北京 100049)

为了降低高速串行接口的时钟数据恢复(CDR)电路的功耗,在研究、分析现有时钟数据恢复结构的基础上,提出了一种新的时钟数据鉴相算法及其电路实现方法。新的电路设计仅使用一个高速采样时钟,比传统的鉴相电路减少一半的采样率,从而减少了前端采样模块的功耗。该鉴相算法采用统计方法减小鉴相时钟的噪声,进而达到很低的误码率。该鉴相算法可使用数字综合的方法实现,工作在较低的频率下,这样便于迁移到不同的工艺中。整个电路使用40nm工艺实现,实际芯片测试数据表明,使用该电路的接收端可以稳定工作在13Gb/s的速率下,功耗达到0.83pJ/bit,误码率低于10E-12。

低功耗接收端, 高速串行接口, 时钟数据恢复(CDR)

0 引 言

随着处理器性能的不断提升,处理器对外的数据传输量在快速增长。为了在接口数目有限的情况下达到更大的数据吞吐量,接口的数据速率会越来越高[1]。而且,由于散热功率的限制,接口的功耗并不能随数据速率增高而增长,在此情况下,原有的并行数据接口无法达到较高的速率。现代处理器对外的接口主要采用串行接口,如HT (HyperTransport)[2]、PCI-E[3]、QPI (QuickPath Interconnect)[4]等。串行接口主要分为源同步及非源同步两种结构,但无论哪种结构,由于电路板上走线匹配度受限,其高速时钟和数据很难保证完全对齐。因此,在高速串行接口中,接收端收到的数据和时钟需要时钟数据恢复电路来重新对齐。由于芯片整体功耗的限制,接收端的功耗要尽量降低,这对于接收端的结构是较大的挑战。

时钟数据恢复电路的主要作用是判断当前时钟和数据的相位关系,将时钟调整到最适合采样的位置上。这样可以降低采样的误码率,使整个互联系统能稳定工作。传统的时钟数据恢复电路主要有三种结构。第一种结构最常见,采用边沿检测法[5],使用一对正交时钟检测到边沿位置,然后调整采样时钟的位置向前或向后。此方法得到的采样时钟有较大的抖动噪声,而且对数据占空比的要求较高。第二种结构采用数据沿跟随[6]方法,在采样时钟前后有另两个边沿检测时钟。此方法输出的状态有三种,即提前、推后、不变。这种方法可以减小采样时钟的抖动,但需要更多的采样器和采样时钟,并为此付出更多的功耗和面积。第三种时钟数据恢复的结构采用片上眼图检测[7]。这种方法得到的时钟抖动很小,功耗也较小。但是此方法需要两个独立可调的时钟,结构复杂,并且需要较长的锁定时间。本文提出了一种新型的低功耗高速时钟数据恢复结构与算法。在前端采样部分只使用一路采样时钟进行数据采集,通过分析采集到的信号的质量,使用统计方法反推当前采样时钟与数据的关系,然后将采样时钟推向数据中间,降低采样的误码率。本方法使用单路采样时钟,大幅降低了前端采样器的数量和功耗。

1 接收端整体结构

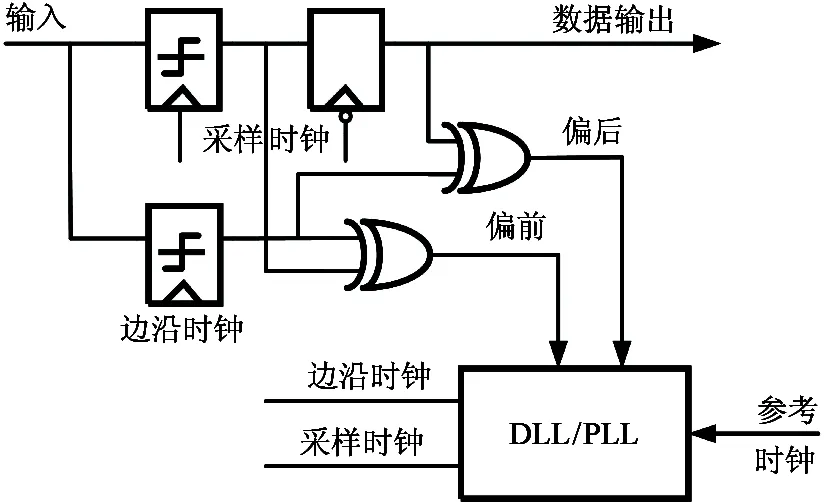

高速串行接口接收端的主要功能是接收外部PCB板上传输的高速模拟信号,并转换为并行数字信号。在高速接口中,数据的时间宽度仅有几十皮秒,时钟和数据在传输过程中无法保证完全对齐。因此,在接收端的时钟和数据需要恢复电路将其重新对齐。传统的时钟数据对齐结构见图1,其中的时钟和数据位置关系的判定使用边沿检测的方法。

图1 传统接收端结构

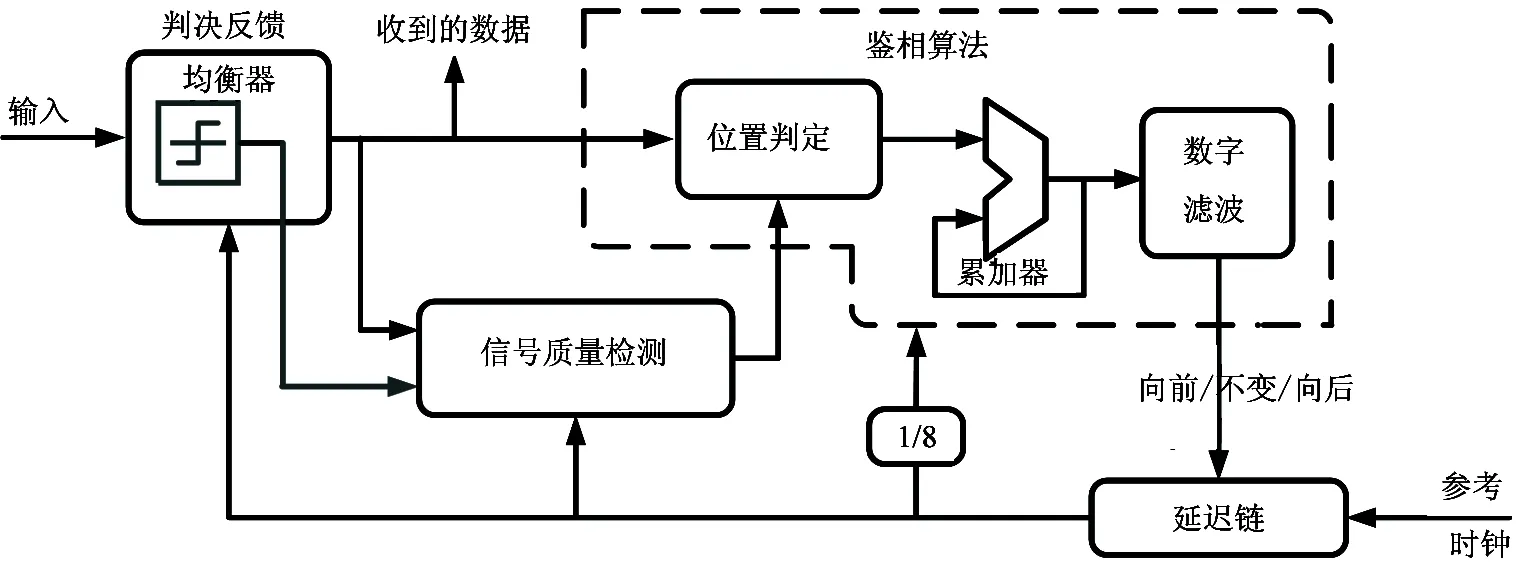

本设计整体结构如图2所示。外部电信号只输入到信号采样模块,不再需要常规的边沿检测模块。之后由内部的信号质量检测模块判断信号质量,标记出信号质量较差的位,再将接收到的数据连同标记一起发送给鉴相算法模块来判断时钟和数据的相位关系。此时判定出的相位关系并不完全准确,有一定出错概率。其后经过累加和数字滤波,才能确定时钟和数据之间准确的相位关系。最后通过数字延迟链对此进行调整,让采样时钟到达最优化的位置,降低采样误码率。

图2 本设计接收端结构

在时钟数据对齐的过程中,采样时钟并没有必要处于数据正中间的位置,时钟处于中间一段采样误码率较低的区域(<10E-12)即可正确采集到数据,如图3所示。为了保证采到的数据的正确性,时钟的位置应与误码率较高的区域间留有一定的边界。如果能保证时钟位置离高误码率的区域有一段距离,则不使用辅助的边沿判断时钟也可保证数据的正确性[8]。

在数据采样的过程中,如果采样时钟靠近数据边沿误码率较高的区域时,第一级采样电路输出的信号质量会变差,但第二级SR锁存器依然可以将这个信号恢复成正确的数据。于是,通过检测第一级输出信号的质量,就可以知道采样时钟与输入的数据边沿是否距离过近。对标记位前后数据的分析和统计由鉴相算法模块进行处理并最终控制时钟延迟链调整时钟位置。信号质量检测模块和鉴相算法的具体实现在下两节中详细叙述。

图3 采样位置

2 信号质量检测模块

传统的边沿检测鉴相器使用正交的边沿时钟和采样时钟对数据进行采样,其结构见图4。

图4 边沿检测鉴相器

边沿检测鉴相器采用一对正交时钟对输入数据进行采样,其中边沿时钟的采样结果用于判定边沿位置,采样时钟得到的结果作为正确的数据输出给内部的数字电路。其鉴相方法如下:如果边沿时钟和采样时钟采到的结果相同,则应当将时钟相对数据提前,否则就将时钟推后。经过调整的边沿时钟位置很靠近数据跳变边沿,采样时钟处于数据中间,此时数据采样时钟得到数据的误码率较低。相对于原始的没有时钟数据对齐的结构,这种时钟数据对齐的方法增加了一倍的采样器,功耗及面积同样增加一倍。而且,其时钟位置一直在不断地调整,带来一定的时钟抖动噪声,可能对数据的误码率产生一定的影响。

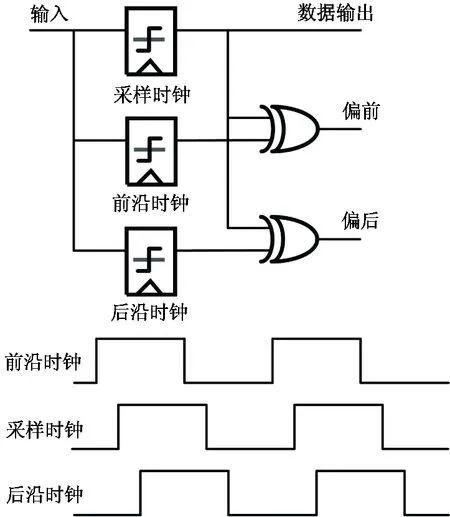

为减小边沿检测方法带来的时钟抖动,有人提出了数据沿跟随的方法。此方法在数据采样时钟前后各有一个边沿采样时钟,其结构见图5。数据沿跟随鉴相方法如下:三个采样结果相同时,时钟位置保持不变,否则,时钟应远离采样错误的那一侧。这种方法增加了两倍的采样器及其功耗和面积。但此种方法得到的时钟噪声较小,因此而产生的误码也较少。

图5 数据沿跟随鉴相器

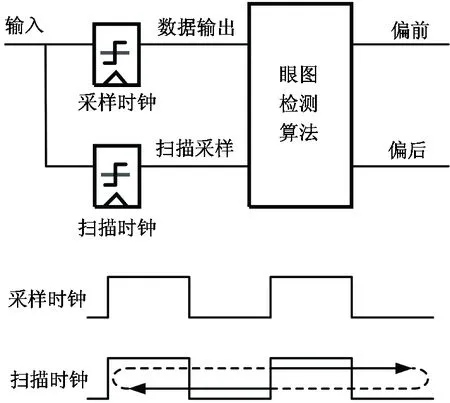

另一种减少时钟抖动的方法是片上眼图检测法,其结构见图6。在此结构中,有一个独立的扫描时钟来回扫描,统计不同位置的误码率,然后依照误码率的大小选择最佳的采样位置,将采样时钟置于此处。统计误码率需要在每个位置采样多次,所以这种方案的跟随带宽极低,基本只能跟随工艺和温度等很慢地变化。另外,此方法使用的扫描时钟需要不断移动位置,这还额外需要一个独立的延迟链。

图6 片上眼图检测

本时钟数据对齐方法仅增加了一小块信号质量检测模块以及低速的数字滤波算法。其中用于鉴相的信号质量检测模块可与现代高速接口中普遍采用的判决反馈均衡器相结合,共用时钟树及部分逻辑,具体实现见图7。

图7 用于鉴相的信号质量检测模块

输入采样电路一般采用SA锁存器,在此之后,使用SR锁存器将采集到的信号恢复成全周期数字信号。SR锁存器比一般的静态锁存器有更强的信号恢复能力。而且,在输入信号幅度较小时,采样SA锁存器的输出延时较长,此时SR锁存器能够正确恢复数据然而动态锁存器会因建立时间不足而出错。因此,在数据信号质量较差时,SR锁存器能得到正确的数据而普通的动态锁存器无法恢复出正确的数据。通过比较两者输出的数据可以判断并标记出信号质量较差的位。电路工作时各主要节点的波形见图8。

在图8中可见,在输入信号幅度较小时,SA锁存器输出信号质量较差,因此动态锁存器无法正确恢复数据,其结果与SR锁存器得到的结果不一致,于是标记此位数据,表示此数据输入幅度过小。

信号质量检测模块一共含有两个动态锁存器和一个异或门,比传统的鉴相模块减少了边沿时钟及其采样器。在接收端中,时钟和前端采样器消耗了大部分的功耗。本设计简化了前端结构,大幅降低了接收端的功耗。

3 鉴相算法

数字鉴相模块根据信号质量检测模块做的标记以及标记前后的数据来猜测时钟和数据的位置关系。时钟和数据的关系如图9所示,若时钟位于中间绿色区域,则采样得到的信号质量较好,数据不会被标记;若时钟处于两侧(P1或P2位置),则采样得到的信号质量较差,信号质量检测模块会对其进行标记。被标记的数据表示采样时钟已经不在中间的低误码率区域了,要对时钟位置进行调整,使其回到数据中间的位置。

图9 时钟采样区域

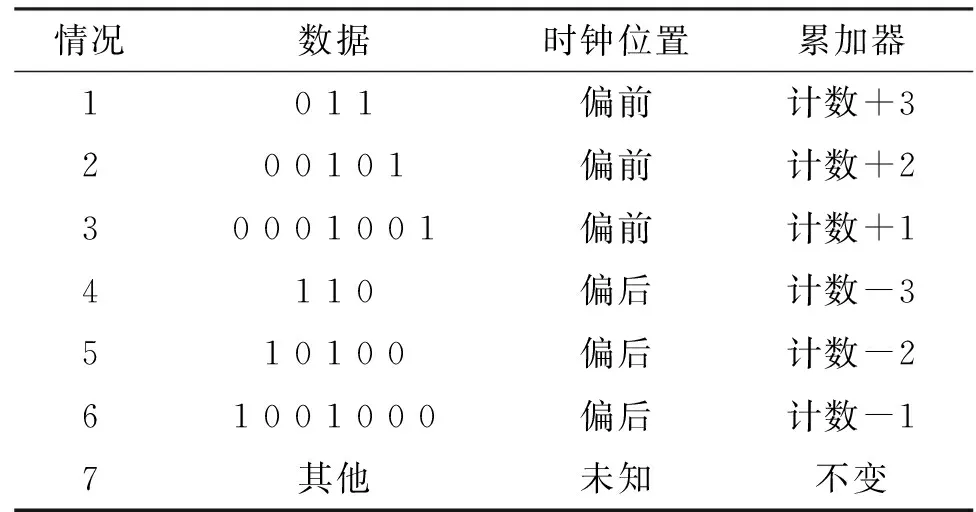

时钟的位置根据被标记数据周围的数据来猜测,猜测结果加入概率累加计数器中。假设被标记的数据为‘1’,则总共有6种不同的情况会改变计数器的值,其余情况不改变。下面对各种情况进行说明,对计数器的改变值总结在表1中。

表1 鉴相计数规则

情况1:信号质量较差的数据为‘1’,其前后的数据值为‘0’和‘1’。采样时钟过于靠近数据跳变的边沿,而在其采样点附近只有一个边沿,因此可以确信时钟采样点比数据眼图中心位置偏前,应将时钟向后调整,累加计数器的值加3。

情况2:信号质量较差的数据‘1’前后的数据值为“00”和“01”。采样时钟过于靠近数据跳变的边沿,但被标记的数据前后均有边沿,需要确认时钟靠近哪个边沿。在这个情况下,被标记的数据前两位均与其不同,而其后只有一位数据与其不同。所以,其之前的跳变边沿会受到前两位数据造成的码间串扰的不良影响;而其之后的跳变边沿仅会受到其后一位数据的码间串扰的影响。前方的数据沿会比后面的数据沿更靠近数据的中心。在图5的P1位置采到的信号会比P2位置信号质量更差。因此,时钟靠近数据前沿的概率更大,时钟应向后调整的概率更大,累加计数器的值加2。

情况3:信号质量较差的数据‘1’前后的数据值为“000”和“001”。这与情况2近似,但前后两个跳变沿受码间串扰影响的差别更小,因此前后沿概率的差不如情况2大。在此情况下,累加器只加1。

表1中的情况4到情况6是前三种情况的镜像,时钟在这些情况下更靠近数据后面,应将时钟位置向前调整。累加器在这些情况下会减去相应的数值。当被标记的信号质量较差的数据为‘0’时,同样有6种判定情况,与之前叙述的数据‘1’的判断逻辑相似,这里不再列出。

表1中只有情况1和情况4是确定的结论,其余的情况都是对时钟位置的猜测。因此,需要使用统计的方法对齐进行处理。具体的实现是,使用概率计数器来统计一段时间内判断值的累加,之后依据累加值对时钟进行调整,每128个数判定一次。若累加器的数大于7,则改变数字延迟链的值,使时钟延迟增加一点;若小于-7,则改变数字延迟链的值,使时钟延迟减小一点;若累加器的数值处于-7和7之间,则认为这些偏差是由噪声引起的,因此不对时钟延迟做任何调整。这样,数字鉴相逻辑输出给时钟延迟链的情况共有3种:(1)增加延迟;(2)减小延迟;(3)不变。这相对于通常只有“增加”、“减小”两种输出的鉴相器来讲,时钟的抖动会更小,因此可以降低时钟噪声,降低误码率。

在时钟已锁定(时钟处于数据中间的低误码率区域)的情况下,偶尔会有较大的码间串扰造成数据信号质量变差,但这个码间串扰会等概率地影响采样点之前的数据沿和之后的数据沿。因此,由大的码间串扰造成的累加器数值的变化过程可认为是一个一维的随机游走。仿真表明,在锁定情况下,每128位中仅会出现两三位信号质量较差的数据,因此选用7作为阈值以避免时钟因此出现抖动。

时钟恢复逻辑需要较长时间的累加才能得到一个确定的结果。因此,本设计的时钟数据跟随带宽较低,理论最大值约为1MHz左右。这足以跟随低频噪声和温度变化对信道延迟造成的变化。

4 芯片实际测试结果

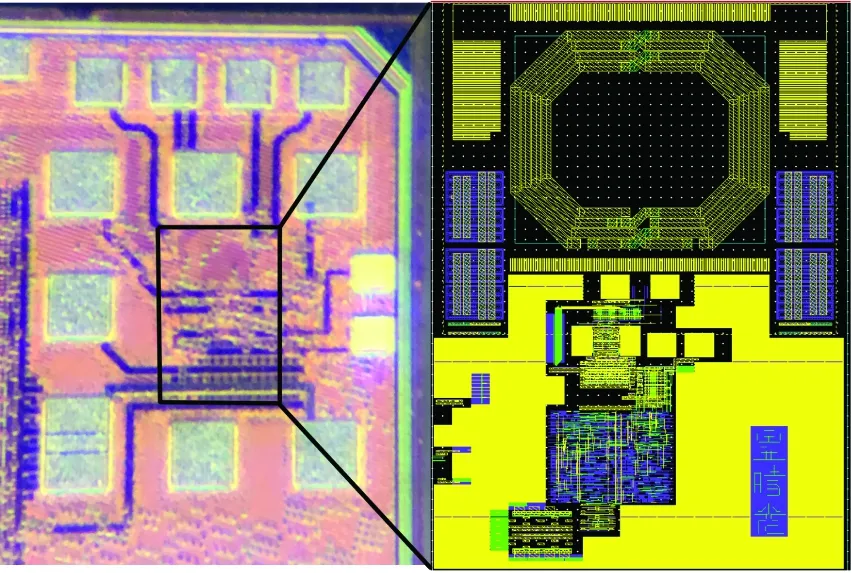

含有本时钟数据恢复电路的接收/发送芯片采用40nmCMOS工艺设计制造。实际芯片照片及设计版图见图10。时钟恢复部分的电路占用芯片面积60μm×70μm,包括信号质量检测模块、时钟恢复逻辑以及数字延迟链。

带有本时钟数据恢复电路的接收端已经经过实际流片检验,在实际芯片测试中,接收到的数据速率最高为13Gb/s。在此速率下,电源电压为1.1V,总功耗10.8mW,其中,数字时钟恢复电路功耗2mW,

图10 芯片显微镜照片

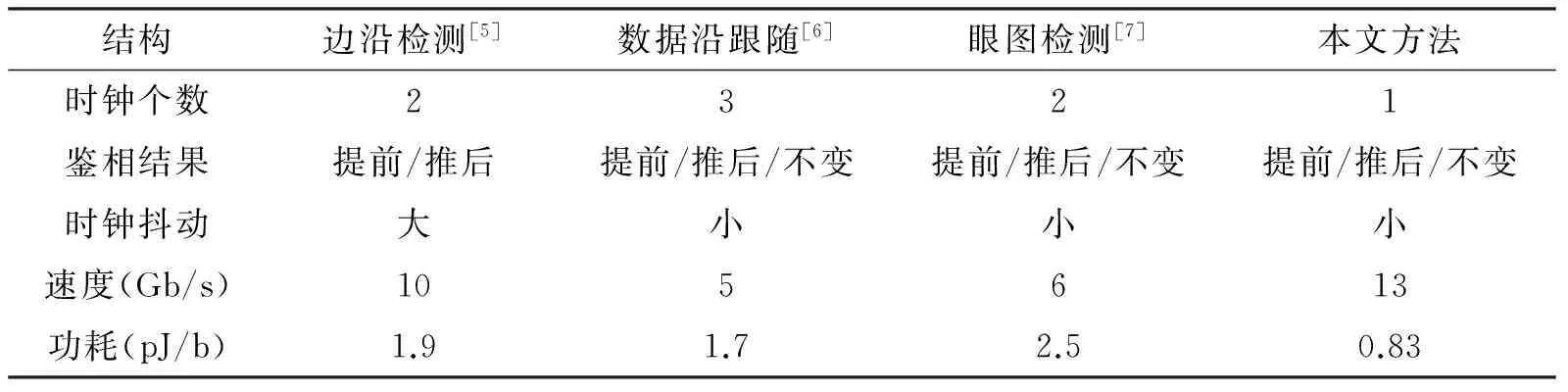

前端处理电路3.8mW,串并转换模块1.5mW,时钟接收及时钟树总计3.5mW。该速率下的功耗效率为0.83pJ/bit,已达到国际先进水平。本接收端性能与其他速率相近的接收端的比较见表2。

表2 时钟数据恢复结构比较

芯片测试环境如图11所示。误码仪发送半速时钟和全速数据到芯片输入端,接收端电路对数据和时钟进行对齐并采样数据,然后将采样后的半速数据,即两路6.5Gb/s的数据流,输出回误码仪。误码仪对比输出和输入的数据,得到误码率。

图11 芯片测试平台

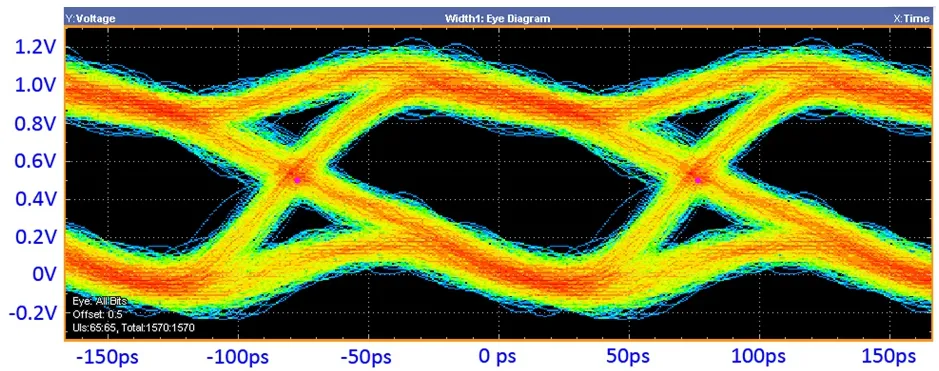

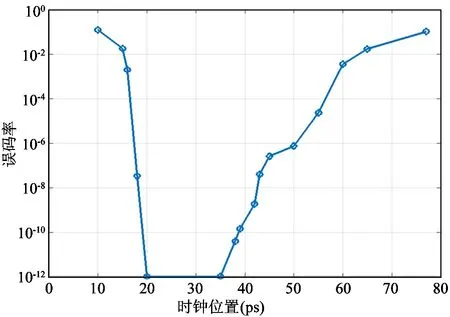

图12展示了输出数据的眼图。实际芯片测试结果显示,接收端电路可以达到10E-12以下的误码率。图13展示了接收端的误码率浴盆曲线。

图14展示了接收端时钟数据相位噪声的容忍能力,曲线表示误码率低于10E-12的情况下,电路接收端能容忍数据上带有的最大抖动。实测数据显示,时钟数据恢复(CDR)电路的跟随带宽约为200kHz,在低频下展现出很好的跟随和噪声消除能力。

图12 输出6.5Gb/s数据眼图

图13 误码率浴盆曲线

图14 相位噪声容忍度

5 结 论

随着处理器接口总线的发展,高速串行总线接口的系统更加复杂,因为对性能、功耗提出了更高的要求,同时需要加入时钟数据恢复等新功能。本文研究了高速串行接口的低功耗时钟数据恢复电路,在原有高速采样接口中,加入了少量高速逻辑和一部分可综合的低速逻辑,使用较少的面积和功耗完成了时钟数据对齐的功能。本设计优化了整体接收端的结构,相对于传统结构,大幅减少了接收端的功耗。而且,本结构经过实际芯片测试检验,其工作速率已能满足现有所有商用CPU对外高速接口的速率要求。

[1] Doi Y, Shibasaki T, Danjo T, et al. A 32 Gb/s data-interpolator receiver with two-tap DFE fabricated with 28-nm CMOS process.IEEEJournalofSolid-StateCircuits, 2013, 48(12):3258-3267

[2] Kalisch B, Giese A, Litz H, et al. HyperTransport 3 core: a next generation host interface with extremely high bandwidth. In: Proceedings of the 1st International Workshop on HyperTransport Research and Applications, Mannheim, Germany, 2009.11-19

[3] 王齐. PCIExpress体系结构导读. 北京: 机械工业出版社, 2010

[4] Ziakas D, Baum A, Maddox R A, et al. Intel® QuickPath interconnect architectural features supporting scalable system architectures. In: Proceedings of the IEEE Annual Symposium on High Performance Interconnects, California, USA, 2010. 1-6

[5] Balamurugan G, Kennedy J, Banerjee G, et al. A scalable 5-15 Gbps, 14-75 mW low-power I/O transceiver in 65nm CMOS.IEEEJournalofSolid-StateCircuits, 2008, 43(4):1010-1019

[6] Park M J, Kim H, Son S, et al. A 5-Gbps 1.7 pJ/bit ditherless CDR with optimal phase interval detection. In: Proceedings of the IEEE Custom Integrated Circuits Conference, California, USA, 2012. 1-4

[7] Loh M, Emami-Neyestanak A. A 3×9 Gb/s shared, all-digital CDR for high-speed, high-density I/O.IEEEJournalofSolid-StateCircuits, 2012, 47(3):641-651

[8] Fukuda K, Yamashita H, Ono G, et al. A 12.3-mW 12.5-Gb/s complete transceiver in 65nm CMOS process.IEEEJournalofSolid-StateCircuits, 2010, 45(12):2838-2849

A low power architecture of high-speed clock and data recovery circuit

Meng Shiguang******, Yang Zongren***

(*State Key Laboratory of Computer Architecture(Institute of Computing Technology, Chinese Academy of Sciences), Beijing 100190) (**Institute of Computing Technology, Chinese Academy of Sciences, Beijing 100190) (***University of Chinese Academy of Sciences, Beijing 100049)

To reduce the power consumption of the clock and data recovery (CDR) circuit of a high speed serial interface, a novel phase detecting CDR was presented and it was implemented based on the study of existing CDR algorithms. The new design only used one sampling clock under high speed, so the sample rate can be reduced to half of the traditional phase detecting architecture and the power consumption of the front sampler can be reduced. The proposed phase detecting algorithm employed a statistic method to diminish the clock jitter during phase detecting period to reach lower bit error rate (BER). The phase detecting algorithm can be implemented using digital synthesis method and it works at lower frequency so it can be easily port to other technologies. The whole circuits was manufactured using 40nm CMOS technology, and the chip test results demonstrated that the designed architecture worked at 13Gb/s with the BER less than 10E-12 and the power efficiency was 0.83pJ/bit.

low power receiver, high-speed serial interface, clock and data recovery (CDR)

10.3772/j.issn.1002-0470.2016.06.004

①国家“核高基”科技重大专项课题(2009ZX01028-002-003, 2009ZX01029-001-003, 2010ZX01036-001-002, 2012ZX01029-001-002-002, 2014ZX01020201, 2014ZX01030101),国家自然科学基金(61521092, 61133004, 61173001, 61232009, 61222204, 61432016)和863计划(2013AA014301)资助项目。

2016-01-25)

②男,1989年生,博士生;研究方向:计算机系统结构;联系人,E-mail: mengshiguang@ict.ac.cn