HEVC 中CABAC 解码器的硬件设计与实现

2016-12-05袁星范蔡敏

袁星范,蔡敏

(华南理工大学 电子与信息学院,广东 广州510640)

HEVC 中CABAC 解码器的硬件设计与实现

袁星范,蔡敏

(华南理工大学 电子与信息学院,广东 广州510640)

基于上下文自适应二进制算术编码(CABAC)是HEVC中采用的一种高效熵编码,具有很高的压缩比,但实现结构复杂,且很难并行化。本文设计了一个高性能的CABAC解码器,并对单周期解码1bit的硬件结构进行了优化,同时采用流水线结构,进一步提高了解码性能。采用0.18 μm CMOS工艺,综合后面积为48K个逻辑门,工作频率为250 MHz,解码速度达到1 bit/cycle,适用于高清视频领域。

CABAC;HEVC;二进制算术编码;硬件设计

随着高清视频应用日益增加,对视频压缩性能提出了更高的要求。因此,2010年4月国际电信联盟电信标准化部门(IUT-T)的视频编码专家组(VCEG)和国际标准化组织(ISO)的动态图像专家组(MPEG)组建视频编码联合组(JCT-VC),联手制定了新一代视频编码标准HEVC。HEVC采用CABAC的熵编码方式,获得了高的压缩效率,但实现结构复杂,诸多的迭代运算,加上各级之间的相关特性使其很难并行化[1-3],在硬件实现上占用较多的面积并且速度较慢。

文中设计了一个高性能的CABAC解码器,通过对单周期解码1bit的结构进行改进,优化了面积和关键路径等特性,提高了解码性能。该设计采用Verilog HDL进行建模和仿真,并利用Synopsys公司的相关工具进行了面积和时序分析。

1 CABAC解码流程

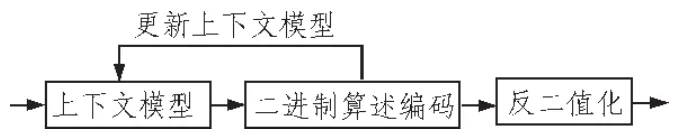

HEVC中,CABAC的解码流程如图1所示。主要由三部分组成:上下文模型,二进制算术编码和反二值化。

图1 CABAC解码框图

1.1上下文模型

语法元素使用的上下文概率模型都被唯一的概率模型索引号ctxIdx标识,每一个ctxIdx与两个概率模型变量有关:最大概率符号MPS和概率状态索引pstate。MPS表示待解码bit最可能出现的符号,取值为0或1;反之,LPS表示待解码bit最不可能出现的符号。CABAC中为LPS设定了64个值,pstate与LPS概率值一一对应,在获得初始概率模型变量后,就可以对符号进行二进制算术编码和概率模型参数的自适应更新。当MPS出现时,当前概率模型的pstate变大;当LPS出现时,当前概率模型的pstate变小;当概率模型的pstate为0时,表明MPS和LPS概率相同,若再出现LPS,则MPS和LPS必须交换[4]。

1.2二进制算术编码

二进制算术解码根据给定的概率模型对区间进行递归的划分,由两个变量进行描述:范围Range(R)和偏移量Offset (O)。Range表示当前解码区间的长度,Offset表示当前从码流中读取的bit串表示的实数在解码区间中的相对位置。每解码一个bit,R和O都要进行更新,同时,根据当前解码出来的值更新上下文模型。经过区间划分后R变得小于256时,就需要进行重新归一化过程[5-7]。此外,还有两种特殊情况下的解码方式:旁路解码和终止解码。

1.3反二值化

在HEVC中,常用的二值化方法有截断莱斯二元化(TR),K阶指数哥伦布二元化(EGK),定长二元化(FL)和查表法。反二值化是将二进制算术解码得到的二元串(bin_string),采用相应的二值化方法得到当前所解语法元素的值,其中每一个这种反二值化后的符号称之为bin。

2 CABAC的硬件设计

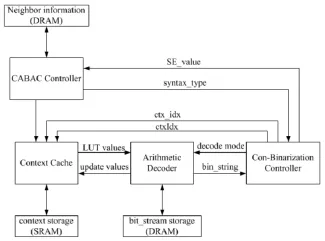

文中CABAC解码器硬件设计的总图框图如图2所示,主要由四大模块构成,分别是CABAC Controller模块、Con-Binarization Controller模块、Context Cache模块和 Arithmetic Decoder模块。

图2 CABAC硬件设计整体框图

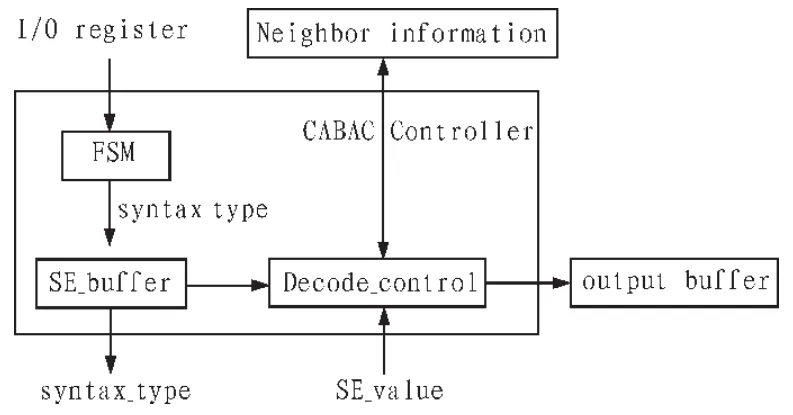

2.1CABAC Controller模块

该模块利用当前相邻的宏块信息 (Neighbor information)和已解码的语法元素值(SE_value),确定下一个需要进行解码的语法元素类型(syntax_type)。主要由状态机(FSM),语法元素缓存器(SE_buffer)和解码控制器(Decode_control)三部分组成,如图3所示。其中FSM是CABAC的核心控制部分,控制整个解码流程,该模块主要输出结果是需要进行解码的syntax_type;SE_buffer用来存储 FSM输出的 syntax_type和Context.

Cache模块的控制信号;Decode_control用来控制输出,把解码后的信息传递给视频解码器中CABAC的下一环节。

图3 CABAC Controller结构图

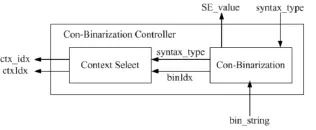

2.2Con-Binarization Controller模块

Con-Binarization Controller模块包含反二值化(Con-Binarization)和上下文模型选择(Context Select)两部分,如图4所示。Context Select模块利用输入的syntax_type和bin_string的索引号(binIdx)确定其概率模型索引号ctxIdx,另外一个重要的输出信号ctx_idx用来确定所选概率模型的存储地址;Con-Binarization模块除了选择相应的二值化方法进行反二值化外,还包括对bin_string进行串匹配以决定是否完成一个语法元素的解码,若匹配成功则输出一个语法元素,并根据码流语法规定进行ctxIdx的更新,用来选择下一个bin的概率模型。

图4 Con-Binarization Controller结构图

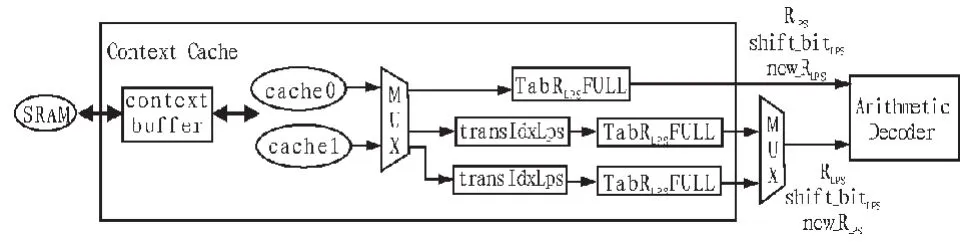

2.3Context Cache模块

在CABAC的解码过程中,每解码完一比特,就会对它所用的上下文模型(context)进行更新,以实现 对视频流实时统计特性的跟踪。Context Cache模块的组成如图5所示。为了减少数据在SRAM、上下文缓存器(context buffer)和乒乓缓存器(cache0,cache1)之间的交换频率,context buffer必须要存储所有的context,乒乓缓存器根据ctx_idx从context buffer中读取 context和存储更新的 context。在解码时,cache0和cache1只有一个处于工作模式用来解码当前的语法元素,另外一个用来读取下一个语法元素的context。乒乓缓存器后的选择器(MUX)用来确定cache0和cache1哪一个处于工作模式,利用transIdxLps,transIdxMps和TabRLPSFULL3个查找表来进行概率模型索引和概率值得更新,最终得到3个变量RLPS,shift_bitLPS,new_RLPS的值作为Arithmetic Decoder模块的输入参数。

图5 Context Cache结构图

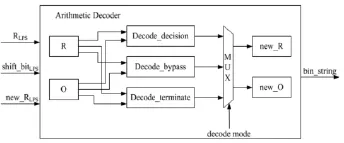

2.4Arithmetic Decoder模块

本模块是CABAC的主要模块,用来实现自适应的二进制算术编码,输出的是解码出来的 bin_string。主要包括Decode_decision、Decode_bypass和 Decode_terminate 3个模块,其内部结构如图6所示。对本模块的硬件优化主要是针对Decode_decision模块,是Arithmetic Decoder模块的核心部分。由于传统CABAC解码结构各级之间的强相关性[8-11],使得区间划分,bin裁决,重归一化只能串行工作,严重影响了解码速率。下面详述本设计中采用的4种优化方案,如图7所示。

图6 Arithmetic Decoder结构图

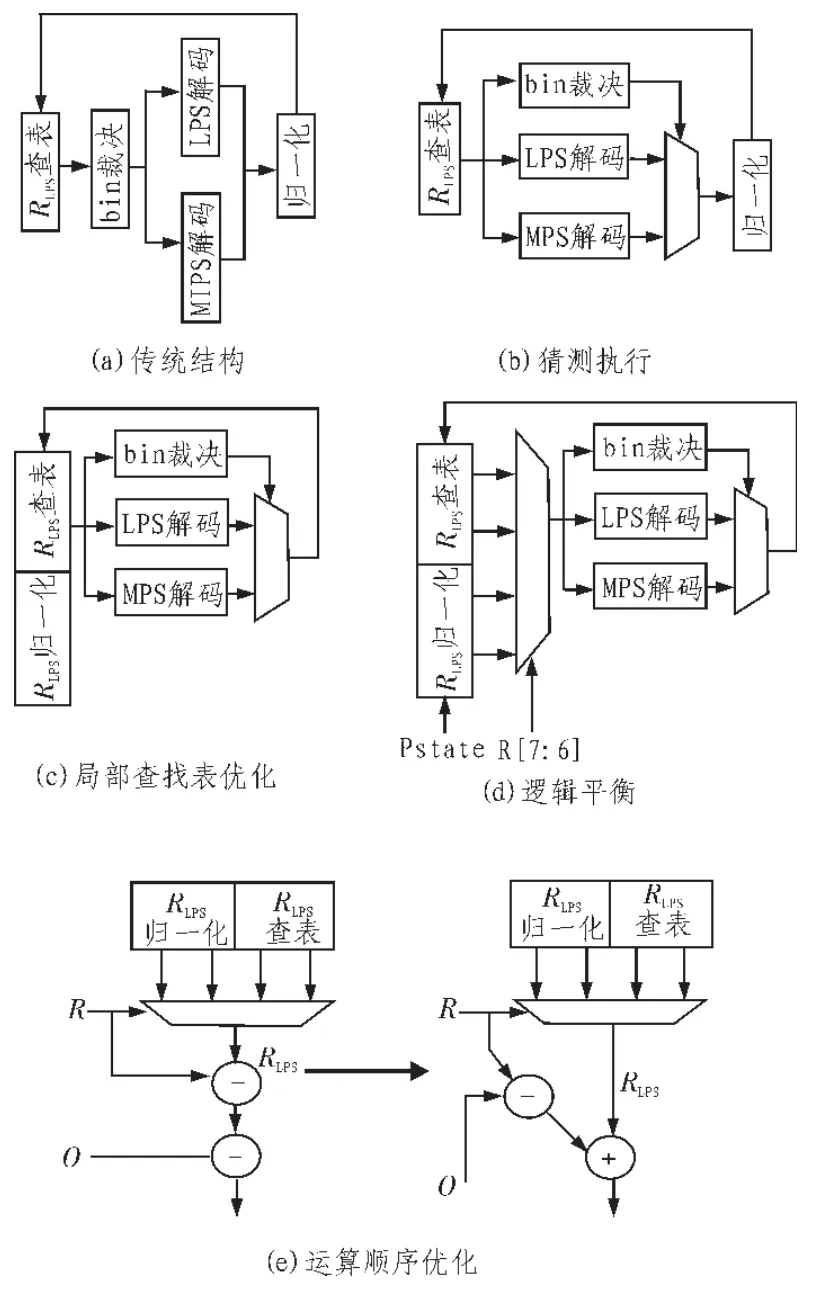

图7 Decode_decision模块的优化

1)猜测执行

猜测执行是把所有可能的输入值对应的结构都计算出来,在前级计算的同时后级按所有可能的输入并行的进行后级计算,再以前级计算结束的结果选择后级计算结果中正确的那个,实现前后两级的并行化。在此设计中,把bin裁决的结果作为最佳猜测对象,由于裁决结果位宽只占一个比特,且处于CABAC解码器的关键路径中,驱动电路只需复制两份,即MPS和LPS同时独立的进行解码,最后根据真实的bin裁决结果进行选通。

2)局部查找表优化

局部查找表优化是指将LPS解码部分的归一化运算并入到查找表TabRLPS中,其实质是当面积在可以接受的范围内,以面积来换速度。

3)逻辑平衡

LPS对应的区间长度RLPS是由查找表TabRLPS得到的,索引值为R的次高两位(R[7:6])和pstate,由于R[7:6]处于bin解码的关键路径中,而pstate不是,所以先查索引值pstate,再通过R[7:6]进行结果选择,来缓解R端输入时序比较紧张的局面[12-14]。

4)运算顺序优化

采用如下公式来交换两个减法的运算顺序使得bin裁决的输出对各输入端达到均衡。其中OLPS表示bin裁决结果为LPS时,更新的O值。

2.5流水线设计

CABAC解码器采用三级流水线结构,第一级流水线FSM控制哪个语法元素要进行解码和产生相应的上下文模型索引;第二级流水线从SE_buffer中获取语法元素,从Context Cache中取出context并锁存起来;第三级流水线进行当前比特的算术解码,解码后的bin_string进行反二值化得到相应语法元素的值。采用流水线设计,使解码时语法元素的延时减少了。提高了解码速度,同时,对硬件实现的时序也有利。

3 CABAC解码器的硬件实现

根据上文CABAC解码器的硬件结构,采用Verilog HDL进行建模,并使用NC_verilog进行了验证,采用Synopsys公司的Design Compiler进行综合,综合面积为48K个逻辑门;Prime Time进行静态时序分析,没有时序违规;工作频率为250 MHz,解码速度达到1 bit/cycle,满足高清视频需求。

4 结束语

文中通过对面积、关键路径等优化,设计了一个高性能的CABAC解码器硬件结构,并采用流水线设计,显著提高了CABAC的解码速度,充分利用了存储空间,在高清视频解码器中具有很大的应用价值[15]。

[1]陈杰,丁丹丹,虞露.高清CABAC解码器的优化设计与实现[J].计算机工程,2012,38(23):273-276.

[2]Chen Jianwen,Chang Chengru,Lin Youlong.A hardware accelerator for context-based adaptive binary arithmetic Decoding in H.264/AVC[J].IEEE Transactions on Circuits and Systems for Video Technology,2005,15(5):4525-4528.

[3]盛怀亮,林涛.全高清CABAC视频解码器的设计与实现[J].计算机工程,2008,34(19):236-228.

[4]万帅,杨付正.新一代高效视频编码H.265/HEVC:原理、标准与实现[M].北京:电子工业出版社,2014.

[5]VIVIENNE S,MADHUKAR B.High throughput CABAC entropy coding in HEVC[J].IEEE TCSVT,2012,22(12):1778-1791.

[6]TSAI C H,TANG C S,CHEN L G.A flexible fully hardware CABAC encoder for UHDTV H.264/avc high profile video[J]. IEEE Trans Consumer Electronics,2012,58(4):1329-1337.

[7]Marpe D,Wiegand T.H.264/MPEG4-AVC Fidelity Range Extensions:Tools,Profile,Performance,and Application Areas[C]// Proc.of IEEE International Conference on Image Processing. San Diego,USA:IEEE Press,2005.

[8]Yu W,He Y.A high performance CABAC decoding architecture[J].IEEE Trans.Consum.Electron.,2005,51(4):1352-1359.

[9]Zhang P.Fast CABAC decoding architecture[J].Electronics Letters,2008,44(24):1394-1395.

[10]胡海明,李金良.基于上下文的自适应二阶二进制算术编码算法[J].计算机工程与设计,2006,27(17):3267-3269.

[11]Zhang P.Fast CABAC decoding architecture[J].Electronics Letters,2008,44(24):1394-1395.

[12]朱敏,刘雷波,王星,等.一种CABAC解码引擎的芯片实现[J].电路与系统学报,2013,18(2):6-11.

[13]张秀丽,万忠,鲍程红.基于码头分组的CAVLC解码算法优化[J].电路与系统学报,2009,14(3):126-130.

[14]Yi Y,Park I C.High-speed H.264/AVC CABAC decoding [J].IEEE Trans.Circuits Syst.Video Technol.,2007,17(4): 490-494.

[15]陈潜,杨秀芝.高清H.264 CABAC解码器的优化设计[J].有限电视技术,2014(9):46-49.

Hardware design and implementation of CABAC decoder in HEVC

YUAN Xing-fan,CAI Min

(School of Electronics and Information,South China University of Technology,Guangzhou 510640,China)

context based adaptive binary arithmetic encoding(CABAC)is a kind of high efficient entropy encoding used in HEVC,which has a high compression ratio,but it is complex and difficult to be parallel.In this paper,a high performance CABAC decoder is designed,and the hardware structure of the single cycle decoding 1bit is optimized,and the pipeline structure is used to improve the decoding performance.With the 0.18 μm CMOS process,the integrated area is 97K logic gates,the working frequency is 250MHz,the decoding speed reaches 1bit/cycle,which is suitable for the field of HD video.

CABAC;HEVC;binary arithmetic encoding;hardware design

TN4

A

1674-6236(2016)21-0057-03

2015-11-18稿件编号:201511174

袁星范(1991—),男,湖南益阳人,硕士研究生。研究方向:数字芯片设计。