彩色视频增强算法关键技术FPGA实现

2016-12-03杨学博陈光拓

杨学博,李 磊,陈光拓

(1.电子科技大学 电子科学技术研究院,四川 成都 611730;2.成都信息工程大学 电子工程学院,四川 成都 610000)

彩色视频增强算法关键技术FPGA实现

杨学博1,李 磊1,陈光拓2

(1.电子科技大学 电子科学技术研究院,四川 成都 611730;2.成都信息工程大学 电子工程学院,四川 成都 610000)

随着视频设备的高速发展,数字视频相关应用同样发展迅速,如监控设备、行车记录仪以及手机等电子产品。而如今数字视频图像增强的算法层出不穷,由于算法的复杂程度比较高,很难满足实时性这一基本的要求。讨论了基于 Retinex模型的处理图像像素以及拉伸尺度可配置的关键技术,对关键模块进行实践以及仿真,最后将其通过FPGA实现(Vertex-5),系统时钟125 MHz,可以满足30 f/s的(2 000×2 048)像素的图像。

retinex;视频增强;FPGA;实时处理

0 引言

视频增强技术应用范围广泛,例如医疗电子、工业控制、消费电子以及深空探测。Retinex理论是由Edwin Land在1971年提出。基于Retinex模型的使用较为广泛的有单尺度Retinex算法(Single Scale Retinex,SSR)、多尺度Retinex算法(Multi Scale Retinex,MSR)、带有颜色校正的多尺度Retinex算法(Multi Scale Retinex with Color Restoration,MSRCR),基于先验模型的算法如基于辩分框架的Retinex算法,但是这种算法的复杂度过高会消耗过多硬件资源,还不能在实际中得到很好的应用。而单尺度或多尺度 Retinex算法对图像增强效果同样显著,多尺度Retinex算法的主要硬件结构就是单尺度Retinex算法硬件电路的重构。本文旨在视频增强算法硬件关键技术的研究,所以采取单尺度 Retinex算法,然而对于这样的算法用CPU也不能满足其视频处理过程中实时性的要求,本文采用 125 MHz频率FPGA,可以满足 30 f/s的 (2 000×2 048)像素的图像。

本文主要讨论了基于 Retinex的关键算法,基于图像像素可配置以及拉伸尺度可配置。提出针对可适应不同像素视频的硬件架构。实现对关键模块的设计和仿真,通过 Vertex-5型号 FPGA实现整个设计,最后评估算法的处理效果。

1 基于Retinex模型的视频增强算法

图1为视频增强 Retinex算法流程图。视频中的帧图像通过RGB将HSV转化成灰度帧图像V,色度帧图像S,饱和度帧图像H。估计照度帧图像,适当拉伸处理后得到光照分量V2以及反分量像V3。经过拉伸处理以及合成处理后的图像O即为处理完成的一帧图像。

1.1 RGB转HSV

由于RGB色彩空间图像直接处理会产生色彩失真,因此需要转换色彩空间。

图1 Retinex算法流程图

1.2 提取光照图像和反色图像

原帧图像 I(x,y)能够被分解成两部分[2]。一部分是光照帧图像 L(x,y),另一部分为反射帧图像 R(x,y),如式(1)所示。

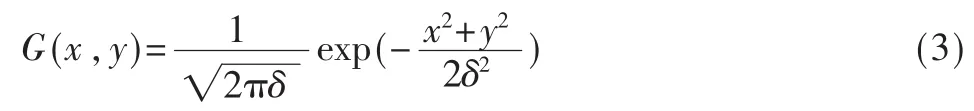

本文采用高斯滤波器进行光照估计,将高频成分(图像的细节部分和噪声部分)滤掉。

提取反射帧图像R(x,y),反射帧图像是图像的高频成分(图像的细节部分和噪声部分)。

由Retinex结构式(4)得到式(5)。为了防止式(5)分母为0,δ取值0.001。

1.3 反射帧分量处理方法及光照分量的处理

反射分量可以通过sigmoid函数进行非线性拉伸。以此可以很好地抑制噪声同时放大有用的细节成分。

本文使用参数u=3,β=0.6。

光照分量通过L′=[L]r函数拉伸。

1.4 HSV图像到RGB图像转换

RGB色彩空间是一种由红绿蓝三种色彩组成,用于显示器显示,所以将HSV图像转换为RGB图像。

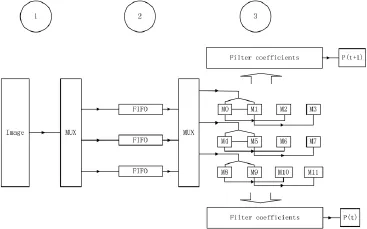

2 视频增强硬件逻辑架构

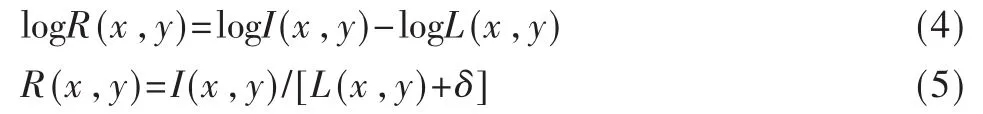

自适应视频增强VLSI架构如图2所示,图2中框内为FPGA实现部分,框外的部分由MATLAB实现转换。本系统由decoder模块对内部配置寄存器进行配置,主要任务是配置处理图像像素。SRAM_interface是SRAM连接外部图像数据流的缓冲,SRAM内部分配两个存储空间用来对视频数据乒乓操作。滤波器采用的是改进型的二维滤波器。本滤波器可以适应不同像素图片滤波较高的处理速度。由滤波器估计光照图像同时由于对数运算和减法的复杂程度相对较高,并且使得亮度较高像素失真,本文采用较高精度除法器得到反射图像。同时通过两个拉伸函数处理经过乘法器得到增强后的图像,经由HVSRGB还原成RGB图像。

图2 自适应视频增强VLSI架构

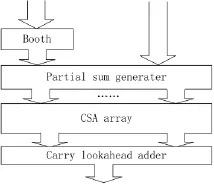

2.1 改进后的滤波器模块

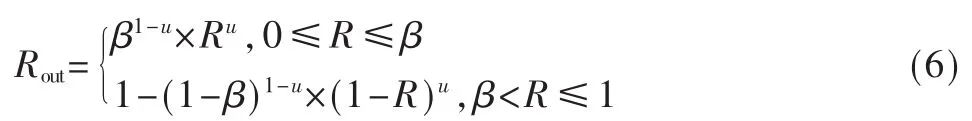

本文基于文献[3][4]提出了一个可配置处理像素大小和具有较好的时序特征的二维滤波器。架构如图3所示。本文的滤波器分为3部分,第一部分的作用是将两个8位的数据合并成一个16位的数据,并依次写入不同FIFO。第二部分是可配置的 FIFO,通过配置内部寄存器来配置 FIFO的深度,给不同行的滤波器窗写数据。第三部分为滤波器窗口,将16位数据转换成8位写到滤波器窗两个像素点,下一个周期将这两个像素点移位到后面两个像素点。通过滤波系数每个周期得到新的处理后的像素点。这种结构不仅节约资源,而且可以配置处理视频图像像素点多少,处理过程中的时钟频率是一半的系统时钟频率,更好地满足时序要求。

图3 滤波器硬件架构

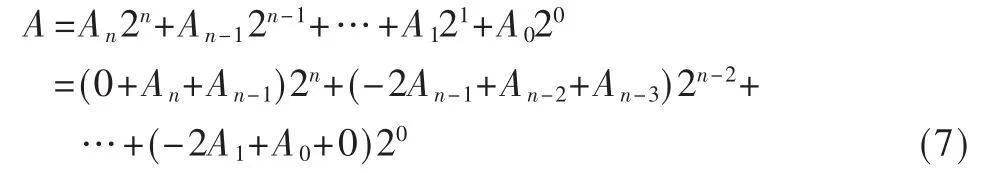

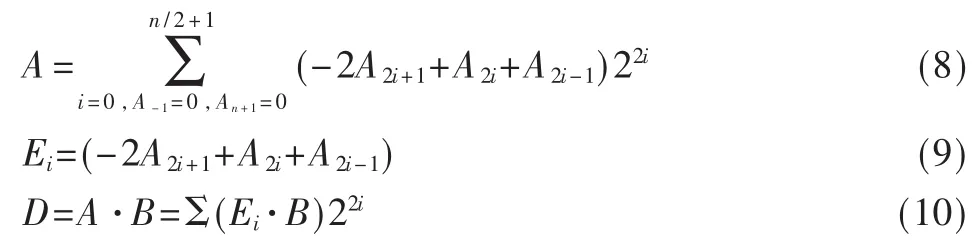

2.2 高速乘法器

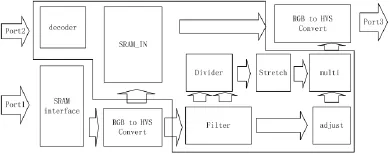

本设计中用到了一些乘法器[5-7],由于时序原因本文采用高速乘法器,图4为乘法器硬件架构图,乘法器包括基-4的 booth算法,由 CSA组成的Wallace树和超前进位加法器。

图4 高速乘法器硬件架构

部分和产生器是基 4 booth算法,将部分和减少近一半,通过CSA累加单元组成的Wallace树结构,得到两个部分和通过超前进位加法器最后得到乘积。

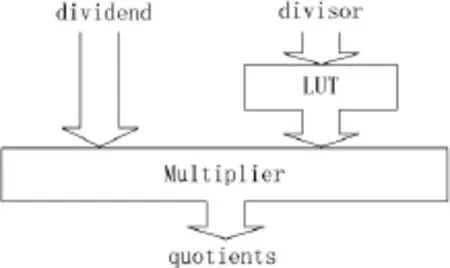

2.3 除法器

本文采用精度较高除法器,减少因为运算产生的误差,高速除法器硬件电路如图5所示,由乘法器和查找表组成,查找表存储除数的倒数。

图5 高速除法器硬件电路

2.4 帧图像拉伸和调整

光照帧图像实现伽马校正,本文采用查找表的方法。

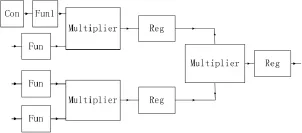

反射图像做拉伸运算,采用图6所示架构来实现,本文是可配置的拉伸,本方法可以实现通过改变Con寄存器改变其拉伸程度。改变其图像处理效果。Fun1和Fun用来实现函数的组合电路。

图6 可配置拉伸尺度图像拉伸模块架构

3 基本模块仿真和实验结果

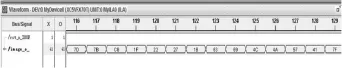

由于VCS仿真能力强于modesim对于各个模块的仿真,本文使用8核16线程48 G的内存滤波器debian linux操作系统,VCS 2013版本的仿真平台,得到结果如图7、图8所示。

图7 滤波器仿真结果

图8 chipscope抓取输出信号

本文采用Vertex_5_FXT(FX70/100T)_FF1136 FPGA芯片搭建的硬件平台实现图中方框内部关键部分,其他部分由AMD 4核4 G内存matlab 2014b实现。图9、图10是对不同图片的处理结果。

图9 汽车

图10 塔

4 算法评估

熵是信息论里面重要概念,表示了信息量的多少,在图像中也反映了图像的内容多少[8-9]。式(11)为熵的表达式。

图像增强前后熵的对比如表1所示。

5 结语

本文主要分析了基于Retinex视频图像增强算法的不同架构,先验的Retinex算法由于算法复杂度较高,本文选择了单尺度 Retinex算法关键技术,经过单尺度算法重构即为多尺度 Retinex算法,基于图像像素可配置以及拉伸尺度可配置提出硬件架构,并对各个模块进行实现和仿真,最后通过FPGA实现,并评估图像处理效果。

表1 图像增强前后熵的对比

[1]Wang Wen,Li Bo,Zeng Jin,et al.A fast multi-scale retinex algorithm for color image enhancement[C].Proceedings of the 2008 International Conference on Wavelet Analysis andPattern Recognition,Hong Kong,2008:30-31.

[2]Fu Xueyang,Sun Ye,LiWang Minghui,et al.A novel retinex based approach for image enhencement with illumination adjustment[C].2014 IEEE International Conference on Acoustic,Speech and Signal Processing,2014:1190-1194.

[3]BAILEY D G.Effcient implementation of greyscale morphological filters[C].International conference on Field Programmalle Technology.2010:421-424.

[4]SEDCOLE P.Reconfigurable platform-based design in FPGAs for video image processing[D].Deparment of Electrical and Electronic Engineering,imperial College,London,UK.2006.

[5]Yao Aihong,Li Ling,Sun Mengzhe.Design of pipeline multiplier based on modified booth′s algorithm and wallace tree[C].Advanced Researon Electronic Commerce,Web Application,and CommunicationInternational Conference,ECWAC 2011 Guangzhou,China,2011,Part I.

[6]Jagadeshwar Rao M,DUBEY S.A high speed and area efficient booth recoded wallace tree multiplier for fast arithmetic circuits[C].2012Asia Pacific Conference on Postgraduate Research in Microelectronics&Electronics,2012.

[7]HENSLEY J,LASTRA A,SINGH M.A scalable counterflowpipelined asynchronous radix-4 booth multiplier[C]. International Symposium on Asynchronous Circuits and Systems,2005:128-137.

[8]Xu Xin,Chen Qiang,Pheng Ann Heng,et al.A fast halofree image enhancement method based on retinex[J].Journal of computer-aided design&computer graphics,2008,20(10). [9]LEVERICK G,WU C,SZTURM T.Coarse quantization in calculations of entropy measures for experimental time series[J].Nonlinear Dynamics,2014,79(1):93-100.

Key technology of color video enhancement algorithm and FPGA implementation

Yang Xuebo1,Li Lei1,Chen Guangtuo2

(1.Electronic Science and Technology Research Institute,University of Electronic Science and Technology of Chengdu,Chengdu 610000,China;2.Institute of Electrical Engineering Chengdu Information Engineering University,Chengdu 610000,China)

With the high speed development of video equipment,digital video related applications also developed fast.Such as monitoring equipment,vehicle traveling data recorder and cellphone.The algorithm of image enhancement is emerge in endlessly. But due to the increasement of the quality and algorithm complexity of the image,video processing is very difficult to meet the basic requirements of real-time.This paper discusses the key technology based on retinex which used in the wide field,and put forward the key modules and implement simulation,then realize the key technology by FGPA implementation,processing rate 125 MHz by using Vertex-5.

Retinex;video enhancement;FPGA;real-time

TP317.4

A

10.16157/j.issn.0258-7998.2016.11.008

杨学博,李磊,陈光拓.彩色视频增强算法关键技术 FPGA实现[J].电子技术应用,2016,42(11):37-39,43.

英文引用格式:Yang Xuebo,Li Lei,Chen Guangtuo,et al.Key technology of color video enhancement algorithm and FPGA implementation[J].Application of Electronic Technique,2016,42(11):37-39,43.

2016-06-26)

杨学博(1988-),通信作者,男,硕士研究生,主要研究方向:图像处理、超大规模集成电路,E-mail:503454911@qq.com。

李磊(1982-),男,博士,硕士生导师,副研究员,主要研究方向:超大规模集成电路。

陈光拓(1989-),男,硕士研究生,主要研究方向:数字信号处理、模式识别。