一种基于Verilog代码的任意分数分频器的设计*

2016-11-30任青莲李东红

任青莲,李东红,2

(1.太原科技大学 电子信息工程学院,山西 太原 030024;2.太原科技大学 华科学院,山西 太原 030024)

一种基于Verilog代码的任意分数分频器的设计*

任青莲1,李东红1,2

(1.太原科技大学 电子信息工程学院,山西 太原 030024;2.太原科技大学 华科学院,山西 太原 030024)

分频器是数字系统设计中最常见的单元电路,对高稳定和准确的基准时钟源进行不同倍数的分频,以得到同样稳定和准确的信号,为各模块提供所需的时钟频率。介绍了一种分数分频器的实现方法,该分频器能对时钟源信号进行任意分数或小数倍分频,给出了该方法的设计原理及实现的Verilog代码,并利用Quartus Ⅱ软件进行了仿真,仿真波形与硬件结果都验证了设计的正确性。该方法结构简单,可避免出现竞争冒险和毛刺问题,并且修改方便,具有很好的可移植性,对任何分频器的设计都具有一定的借鉴意义。

分数分频;Verilog;设计;仿真

分频器广泛应用于近代电子系统中,是近代通信系统的重要组成单元电路。它利用一个高稳定和高准确度的基准频率产生出一系列等间隔的离散频率信号,这些离散频率信号与基准频率具有同样的稳定度和准确度。

分频器有整数分频和分数分频。当所需频率与给定基准频率不成整数关系时,或需要对输入信号频率微调整时,可采用分数分频器进行分频。分数分频器输出频率的精度为分频比的小数部分和参考时钟频率的乘积,这样在参考时钟很大时,小数部分如果很小,仍可以得到很小的频率分频率。

本文介绍一种基于Verilog代码的任意分数分频器的设计方法,给出其设计原理和实现方法,该方法可以很方便地实现各种分数分频,而且结构简单,修改也很方便。与传统的分数分频器相比,可避免出现竞争冒险和毛刺问题[1-3]。

1 分数分频器的分频原理

假设基准时钟源的频率为fin,期望得到的输出频率为fout,则其分频比为:

(1)

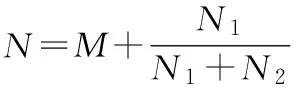

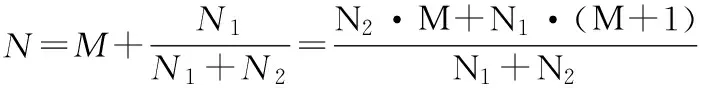

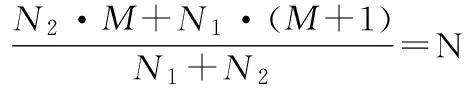

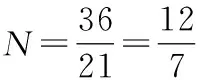

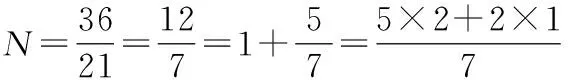

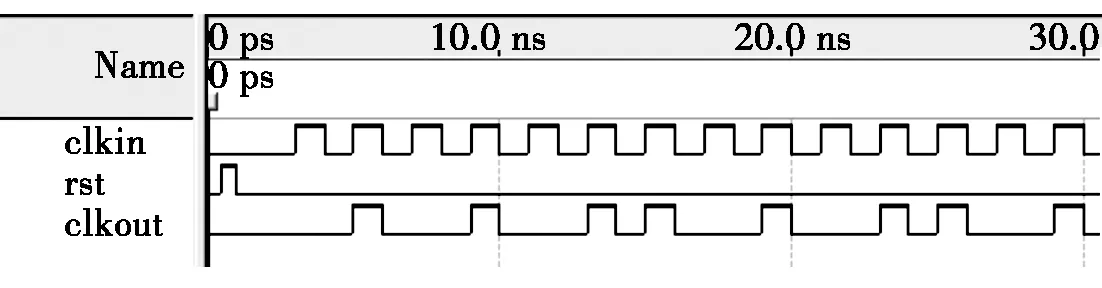

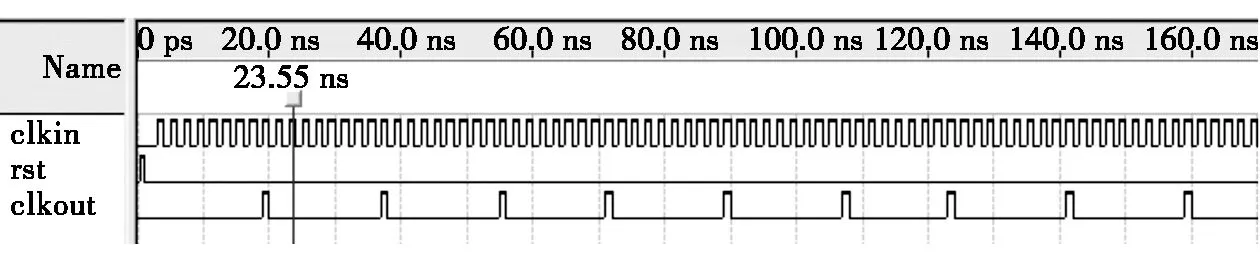

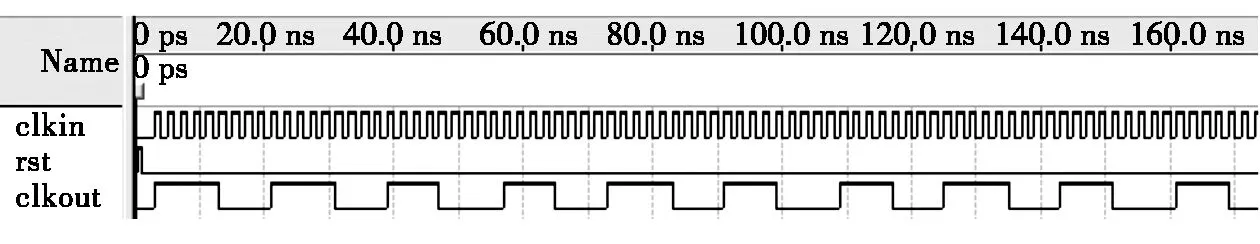

其中N>1,假设M (2) 其中N1、N2为整数。当N1、N2取不同整数时,就可实现任意分数分频。 根据: (3) 可得分数分频是通过可变分频比和多次平均的方法实现的。分频器设置两个分频模数,分别为M和M+1,它们的分频次数分别设置在N2和N1,在一个输出信号的完整的周期(N1+N2)中,若输入信号的周期为N2·M+N1·(M+1),即在周期为N2·M+N1·(M+1)的输入信号中,进行了N2次M分频和N1次(M+1)分频,则可得到周期为(N1+N2)的输出信号,所以,分频器的分频比为: 令Q=N1+N2,P=N2·M+N1(M+1),则分频比又可以写成: (4) 其中P、Q均为整数,且P>Q。可得当基准时钟源每输入P个脉冲时,按照一定规律删除(P-Q)个脉冲,并使删除的(P-Q)个脉冲位置相对均匀地分布在时钟源相对应的P个脉冲中,输出Q个脉冲,便实现了平均意义上的N分频。 通过分析可知,分数分频的两种分频比可通过脉冲删除电路来实现。具体设计思路为:设置一个计数器,设其初始值为0;在基准时钟源的每个上升沿到来时,计数器加上Q,若结果大于等于P,则将计数器的值减去P,并不删除脉冲;若结果小于P,则删除脉冲。 例如,要从36 MHz的基准时钟源产生21 MHz的时钟信号,由公式(1)可得分频比为: 设计数器的初始值为0,在基准时钟源的每个上升沿到来时,计数器加上7,若结果大于等于12,则将计数器的值减去12,并不删除脉冲;若结果小于12,则删除脉冲,这样当基准时钟源每输入12个脉冲时,删除5(12-7)个脉冲,并使删除的5个脉冲位置相对均匀地分布在时钟源相对应的12个脉冲中,输出7个脉冲,便实现了平均意义上的12/7分频。 又因为: 可知在输出信号的7个脉冲中,其中有5次是对输入信号2分频得到,2次是1分频得到的。 其工作过程如表1所示。 表1 12/7分频器的工作过程 从表1可知,在基准时钟源每输入12个脉冲信号,输出端就会得到7个脉冲信号,其中2个脉冲是对输入进行次1分频得到,5个脉冲是对输入信号进行2分频得到的,所以分频比为12/7[3-7]。 设分数分频器的分频比为N=P/Q,P、Q均为整数,且P>Q。任意分数分频器Verilog代码如下。 本例中P=12,Q=7。应用中只要根据实际需要求出相应的P和Q,改变代码中的P、Q参数值即可。 module clk_divider(rst,clkin,clkout); input rst,clkin; output clkout; reg clkout,delete; integer count; parameter P=12,Q=7; always @(posedge clkin or posedge rst) begin if(rst) begin count=0;delete=1′b0;end else begin count=count+Q; if(count>=P) begin count<=count-P; delete=1′b0; end else delete=1′b1; end end always @(delete) begin if(delete) clkout=1′b0; else clkout=clkin; end endmodule 当分频比为小数时,可以将其化为分数形式,求出相应的P和Q值。例如分频比为8.7,化为分数形式为87/10,即P为87,Q为10,输入信号每87个周期输出端得到10个脉冲,其中有3个脉冲是对输入进行了8分频得到,7个脉冲是对输入进行9分频得到的[3-10]。 分数分频器设计FPGA器件选择Cyclone 系列中EP1C12Q240C8N芯片,在QuartusII软件中设计并仿真。分频比为12/7的仿真结果如图1所示。可以看出经过基准时钟源12个周期,输出7个周期信号,实现了12/7的分频输出。当输入36 MHz的基准时钟源时,输出端可得到21 MHz的时钟信号。 图1 12/7分频仿真结果 当分频比N>2,比如分频比为87/10的仿真结果如图2,如果希望信号的占空比尽量接近50%时,可将分母扩大2倍作为Q值,最后再对输出进行2分频。只要改变Verilog代码中的Q值,再加入一个二分频进程即可,仿真结果如图3所示。 图2 8.7分频仿真结果 图3 8.7分频扩大占空比后的仿真结果 从图2和图3的仿真结果可以看出,输入每87个脉冲,输出端就会得到10脉冲,均实现了87/10分频。并且图3输出脉冲的占空比要比图2输出脉冲的占空比大。仿真波形与硬件结果都验证了该设计的正确性。 本文给出了一种基于Verilog代码的任意分数分频器设计方法。设计思路简单,结构清晰,能够非常方便地实现各种分数和小数分频,只需根据实际要求计算得出所需分频的分数值,根据得出分子和分母修改代码中的参数即可,该实现方法具有良好的可移植性,对任意分数或小数分频器的设计都具有一定的指导意义。 [1] 董尚斌.电子线路(Ⅱ)[M].北京:清华大学出版社,2008:334-337. [2] 孟令部.2~2.4 GHz分数分频频率综合器设计[D].上海:复旦大学,2010:20-26. [3] 王金明,徐志军,苏勇.EDA技术与Verilog HDL设计[M].北京:电子工业出版社,2013:213-250. [4] 李雪梅,周思敏.基于FPGA的数字分频器设计与实现[J].北京电子科技学院学报,2013,21(4):80-84. [5] 周冬成,王永斌,郑亚平.基于FPGA的小数分频频率合成器设计[J].电子测量技术,2006,29(3):79-80. [6] 袁泉,陈晓龙,王家礼.基于FPGA的小数分频实现方法[J].电子技术应用,2010,36(11):99-101. [7] 王晋伟,崔永俊,贾磊,等.高精度模拟分频电路的设计与实现[J].科学技术与工程,2015,15(15):44-48. [8] 杨承光.应用于GPS中的∑-Δ小数分频电路的研究[D].西安:西安电子科技大学,2012:7-19. [9] 李广参,冯永新,钱博,等.基于FPGA的BPSK信号载频估计单元设计与实现[J].电子技术,2014,7:38-41. Design of Arbitrary Fractional Frequency Divider Based-on Verilog Ren Qinglian1,Li Donghong1,2 (1.CollegeofInformationEngineering,TaiyuanUniversityofScienceandTechnology,TaiyuanShanxi030024,China; 2.CollegeofInformationEngineering,HuakeUniversity,TaiyuanShanxi030024,China) Frequency divider is a common unit circuit in digital system.The high stable and accurate signal is divided into different frequency signal with the same stability and curacy that provides the required clock frequency for each module.A realization method of arbitrary fraction or decimal fraction frequency division is presented.The principle of the design and the code based on Verilog are also presented,and their functions are simulated using Quartus.The simulation waveforms and hardware results verify the correctness of the design.This method is simple and can avoid competition risks and burr.The design method can also be easily modified and has good portability,so it has reference for the design of any arbitrary frequency divider. fractional frequency; Verilog; design; simulation 2016-06-30 山西省2014年教育教学改革研究项目(J2014152) 任青莲(1973-),女,山西长治人,副教授,硕士,研究方向:无线通信及电子技术应用。 1674-4578(2016)05-0020-03 TN74 A

2 Verilog代码实现

3 仿真结果及分析

4 结论