2.4 GHz低噪声放大器设计

2016-11-25韦可雷袁乃昌

韦可雷,郭 敏,黄 雷,袁乃昌

(国防科学技术大学 电子科学与工程学院,湖南 长沙 410073)

2.4 GHz低噪声放大器设计

韦可雷,郭 敏,黄 雷,袁乃昌

(国防科学技术大学 电子科学与工程学院,湖南 长沙 410073)

低噪声放大器是信号接收前段的重要部件,它的性能决定了整体接收机系统的信噪比。本文介绍了一种基于英飞凌公司的BFP740ESD放大器设计的宽带低噪声放大器的设计过程,采用2级芯片级联放大的方法,首先通过ADS2013建模仿真,确定放大器的原理图;然后根据原理图绘制PCB版图。实物测试结果得到,在2.3~2.5 GHz的范围内增益为32 dB左右。在室温下,噪声系数低于1.5 dB,在中心频率2.4 GHz时,输入端的S11达到-20 dB,达到预期设计要求,具有良好性能。

低噪声放大器;ADS;噪声系数;增益

低噪声放大器处于信号接收系统的前端,其主要作用是放大天线从空中接收到的微弱信号,减小噪声干扰,以供系统解调出所需的信息数据[1]。对于接收机系统,噪声系数NF决定了系统的灵敏度。对于多级级的系统来说,第一级的噪声系数决定了整个系统的噪声系数。所以,低噪声放大器的设计对整个接收系统重要,是提高整体系统灵敏度重要方法。

目前,利用微波电路设计软件,结合可靠的LNA设计理论来进行电路设计,可以避开复杂的理论计算,极大地提高设计准确性和效率,有效缩短研制周期,降低成本。Agilent公司的ADS软件由于其强大的功能而广泛应用于射频微波电路的仿真和优化设计。低噪声放大器的主要技术指标有噪声系数NF,增益G,输入端反射系数S11。低噪声放大器的设计目标就是在尽量低噪声的情况下,提高增益,同时S11尽量低。

1 低噪声放大器的设计

本次设计使用ADS软件来进行电路设计,可以避免复杂的理论计算,有效缩短研制周期,降低成本。并且该放大器工作频率为2.4 GHz,为开放公共使用频段,在ADS中有参考工程可以借鉴。

1.1 器件选择与整体级数确定

英飞凌公司是全球知名半导体生产商,其生产的半导体涵盖有线和无线通信、汽车和工业电子、计算机安全等应用。本次设计采用的英飞凌低噪声放大器BPF740ESD,是一款低噪声宽带两极NPN射频晶体管。高增益低噪声的特点使其尤其适合移动通信应用领域。并且该芯片采用英飞凌的可靠高电压SiGe:C异质结构技术,使其工作电压Vceo高达4.2 V,Ic达到45 mA。资料手册表明,在2.4 GHz的频率上,其增益可达到20 dB以上,为达到至少30 dB的增益要求,故采用2级增益放大设计。

1.2 偏置电路设计与稳定性分析

偏置电路的设计可借助ADS中的直流分析模板DC Tracing,结合芯片手册,确定直流工作点。首先设计单级偏置电路,后一级采用同样的直流偏置电路。下载芯片的ADS参数模型,导入到软件中,结合芯片手册最终确定集电极电流为13.1 mA,集极电压由电子分压得到。放大器的稳定性,直接决定了放大器能否正常工作,若使放大器正常工作,则必须满足如下判定条件:

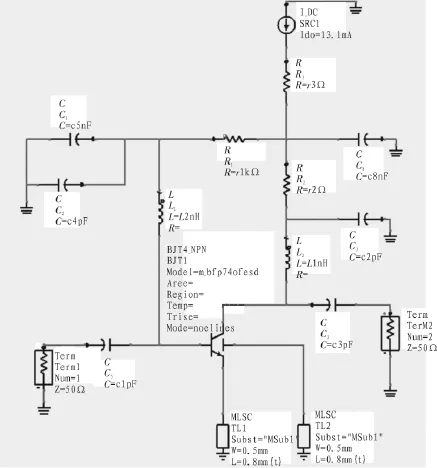

在电路两端,添加50欧端口,并调用StabFact控件,来绘制稳定系数曲线。只有绝对稳定系数K>1时,放大器才稳定。使系统稳定的方法,最常用的就是添加负反馈[3]。在本设计中,在发射极添加可调电感值,调节其大小,观察稳定系数曲线,在2.3~2.5 GHz范围内,由K值大于1来确定其值大小。最总确定,其电感值为0.35 nH,电感值过小,集中参数元件中无对应值,则可以用微带线来代替。本设计中,微带线的介质采用FR4材料,其参数介电常数Er=4.4,板厚1 mm,通过ADS中的LinCalcu工具计算得到其对应的微带线宽度和长度。第一级放大器电路原理如图1所示。

图1 单级放大器原理图

1.3 匹配电路设计

本设计采用两级放大,故两级放大器之间需要添加匹配电路,使第二级电路输入电阻与匹配到第一级输出电阻。同时对于此低噪声放大器,为使整个电路噪声系数较小,输入端应做最小噪声匹配。为使放大器增益尽量大,第二级应当做最大增益匹配。

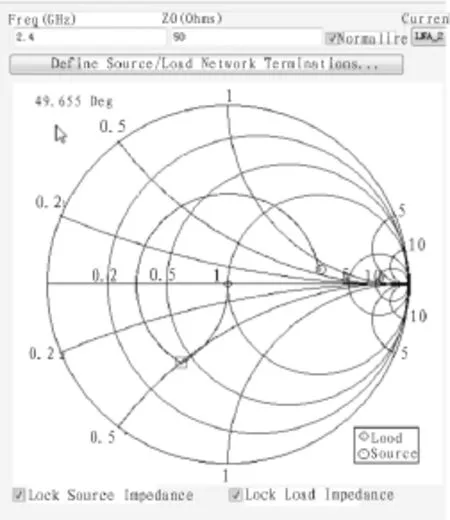

在做匹配电路前,将单级放大器中的理想集中参数元件,换为实际的器件。可以通过将实际元器件模型导入到软件中,代替理想元件。输入端的最小噪声匹配首先需要借助最小噪声系数圆确定输入端的输入阻抗,然后利用Smith圆图匹配工具Smith Chart Utility对输入端进行匹配[4],因为本设计所有连接线的特性阻抗为50欧姆,所以将其匹配到50欧姆。匹配结果如图2所示:由输入端阻抗匹配到中心点。

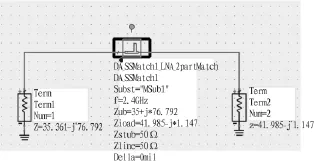

两级放大器间的阻抗匹配通过微带单枝短截线匹配控件SSmtch来自匹配如图3所示。

对输出端的最大输出匹配可采用类似输入端最小噪声匹配的方法,首先得出输出端输出阻抗,在通过Smith Chart Utility进行匹配。

图2 输入端最小噪声匹配

图3 两级放大器间的阻抗匹配

1.4 综合优化与制版

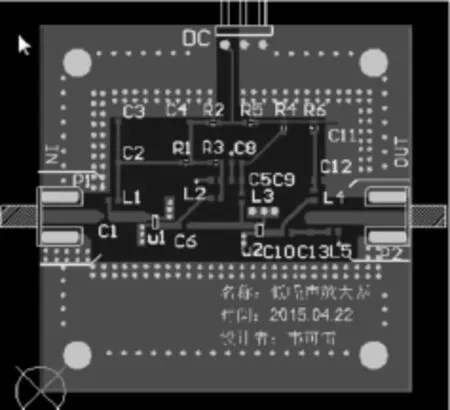

调用ADS中的OPTIM控件,并设置几组优化目标,包括S11<-10 dB,S21>30 dB等,对输入端的电容,发射极反馈电感等对性能敏感的值设置为变量,来综合优化电路,并且可以手动调节这些变量,使噪声系数、增益、输入端反射系数达到最优的组合。优化完成后,利用 PCB绘制软件 Altium Designer绘制此设计的PCB版图,如图4所示。

图4PCB版图

2 实验测量与结果

2.1 增益、反射系数测量

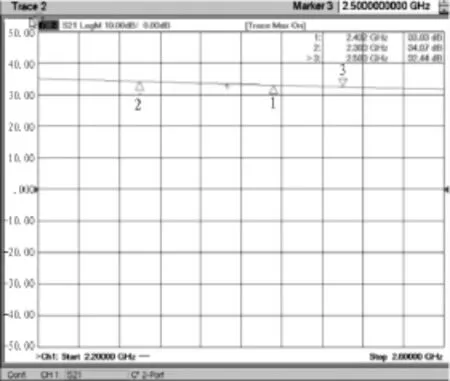

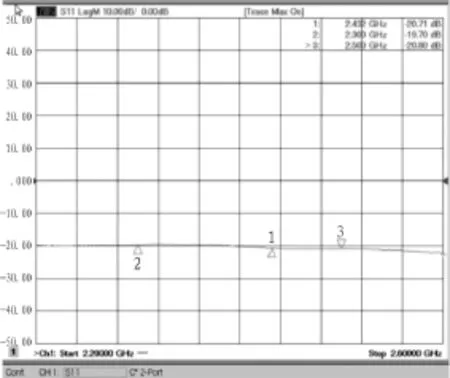

将低噪声模块接入矢量网络分析仪中,可以测得其主要S参数如下图所示。测量仪器为Agilent N5230C网络分析仪。

图5 实测S21结果

可以看到S21在32 dB左右,且在测量的范围内2.2~2.6 GHz内,增益较平坦。在2.4 GHz频点上有33 dB的增益,达到设计要求。S11在-20 dB左右,满足设计指标,说明输入匹配很好,反射系数较小,具有良好的性能。

图6 实测S11结果

2.2 噪声系数测量

将噪声源接入低噪声放大器输入端,在接入到Rohde& Schwarz的频谱分析仪中,选择噪声测量,校准一段时间后,得到测量数据如表1所示。

表1 噪声系数测试结果

可以看到,噪声系数也具有较好的性能。

3 结束语

文中通过在ADS中基于BFP740ESD构建仿真模型,详细介绍了仿真、优化过程,并给出了实物版图,实测数据,具有参考意义。实测结果看出,此低噪声放大器具有量好的性能,能够满足接收机系统的要求,并且和ADS仿真效果相差不多,所以ADS的使用有效的缩短了开发时间,提高了设计效率。

[1]徐福兴.ADS2008射频电路设计与仿真实例[M].北京:电子工业出版社,2009.

[2]丁鹭飞,耿富录.雷达原理[M].西安:西安电子科技大学出版社,2009.

[3]唐海啸,张玉兴等.利用ADS软件设计X频段低噪声放大器[J].电视技术,2006(3):119-122.

[4]毕娜娜.刘德喜.Bi Nana.LiuDexi C频段低噪声放大器的设计[J].遥测遥控,2015(3):37-41.

[5]黄智涛.射频小信号放大器电路设计[M].西安:西安电子科技大学出版社,2008.

[6]李瑞,耿立明.Altium Designer 14电路设计与仿真从入门到精通[M].北京:人民邮电出版社,2014.

The design of 2.4 GHz LNA

WEI Ke-lei,GUO Ming,HUANG Lei,YUAN Nai-chang

(College of Electronic Science and Engineering,Nationl University of Defense Technology,Changsha 410073,China)

The low noise amplifier is an important part of the signal receiver.Its performance determines the SNR of the whole receiver system.This paper introduces a design process of a broadband low noise amplifier based on the BFP740ESD chip of InfineonCorporation.The method of 2 stage chip cascade amplification is adopted.Firstly,the principle of the amplifier is determined by ADS2013 modeling simulation.Then,the PCB layout is drawn according to the schematic diagram.Test results are obtained,and the gain of 2.3~2.5GHz is about 32 dB.At room temperature,the noise figure is lower than 1.5dB,and the S11 reached-20 dB at the center frequency 2.4 GHz,and the input terminal achieves the expected design requirements,and has good performance.

LNA;ADS;noise figure;gain

TN72

A

1674-6236(2016)18-0172-03

2015-09-15 稿件编号:201509106

韦可雷(1992—),男,安徽临泉人,硕士研究生。研究方向:微波固态电路设计与数字电路设计。