基于FPGA和CAN控制器软核的CAN总线发送系统的设计与实现

2016-11-17关俊强左丽丽吴维林祝周荣

关俊强,左丽丽,吴维林,祝周荣

(上海航天技术研究院 上海航天电子技术研究所,上海 201109)

基于FPGA和CAN控制器软核的CAN总线发送系统的设计与实现

关俊强,左丽丽,吴维林,祝周荣

(上海航天技术研究院 上海航天电子技术研究所,上海 201109)

基于FPGA嵌入式片上系统可编程技术,采用现有的CAN总线控制器软核模块,设计了软核控制程序,将由CAN控制器软核及其控制程序组成的CAN发送软件嵌入在FPGA内部,开发了CAN总线通信系统,实现了对CAN总线数字量的发送;经过软件仿真验证、静态时序分析和硬件系统测试,仿真和测试结果表明,该系统设计合理,方案可行,时序正确,功能、性能满足要求;系统将硬件软件化,有效的减少了外围芯片的数量,降低了系统的体积和功耗,提高了产品的集成度、通用性和可靠性,具有良好的实用价值和推广前景。

FPGA;CAN总线;CAN控制器;软核

0 引言

CAN总线是一种适用于分布式控制或实时控制的串行通信网络。由于采用了非破坏性总线仲裁技术等许多新技术及其独特的设计,CAN总线与一般的通信总线相比,性价比高、容错能力强、通信速率高,数据通信具有突出的可靠性、实时性和灵活性。CAN的上述优点使其目前应用范围不再局限于汽车工业,而拓展到了航天电子、机械工业、纺织机械等领域,而且已经形成国际标准,是目前为止唯一有国际标准的现场总线,是公认的几种最有前途的现场总线之一[1]。

传统的CAN总线通信系统如文献[2]、文献[3]介绍的一般由单片机和CAN控制器SJA1000芯片以及收发器PCA82C250/251芯片组成,但是单片机速率较低,资源少,遇到强电磁干扰程序很容易跑飞,这种现象在航天控制领域表现得非常突出[4]。文献[4]、文献[5]提出了由FPGA、CAN控制器SJA1000芯片以及收发器PCA82C250组成的CAN通信系统。上述这些方案虽然技术成熟,性能可靠,但外围芯片较多,集成度不高,通用性不好,需要占用较多的印制板空间,很难适用于对电路体积和功耗要求苛刻的场合,因此,研究开发一种体积较小,功耗较低、集成度较高,适用于小型化应用的CAN总线通信系统是十分必要的。

鉴于目前基于FPGA嵌入IP核的片上可编程系统得到了广泛应用,本系统选用高密度ACTEL FPGA芯片,采用现有的CAN控制器软核模块,自行设计开发了软核发送控制程序,将软核及其控制程序组成CAN总线发送程序,嵌入在FPGA芯片内部,组成了CAN总线通信系统。硬件上主要采用一块FPGA芯片,配合一片CAN接口芯片即可实现CAN总线数据的通信。该电路有效的减少了外围芯片的数量,降低了产品的体积、重量、功耗和复杂度,提高了产品的集成度、可靠性和通用性,特别适用于需要小型化设计的数字量采集系统。

1 CAN总线通信系统硬件设计

FPGA芯片具有集成度高、功耗低、重量轻的优点,因此,本文设计的CAN总线发送系统硬件上主要由一块FPGA芯片作为核心控制单元,外加一片外围CAN接口芯片组成,CAN发送控制软件采用Verilog硬件描述语言编写,和受其控制的采用VHDL语言编程的CAN控制器软核一起,嵌入FPGA芯片内部,配合实现系统功能。选用外部晶振提供系统时钟,频率为16 MHz。

图1 CAN总线通信系统结构框图

FPGA芯片选用ACTEL公司的FLASH型A3P250-VQ100芯片,该芯片属于ProASIC3 FLASH工艺系列FPGA,具有成本低、体积小(14 mm×14 mm)、功耗低、安全性好、可反复编程、无需额外片外配置PROM、独立工作、无上电浪涌电流、加载直接启动和抗单粒子翻转性能好的优点。芯片资源为,具有25万门、6144个D触发器、36Kbits RAM、157个用户IO口、350 MHz的系统性能;支持高级IO接口,静态工作电流小于30 mA[6]。

CAN接口芯片选用SN65HVD233,该芯片是TI公司生产的CAN总线收发器芯片,电源电压3.3 V,最高数据传输速率为1 Mbps,是CAN控制器与物理总线之间的接口,对物理总线传输电路提供差分收发能力,同时它可以用来隔离进行和增强驱动能力,提高系统的可靠性[7]。

2 CAN总线发送软件设计和验证

CAN总线发送程序由CAN控制器软核及其发送控制程序组成,用于控制CAN控制器软核向总线上发送FPGA需要发送的数据。

2.1 CAN控制器软核概述

CAN总线通信系统的核心是CAN控制器,实现了CAN总线物理层和数据链路层的所有功能,用于完成CAN总线的通信和网络协议。

本文采用的已购买的CAN控制器软核,是一种执行CAN通信协议的串行通信控制器,支持CAN 2.0 B规范(标准帧、扩展帧和远程帧),采用VHDL语言自顶向下模块化设计,便于不同应用时对软核进行裁剪。SJA1000软核包括接口管理逻辑、位时序逻辑、位流处理器、错误管理逻辑、传输逻辑、发送缓冲器、接收缓冲器和验收滤波器等功能模块,最高可编程数据传输速率可达1 Mbps,8位数据线主机接口,完全可综合,占用逻辑资源较少[8]。

软核主要接口信号包括时钟clk、异步复位信号rst_b、输入数据信号datain[7:0]、输出数据信号dataout[7:0]、地址adr[5:0]、片选信号cs_b、读信号rd_b、写信号wr_b、中断信号int、接收信号rxd、发送信号txd等。相对于FPGA可以看做一个存储器外设,FPGA可以通过访问CAN 软核控制器来实现对CAN通信网络上数据的发送和接收。

该CAN控制器软核跟常用的SJA1000控制器芯片工作原理和流程完全相同,只是寄存器地址分配和定义不同,寄存器地址和定义可参见用户手册[8],本文设计的控制程序经过适应性修改可用于SJA1000软核的控制程序设计。

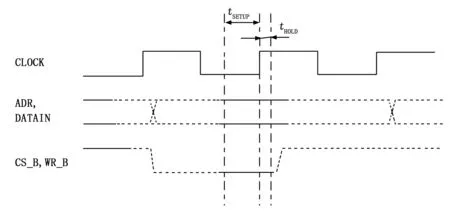

根据软核用户手册[8],写操作和读操作时序要求分别如下图2和图3所示。

图2 CAN控制器软核写操作时序要求示意图

图3 CAN控制器软核读操作时序要求示意图

2.2 CAN总线发送控制软件设计

根据软核用户手册要求,设计CAN 总线发送控制软件对该软核进行初始化配置,设置工作模式,控制节点向总线发送数据。

2.2.1 软件设计与实现

本文设计的软件采用Verilog语言编程,采用一个“三段式”状态机实现控制功能,一次发送流程包括查询操作、写发送缓冲器、发送命令操作,其中,查询操作包括查询中断寄存器和查询状态寄存器。

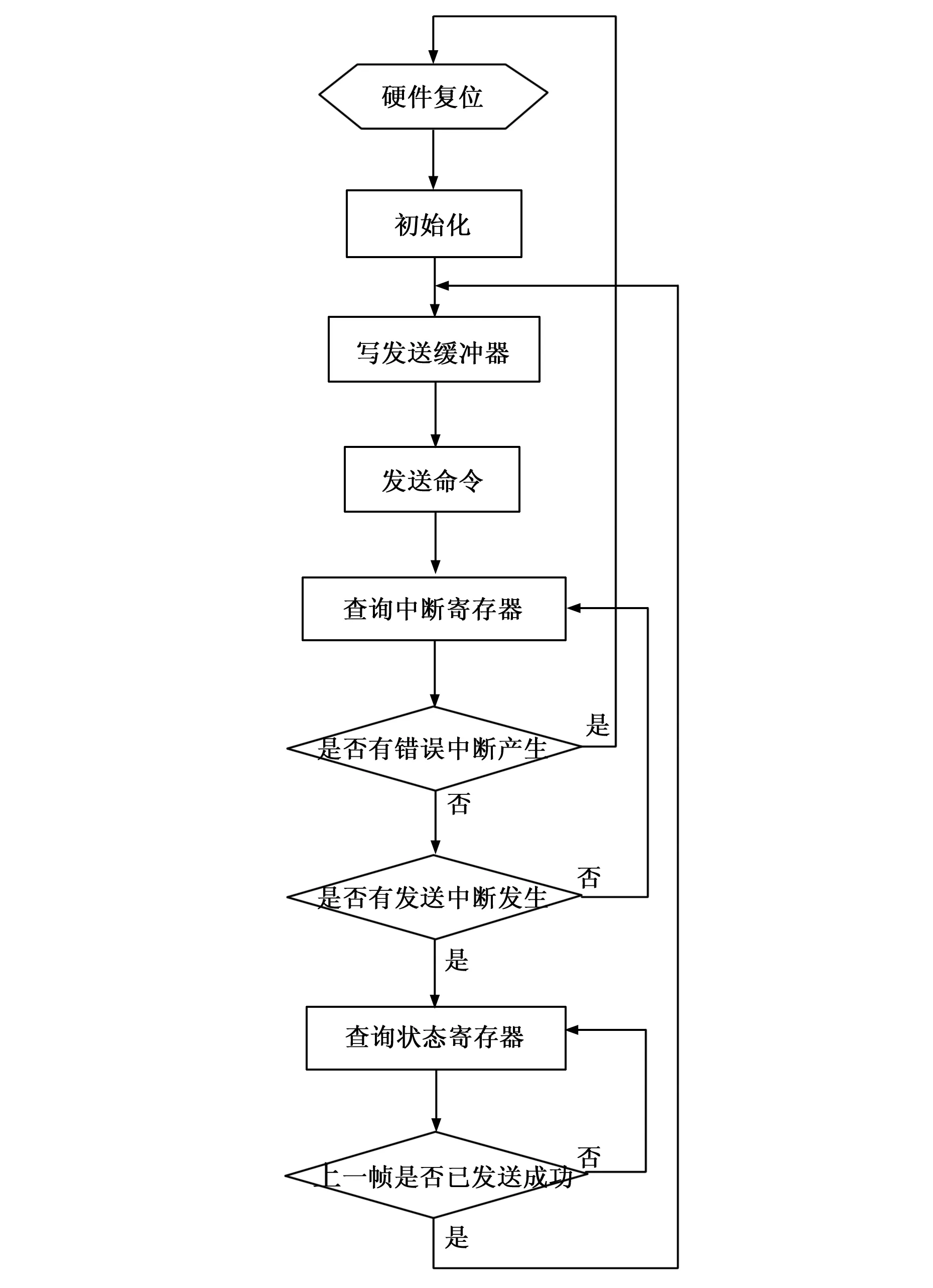

状态机工作流程图如图4所示。

图4 CAN发送控制程序状态机流程图

1)硬件复位:

根据软核用户手册要求,上电后需对软核进行异步复位,复位信号低电平有效。在FPGA软件上电复位后,控制状态机输出一定宽度的低电平复位信号rst_b_t;

2)初始化:

硬件复位完成后,需对CAN 控制器软核进行初始化,配置软核工作模式。根据IP软核用户手册中寄存器地址和定义要求,需先后对11个功能寄存器进行配置。

软件借用ROM的思想,将寄存器地址和数据统一编码,存储在ROM中,按照一定的顺序依次输出。

先向控制寄存器(地址为6’h20)写入数据8’hF8,以使CAN控制器进入软件复位模式,可以进行工作模式配置;然后对验收代码寄存器(地址为6’h24、6’h25、6’h26)均写入数据8’h00,对验收屏蔽寄存器(地址为6’h27、6’h28、6’h29)均写入数据8’h11,对附加寄存器(地址为6’h2B)写入数据8’h47,以配置验收滤波寄存器对接收数据标识符不进行校验,设置同步跳转宽度为2;对位定时寄存器(地址为6’h2A)写入数据8’hB4,设置采样点位置为80%;由于本文时钟频率为16 MHz,对时钟分频寄存器(地址为6’h2C)写入数据8’h01,配置总线波特率为500 Kbps;最后,对控制寄存器(地址为6’h20)写入数据8’h78,退出复位模式,进入工作模式。

软件初始化过程前仿真波形图如图5所示。

图5 初始化过程前仿真波形图

3)写发送缓冲器:

本文采用标准帧模式,发送缓存器地址为6’h10~6’h19,其中6’h10、6’h11为节点帧ID标识符地址;6’h12~6’h19为发送数据地址,共8字节。写发送缓冲器过程前仿真波形图如图6所示。

4)发送操作:

对命令寄存器地址6’h21写入数据8’h40,启动按照标准帧格式发送数据。

前仿真波形图如图6所示。

5)查询操作:

(1)查询中断寄存器:

发送完毕后,不断查询中断寄存器,进行相应的操作。

中断寄存器地址为6’h23,当读到该地址数据的第4bit为1时,表示总线发生错误,转入硬件复位流程进行复位操作,使软件重新开始工作。当读到数据的第2bit为1时,表示数据已经成功发送完毕,状态机转入查询状态寄存器状态;否则,继续查询中断寄存器。

(2)查询状态寄存器:

状态寄存器地址为6’h22,读取该地址数据,如果第4bit为0,表示上一次发送尚未完成或者还没有开始发送,如果第5bit为0,表示发送缓冲器已满,锁定不可用,如果第6bit为1,表示接收缓冲器已满,这3种情况下均不能发送数据,状态机继续查询状态寄存器。

如果读取数据第4bit为1,表示上一次写入发送缓冲器的数据已经成功发送,第5bit为1,表示发送缓冲器可以使用,第6bit为0,表示接收缓冲器为空,这3种条件都满足时,可以发送数据,状态机转入步骤3)写发送缓冲器状态进行下一次发送操作。

查询操作前仿真波形图如图6所示,中断寄存器数据为8’h04,表明没有发生总线错误,发送请求已经被成功完成,状态寄存器数据为8’h30,表明上一帧写入发送缓冲器的数据已被成功发送,发送缓冲器可以使用,而且接收缓冲器为空,状态机可以转入写发送缓冲器状态。

图6 3)、4)、5)各流程前仿真波形图

6)读写操作:

在上述流程2)、3)、4)对寄存器或者发送缓冲器进行写操作时,状态机均需要转入写流程,对软核输出片选信号cs_b、和写信号wr_b,配合各流程输出地址adr[5:0]和数据datain[7:0]进行相应的写操作。

在上述流程5)对寄存器进行读操作时,状态机需要转入读流程,对软核输出片选信号cs_b、读信号rd_b,配合各流程输出地址adr[5:0]进行相应的读操作,从软核dataout[7:0]读出数据。

写操作、读操作仿真时序图分别如图7、图8所示,读周期和写周期最小值均为375 ns,写操作时,地址和数据的建立时间和保持时间均为187.5 ns。

图7 写操作前仿真波形图

图8 读操作前仿真波形图

2.2.2 可靠性、安全性设计

1)进行降额设计,对FGPA内部逻辑资源占用率不超过80%,最大时钟速率降额80%;

2)FPGA设计时编程语言和风格应符合相关设计规范的要求;

3)对需要采用分频时钟的模块,采用系统时钟和时钟使能实现同步电路,提高时序性能;

4)状态机编码采用Gray码,综合时采用安全模式,防止状态机跳转到非法状态而发生状态机死锁。

5)软件只使用系统时钟上升沿,提高时序性能。

2.3 软件仿真验证

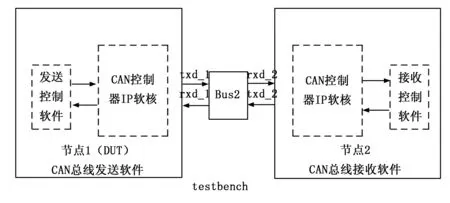

将CAN总线发送软件作为DUT,编写测试床(testbench),采用VCS 2011仿真工具进行功能仿真和时序仿真,验证软件功能。

编写了一个由2个节点组成的CAN总线通信系统仿真测试环境,包括节点1、节点2和CAN总线两节点连接模型Bus2,testbench组成框图如图9所示。

由DUT作为节点1负责发送数据,testbench中的接收软件作为节点2负责接收数据,接收软件包括接收控制软件和CAN控制器软核。

图9 仿真激励模型组成框图

将节点2和DUT中的CAN控制器软核按照同样的方式进行初始化,设置总线数据通信波特率为0.5 Mbps。向节点1发送缓冲器地址6’h10~6’h19依次写入数据8’hA7、8’hE8、8’h11~8’h18,前两个字节表示节点1的ID标识符为11’h53F,8’h11~8’h18为8字节发送数据包,将数据写入发送缓冲器,然后向命令寄存器6’h21写入数据8’h40,启动发送,发送格式为标准帧。

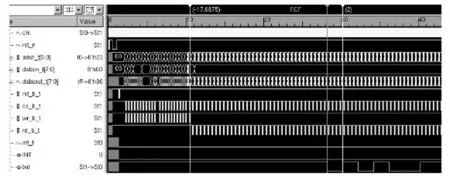

CAN总线发送软件各流程VCS前仿真时序波形图见前文图5~图6所示。

在写入发送命令17.7 us后,发送接口txd开始输出发送数据,239.7 us发送完毕,发送数据周期为2 us,波特率为0.5 Mbps,采样点位置为80%,仿真波形图见图10所示。

图10 txd发送数据波形图

testbench中的节点2在初始化完成后,rxd_2接口上接收到总线数据,在接收中断有效后,节点2开始读取接收缓冲器数据,依次读地址为6’h00~6’h09的接收缓冲器,读到的第一帧数据为8’hA7、8’hF1、8’h11~8’h18,前2个字节表示ID标识符为11’h53F,数据长度为8字节,接收到的ID标识符和数据均与发送节点1发送数据完全一致。节点2接收数据前仿真波形图如图11所示。

设置节点1继续连续发送多帧数据,节点2均能正常接收数据,观察节点1发送错误计数器和节点2接收错误计数器,均显示数值为0,说明没有发生发送和接收错误,总线工作正常。

图11 testbench节点2接收数据波形图

由此可见,CAN总线发送软件功能正确,能够按照配置的工作模式,向总线正确发送数据。

2.4 静态时序分析

软件采用Designer布局布线后资源占用情况见图12所示,逻辑资源占用率约为53%。采用SmartTime工具进行静态时序分析,分析结果见图13所示,最大工况下,系统时钟最高工作频率约为33.5 MHz,本设计实际工作频率为16 MHz。逻辑资源占用率和工作频率均满足降额80%要求。

在最大工况、典型工况和最小工况下,各条时序路径建立时间和保持时间余量均为正值,满足要求。

图12 布局布线后资源使用情况图

图13 时序性能分析结果图

2.5 实验结果分析

在Libero IDE v9.1开发环境下对CAN发送软件进行编译,选择ACTEL公司FLASH型ProASIC3系列A3P250-VQFP100-std芯片,采用Synplify Pro2010综合生成网表文件,最后采用Designer生成pdb下载文件,烧入FPGA芯片,经过系统硬件测试,在常温和高低温(符合芯片工作温度范围)情况下,FPGA均能够按照设定的工作模式,向总线正常发送数据,实现可靠的数据通信。

3 结论

本文在分析比较几种传统CAN总线通信系统技术方案优缺点的基础上,基于FPGA嵌入式片上系统可编程技术,采用现有的CAN控制器IP软核模块代替CAN控制器芯片,设计了采用verilog语言编写的CAN总线发送控制软件对CAN控制器软核进行控制,将软核及其控制程序嵌入一块高密度、小体积的ACTEL FPGA芯片,组成一种小型化、高集成度、高可靠性的CAN总线通信系统,成功实现了对CAN总线数字量的正确发送。

通过对软件的仿真验证、静态时序分析,以及最后的系统硬件测试,仿真和测试结果表明,本文提出的技术方案设计合理、方案可行,设计的软件时序性能良好、功能正确,系统具有较强的实用性、通用性和可靠性。跟传统CAN通信系统相比,该系统极大的减少了外围芯片的数量,降低了系统的体积、重量和功耗,提高了系统的集成度、通用性和可靠性,可用于实现需要小型化、通用化设计的CAN通信系统。

[1] 饶云涛,邹继军,等.现场总线CAN原理与应用技术(第2版)[M].北京:北京航空航天大学出版社,2007.

[2] 吴 坎.基于SJA1000和PCA82C250的CAN总线接口设计[J].机械设计与制造,2010,17(7):57-58.

[3] 王毅峰,李令奇.SJA1000在数据采集与控制系统中的应用[J].微计算机信息,2001,17(4):16-18.

[4] 陈 萍,姜秀杰.基于FPGA的CAN总线通信系统[J].计算机测量与控制,2009,17(12):16-18.

[5 ] 武星星,刘金国,周怀得,等.基于TSC695F和FPGA的CAN总线接口设计[J].计算机测量与控制,2012,20(11):3032-3034.

[6] Microsemi,Inc.ProASIC3 Flash Family FPGAs Datasheet[Z].2010:1-6.

[7] SN65HVD233 Datasheet[Z].Texas Instruments.

[8] CAN Controller Core User’s guide[EB/OL].http://www.cast-inc.com.

Design and Implementation of a CAN Data Transmission System Based on FPGA and CAN Controller Soft Core

Guan Junqiang, Zuo Lili, Wu Weilin, Zhu Zhourong

(Shanghai Institute of Aerospace Electronic Technology, Shanghai Academy of Spaceflight Technology,Shanghai 201109, China)

Based on FPGA embedded programmable technology,adopted an existing CAN Controller Soft Core, and designed a CAN Bus transmission software which consists of the Soft Core and its control software. The transmission software which is embedded in a FPGA chip, together with the FPGA, form a CAN bus transmission system, which can transmit digital signals to the CAN bus. Through simulation, static timing analysis and hardware system testing, the results indicate that the system design and scheme of this paper is reasonable, feasible, and the timing is correct and its functions and performance can meet the design requirements. Design of this paper implements the function with software instead of hardware, minimizes the use of peripheral chips, makes the system have small volume, low cost and power consumption, high integrity, reliability and generality, and these advantages that this system possesses make it have good practical value and application prospects.

FPGA; CAN bus; CAN controller; soft core

2015-12-17;

2016-01-27。

关俊强(1985-),男,山西忻州人,硕士,工程师,主要从事航天FPGA产品的设计和验证方向的研究。

1671-4598(2016)03-0281-04

10.16526/j.cnki.11-4762/tp.2016.03.077

TP336

A