AD8302在鉴相系统中的应用

2016-11-17涂正林刘恩凯

涂正林,刘恩凯

(中国船舶重工集团公司第723研究所,扬州 225001)

AD8302在鉴相系统中的应用

涂正林,刘恩凯

(中国船舶重工集团公司第723研究所,扬州 225001)

介绍了以AD8302为基础的鉴相系统在测频测向系统中的应用、设计概况和解模糊方法。这种设计使鉴相系统体积缩小并简化,可广泛应用于军事、通信、电力等领域。

鉴相系统;解模糊;反应时间

0 引 言

当前鉴相系统,以数字式瞬时测频(DIFM)最为典型,它由正交相关器、延时线、检波器及编码板等构成,具有体积小、重量轻、鉴相测频速度快,精度高等优点。随着数字器件的飞速发展,更高技术新型瞬时测频也在不断涌现,如基于高速模/数转换器(ADC)的全数字信道化瞬时测频,超导延时线瞬时测频,多路移相时钟瞬时测频,集成鉴相芯片瞬时测频,与目前通用的DIFM相比他们有体积更小,同时信号及信号分析等功能更强大等优点。本文将重点介绍基于AD公司的AD8302芯片为基础的小型鉴相系统及其拓展应用的一些想法。

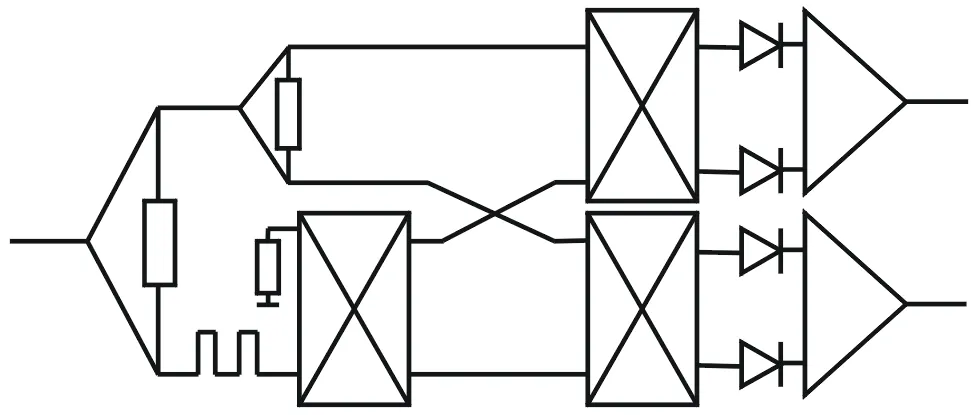

1 数字式瞬时测频正交鉴相器的架构

当前瞬时测频主要由限幅放大器、功分器、正交相关器、延时线、检波器、差分运算放大器、高速比较器、编码控制板组成,根据体积和编码位数等要求,可分为4通道、5通道和7通道相关器组,除相关器数量区别外,功能、结构和编码方法大体一样。单通道结构如图1所示[1]。

图1 单通道相关器结构

这种相关器组体积较小,重量和体积主要集中在相关器、限幅放大器、延时线上,工作带宽有2~8 GHz,4~6 GHz,8~18 GHz等,测频时间达到120 ns左右,能对50 ns脉宽到连续波信号进行测频,通用性较好,能够用于测频测向等多种场合。不过对于体积要求更小的反辐射导弹、反辐射无人机,其体积和重量则略显大[2]。

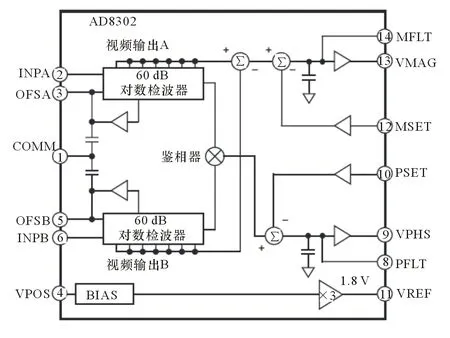

2 AD8302功能简介

AD8302是AD公司推出的高度集成的幅度和相位测量的单片集成电路,能测量从DC~2.7 GHz频率范围内2个输入信号间的幅度比和相位差。该器件将精密匹配的2个对数检波器集成在一块芯片上,将误差源及温度漂移减小到最低限度。其基本参数:

频率范围:DC~2.7 GHz

幅度测量比例系数:30 mV/dB

灵敏度:-60 dB

动态范围:70 dB

相位测量范围:180°

幅度分辨率:30 mV/dB

精确相位测量比例系数:10 mv/°

相位分辨力:优于1°

基准电压偏置:1.8 V

视频带宽响应:30 MHz

由图2可知,2路信号由管脚INPA和INPB输入,管脚IVPHS输出2路信号间的相位差,而管脚IVMAG输出2路信号幅度差。也就是说该器件既可比幅也可比相,这又拓展了它的应用空间。

图2 单通道相关器结构

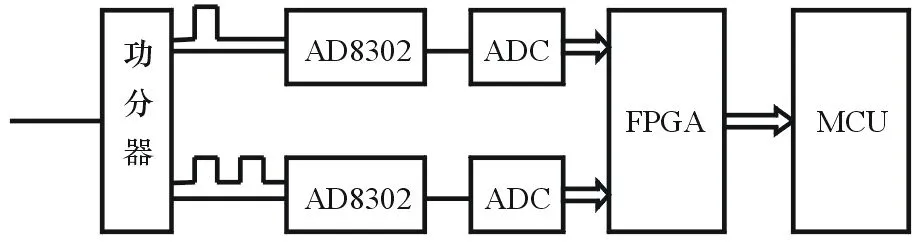

3 基于AD8302瞬时测频的基本架构

根据AD8302的幅相曲线,在较长延迟线中2π内会产生2个或2个以上相位模糊,这时可以采用传统DIFM解模糊方法,即在1∶2延迟线的基础上采用电阻排移相方法解模糊,但有移相不精确的问题;也可以采用正交两路下变频加以解决。这里我们选用两路不规则延迟线的方法,对系统鉴相进行造表比对,用查表对应相位差的方法快速鉴相。基本方案如图3所示。

测频方法:2路AD8302将频域划分为3个区间,ADC采样数据先进行比较编码后确定大概频率区间解模糊,再根据主通道ADC的采样数据相位频率公式计算出相应频率。但是测量相位差并计算出频率这种方法不仅需要CPU不停从ADC读入相位码,还需要CPU解算相应的频率码并上报,浪费CPU资源,同时也延长了系统反应时间。因此频率码可采用码表对应的方式产生,工作时以ADC采样值即相位差作为位地址,频率码为数据存在相应地址内即可,以列表形式保存在FPGA中。

图3 AD8302瞬时测频的基本架构

3.1 频率区域划分

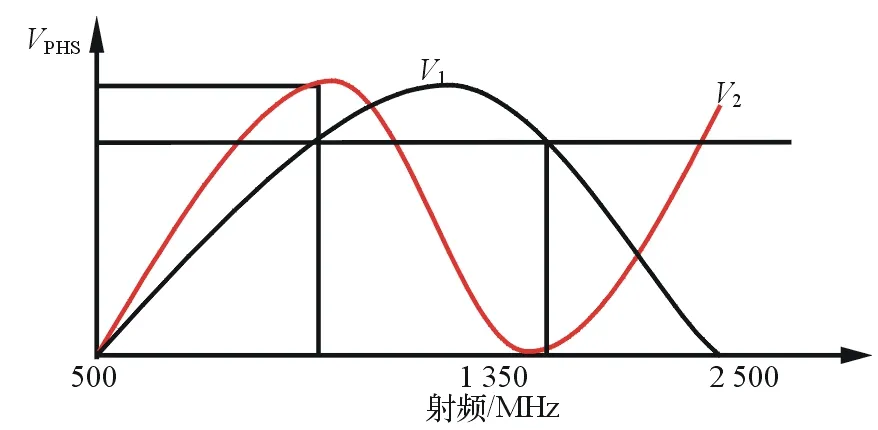

图4 两路解模糊VPHS输出

如图4所示,V1为一通道短延迟线扫频视频输出,V2为二通道长延迟线扫频视频输出。只选取AD8302频段中的500~2 500 MHz,以V1和V2曲线依次分为3个区域,为了保证在这3个区域里不会出现频率编码模糊,必须调整2根延迟线电长度,不能让扫频时的检波视频曲线有倍数关系,如1∶2或者1∶4,因为那将会在不同频率周期性出现相同频率码,从而产生频率模糊。

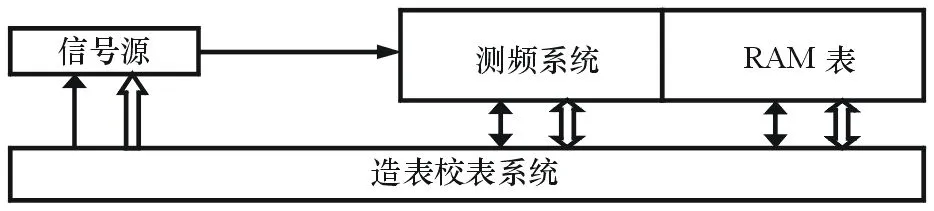

3.2 造表与编码解模糊

频率区域划分是造表与解模糊的前提,频率区域划分好之后如何精测频率并解模糊是工作的重点。图5是自动测试造表系统简图。

图5 造表系统

假设在中频500 MHz,2路ADC采样数据分别为80H和92H,将8092H作为频率码,并存储在根据电路设计设定的固定地址页,产生数据与频率之间的对应关系如表1所示。

表1 真实频率造表关系

从表1可以看出地址码没有出现重复数据,而频率码则是非线性无重复编排,在实际应用中就不会出现频率模糊[3]。

3.3 测频精度和误差分析

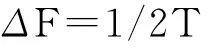

测频不模糊范围:

(1)

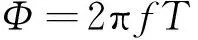

(2)

鉴相器输出相位与输入信号频率的关系:

AD8302的相位分辨率≤1°,则:

测频其理论精度为:

|df |=2 700/360=7.5MHz

考虑到AD8302在 [-π,-160°]∪[160°,π]会出现5°以上的相位误差,因此将频率范围定为500~2 500 MHz是较为合理的。本系统采用2通道解模糊测频,本系统理论测频精度为:

| df |=2 000/720=2.78 MHz

不过为了提高精度,除了造表以外,还可以加入插值算法对频率编码进行补充造表等数据处理手段,实际测频精度将高于理论测频精度。

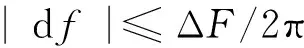

4 多通道测频应用实例

(1) 假设中频带宽为500~2 500 MHz,中心频率1 500 MHz,带宽2 000 MHz,将12~16 GHz分为3个通道:12~14 GHz,14~16 GHz,16~18 GHz,然后以14.5 GHz,16.5 GHz,18.5 GHz本振分别将三通道下变频至500~2 500 MHz,经过放大滤波后进行测频。其基本框图如图6所示。

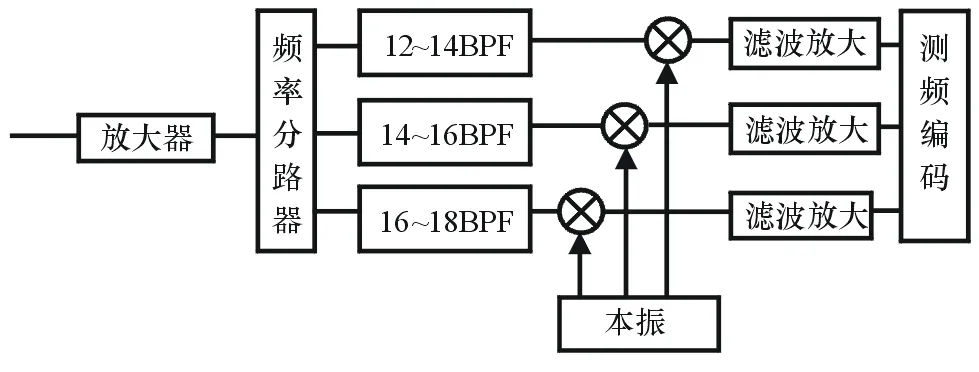

图6 分通道测频基本框图

(2) 对14~16 GHz连续波或脉冲信号测向,以16.5 GHz本振分别将三通道下变频至中频500~2 500 MHz,经过滤波、稳相、限幅放大等处理后,分别利用VPHS和VMAG进行比幅定向计算和比相定向编码,同时或分别以2种方式对辐射目标进行精确定位。其基本框图见图7。

图7 比幅比相基本框图

5 反应时间比较

数字式瞬时测频的反应时间主要由最长延迟线长度、相关器、检波器、差分运算放大器、比较器的延时累加而成。通常瞬时测频的测频精度由最长延迟线决定,因此最长延迟线往往达到数米,其反应时间大约120 ns。

而以AD8302为基础的鉴相系统的反应时间主要来自于延迟线长度、AD8302视频带宽、ADC采样速度、编码电路速度。因为该系统不需要长延迟线来提高精度,因此反应时间将大大减小。

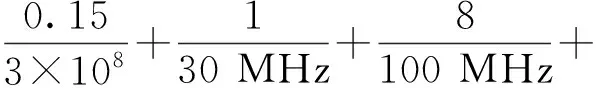

若AD8302测频系统最长延迟线为30 cm,以AD8302视频带宽30 MHz、ADC采样时钟100 MHz、编码板工作频率500 MHz计算,理论系统反应时间为:

而用于定向的鉴相系统,由于通道一致性要求在微波通道反应时间相同。因此系统反应时间主要由通道延迟时间和数字编码时间组成。

若AD8302定向系统射频传输线为15 cm,视频带宽30 MHz,两路ADC采样时钟100 MHz,编码板工作频率500 MHz计算,线阵长度50 cm,入射角45°,则理论系统反应时间为:

6 结束语

AD8302是一款单晶双极性增益鉴相器,设计用来测量2路信号间的增益(插损)和相位差,它将幅度和相位测量集中在一起,省去了原先体积较大的盒体相关器组,使得鉴相系统大大简化。但AD8302也有工作频段窄、频率较低的缺点,如果与小型化频合器一起应用,也能在军事领域发挥一定的作用。它不仅可以用于DIFM,也可以应用于比幅比相测向系统、通讯频段侦察、频率瞄准与反辐射等领域,如果增加频率合成模块还能拓展频段,提高设备的经济性、适用性和可靠性。随着低温共烧陶瓷(LTCC)技术的不断发展,工作频率更高、带宽更大、体积更小的功分器、带状线延迟线、幅相采样芯片也会相继推出,将为新型鉴相系统的宽频化、小型化提供技术支撑。

[1] 赵国庆.雷达对抗原理[M].西安:西安电子科技大学出版社,2005.

[2] 丁鹭飞,耿富录,陈建春.雷达原理[M].北京:电子工业版社,2009.

[3] 程佩清.数字信号处理教程[M].北京:清华大学出版社,2007.

Application of AD8302 to Phase Detection System

TU Zheng-lin,LIU En-kai

(The 723 Institute of CSIC,Yangzhou 225001,China)

This paper introduces the application,design situation and solving ambiguity method of phase detection system in frequency measurement and direction finding system based on AD8302.This design makes the size of phase detection system reduced and the system simplified,so the system can be widely applied to domains such as military,communication and electric power,etc..

phase detection system;solving ambiguity;response time

2016-05-23

TN763.3

B

CN32-1413(2016)04-0113-04

10.16426/j.cnki.jcdzdk.2016.04.025