异步信号的同步化逻辑时序及电路结构研究

2016-11-11刘海成邹海英佟宁宁

刘海成,邹海英,佟宁宁

(黑龙江工程学院 电气与信息工程学院,黑龙江 哈尔滨 150050)

异步信号的同步化逻辑时序及电路结构研究

刘海成,邹海英,佟宁宁

(黑龙江工程学院 电气与信息工程学院,黑龙江 哈尔滨 150050)

为实现异步信号接入同步时序逻辑电路,则需要通过异步信号的同步化电路将异步信号转换为可同步的时序,包括异步信号的采样、“准稳态”问题和异步信号的自动撤销等3个问题。文中给出了解决该问题的电路结构组成、3种同步化时序和5种具体的实现电路,为基于FPGA进行复杂系统设计提供异步信号解决方案。实际测试表明,系统具有稳定性好和结构简单等特点。

异步信号;同步化;时序;电路

人机操作过程,测量仪器的触发信号等都是相对于电子系统同步逻辑的异步输入信号。异步信号和同步时序逻辑电路的同步时钟信号无关,这就涉及异步信号如何与同步时序逻辑电路进行同步,即实现不同时钟域信号的有效传递。

比如地铁的自助售票等投币式交互系统,投币信号就是异步信号,且这些异步信号的特点是“仅有效一次”,即不但要正确响应,还不能多次响应。也就是说,投币信号产生的高电平持续时间要大于同步时序电路状态转换时钟周期,以保证在状态时钟的有效边沿时其处于高电平,同时也会出现一次投币信号被多次状态转换时钟捕捉的问题,投币信号作为有效的确认信号后要被即刻自动清除,否则会被同步时序逻辑电路“误解”为又有硬币投入。本文针对该问题,深入研究了异步信号的同步化逻辑时序及电路结构[1-2]。

1 异步信号的同步化逻辑结构及时序

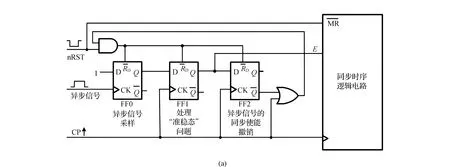

假定异步信号的性质为高脉冲,“异步信号作为单次同步使能信号”,需要一个采样触发器(上升沿触发)即刻记忆已经出现一次异步信号,如图1所示中的FF0。一般是触发器由“0”变为“1”表示异步信号有效,辅助时序逻辑电路据FF0的Q产生用于同步时序逻辑电路的同步使能信号E(高有效),在此后出现一次有效的同步时钟边沿后,触发器FF0和信号E在下次有效同步时钟边沿到来之前自动被清除(由“1”变为“0”)[3]。

图1 异步信号作为单次同步使能信号的电路结构

但强调的是,FF0的输出不能直接作为E,这是因为异步信号的起始沿经采样触发器产生的请求信号还是异步信号,FF0在这里的作用有两个:一是为了防止异步信号过短,用FF0记忆有异步信号;二是为了防止异步信号过长,解决异步请求信号高电平时间超过同步时钟周期而形成一次异步请求多次响应的问题。若采样触发器的输出直接作为E,则有可能出现同步时钟的上升沿与异步请求信号的上升沿极其临近的情况,不满足建立时间和保持时间的条件,也就无法确定采样触发器的输出是否为高电平,这种情况称为准稳态,必须进行同步化和二次确认。因此,异步信号作为单次同步使能信号的逻辑转换共涉及3个问题:异步信号的采样、“准稳态”问题和E的自动撤销问题。为解决这3个问题,同步时钟CP(假定为上升沿有效)与E的时序关系共有3种,如图2所示。可以看出,E的起始沿(上升沿)与异步信号的起始沿不是对齐的,也就是没有发生准稳态。若出现准稳态,则E将可能被推迟1个同步时钟周期。

图2(a)中,同步后的信号E高脉冲的宽带等于同步时钟的周期,应用信号E的有效同步时钟边沿发生在E信号高脉冲的中间时刻;图2(b)中,同步后的信号E高脉冲的宽带也等于同步时钟的周期,应用信号E的有效同步时钟边沿发生在E信号高脉冲的结束时刻;图2(c)中,同步后的信号E高脉冲的宽带大于同步时钟的周期,但其间仅有一个有效的同步时钟边沿。

图2 异步信号作为单次同步使能信号的时序

2 异步信号的同步化电路

本文给出5个电路来实现异步信号作为单次同步使能信号的逻辑转换,每个电路都包含异步信号采样、处理“准稳态”问题和E的自动撤销电路3个部分。3种时序关系在功能上是等价的,显然5种电路在功能上也是等价的。

2.1基于时序1的异步信号作为单次同步使能信号的逻辑转换电路

本文给出两个基于时序1的异步信号作为单次同步使能信号的逻辑转换电路。

2.1.1电路1

2.1.2电路2

某时刻异步信号出现,同样,其上升沿促使FF0对异步信号取样一次,并输出高电平。此后,在CP的下降沿,且FF1处于非准稳态时,同步使能信号E有效(变为高电平),E在接续的CP上降沿被同步利用,FF0也被即刻异步清零,此后在接续的CP下降沿FF1自动被同步清零,回到异步信号有效之前的状态。

图3 异步信号作为单次同步使能信号的电路(图2(a)时序)

图4 异步信号作为单次同步使能信号的电路(图2(a)时序)

2.2基于时序2的异步信号作为单次同步使能信号的逻辑转换电路

图5 异步信号作为单次同步使能信号的电路(图2(b)时序)

2.3基于时序3的异步信号作为单次同步使能信号的逻辑转换电路

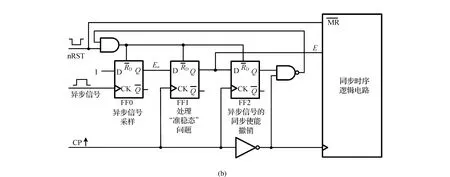

本文给出两个基于时序3的异步信号作为单次同步使能信号的逻辑转换电路。

2.3.1电路1

2.3.2电路2

如图6(b)所示电路,工作过程同图6(a)所示电路,只是组合逻辑略有差异,这里不再赘述。

图6 异步信号作为单次同步使能信号的电路(图2(c)时序)

3 结束语

本文从异步信号的同步化需求入手剖析了相关问题,并给出了解决该问题的电路结构组成、3种同步化时序和5种具体的实现电路,实现了异步电路与同步电路的分离设计及协同工作。以上方法在多个具体项目中应用,系统可靠运行,成效明显。

[1]秦进平.数字电子与EDA技术[M].北京:中国电力出版社,2013:160-165.

[2]唐昌凡,段金蓉.时序逻辑电路的次态卡诺图分析法[J].四川师范学院学报(自然科学版),1999,20(3)273-277.

[3]蒲石.异步多时钟域系统的同步设计研究[D].西安:西安电子科技大学,2007.

[4]张继军.同步和异步时序逻辑电路统一设计的新方法[J].计算机工程与应用.2003(17):136-138.

[5]唐志兴.时序逻辑电路的矩阵分析法[J].西南师范大学学报(自然科学版),2001,26(6):684-688.

[6]张海泉,张燕林.时序逻辑电路中的竞争冒险[J].河南教育学院学报(自然科学版),2004,13(2):34-35 .

[7]高美蓉.基于时序图的异步时序逻辑电路的设计[J].新技术新工艺,2016(2):37-39.

[8]谢春茂.同步时序逻辑电路设计的新方法[J].西华师范大学学报(自然科学版),2008,29(2):204-207.

[9]喻桂兰.一种分析时序逻辑电路的补充方法[J].现代计算机(专业版),2012(28):7-10.

[10]李彩.浅谈时序逻辑电路[J].科技视界,2013(3):38.

[11]徐永谦,万延.时序逻辑电路的设计方法分析[J].科技创新导报,2008(10):61-62.

[12]黄晓明.脉冲异步时序逻辑电路的分析与设计探讨[J].湖北教育学院学报,2005,22(5):47-49.

[13]李德明.异步时序逻辑电路中的竞争现象[J].中州大学学报(综合版),1994(1):43-47.

[14]刘海成,秦进平,邢传军,等.基于次态输出的FSM设计及异步转换条件采样研究[J].黑龙江工程学院学报,2014,28(4):38-42.

[15]万敏.异步时序电路中的亚稳态设计与分析[D].上海:上海交通大学,2008.

[责任编辑:刘文霞]

Research on synchronous logic sequence and circuit structureof asynchronous signals

LIU Haicheng,ZOU Haiying,TONG Ningning

(College of Electrical and Information Engineering,Heilongjiang Institute of Technology,Harbin 150050,China)

The realization of asynchronous signals accessed by synchronized sequential logic circuits,needs asynchronous signal conversion for synchronization timing through the synchronization circuit of asynchronous signal,including three parts: asynchronous signal sampling,“quasi steady” and asynchronous signal automatic revocation.This paper gives a circuit structure,three kinds of synchronization time series and five kinds of realization circuit to provide asynchronous signal solution for complex system design based on FPGA.The tests show this system servers stable and simplified in its structure.

asynchronous signals;synchronization;sequential; circuit

10.19352/j.cnki.issn1671-4679.2016.05.011

2016-05-24

黑龙江省教育厅科学技术研究项目(12541673)

刘海成(1979-),男,副教授,研究方向:信号处理与嵌入式系统应用.

TM131.5

A

1671-4679(2016)05-0038-05