C波段微波锁相环频率合成器的设计与仿真

2016-11-10张瑞成李玉红

张瑞成,李玉红

(华北理工大学电气工程学院,河北唐山,063009)

C波段微波锁相环频率合成器的设计与仿真

张瑞成,李玉红

(华北理工大学电气工程学院,河北唐山,063009)

随着高频技术的发展,微波能量传输系统中常采用更高的频率,为了整流天线能得到高输出电压,并且减小系统体积,降低装置成本,设计了一种C波段微波微波锁相环频率合成器。通过以ADF4106作为核心电路,选用合适的压控振荡器芯片,确定鉴相频率、分频系数,并且详细分析了环路滤波器结构及其参数,并利用仿真软件对锁相环仿真,得到的仿真参数与计算结果基本一致。该系统具有极高的工作频率,省略了许多高频系统中的倍频部分,简化了系统的结构,降低了装置的成本。

C波段;锁相环;频率合成;ADF4106

0 引言

随着科学的不断发展,微波无线输能成为当前科学研究中一个既有难度,又相当热门的方向。微波无线电能传输对于微小型机器人、卫星等能量传输以及解决地面复杂环境的电能输送等问题有着重要意义。在利用微波实现无线输电的系统中,微波频率合成是微波无线输能系统发射端重要的研究部分。

目前,在微波频率合成中锁相环技术得到广泛应用,但因器件工作频率的限制,锁相频率合成需要采用倍频、分频、滤波等频率变换和组合,从而产生各种干扰。文献[3]介绍了一种基于ADF4113的锁相环频率合成模块,由于锁相芯片的频率限制,其最后输出频率为1GHz,无法满足现在对高频的要求;文献[4][5]详细分析了各种锁相环环路滤波器的结构和参数,但并未考虑压控振荡器、鉴相器等其他部分的参数。因此本文以ADF4106作为核心电路,选用集成VCO芯片V940ME30作为外部压控振荡器,设计相应的环路滤波器,构成锁相式频率合成器,产生C波段的微波信号,并且要求相位噪声低,频率稳定度高同时转换时间较快。该系统具有极高的工作频率,省略了许多高频系统中的倍频部分,简化了系统的结构,降低了装置的成本。

1 锁相环的基本组成与原理

1.1锁相环的组成及工作原理

锁相技术是一种相位负反馈技术,通过比较输入信号和VCO输出信号的相位,选用与两个信号相位差成正比的电压作为误差电压,利用这个误差电压来控制振荡器的频率从而达到使其与输入信号频率相等的目的。

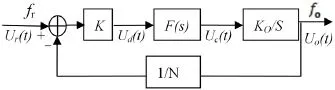

锁相环系统的模型由鉴相器(PDF)、环路滤波器(LPF)、压控振荡器(VCO)以及分频器组成,结构如图所示:

图1 锁相环结构图

当环路锁定时,通过鉴相器的两个信号频率相等,相位差也不再变化,此时的误差电压固定,输入信号频率与VCO输出频率相等,所以锁相输出频率为

其中, N和R主分频器和参考分频器的分频比,fo为输出频率,fi为参考频率,一般是由频率极稳的晶振提供。在实际应用中,可以通过调整N和R的值,从而获得需要的输出频率。其鉴相频率为

1.2锁相环的数学模型

将锁相环每一部分用恒定的增益或者频率函数的增益值表述, 得到其数学模型如图所示

图2 锁相环数学模型图

通过计算误差电压Ud和输出电压UO的关系,可以得到负反馈系统的闭合回路增益的表达式为:

所以系统闭环传递函数为

开环传递函数为

2 系统方案的设计与仿真

在微波无线电能传输系统中,稳定,高质量的微波信号对于能量的传输有着重要影响,所以发射端需要一个稳定的振荡源。以ADF4106为核心,选择合适的外部压控振荡器,设计相应的环路滤波器,即可构成低噪声,高稳定度的微波信号。

2.1方案设计

本方案选取ADI公司生产的锁相环芯片ADF4106,该芯片最大特点就是它具有极高的工作频率,最高可达6GHz。用其设计的锁相环路具有很高的带宽,从而在高频系统中省去了倍频器,消除了由倍频器所带来的谐波、杂波及噪声干扰,有利于提高系统性能,简化系统结构,从而降低了功耗和设备成本。选用高稳定度有源晶振为芯片提供20MHz的参考频率,并且经过50Ω的匹配电阻后连接到锁相环芯片的输入端。因ADF4106内部参考分频器R=10,由公式(2)得到鉴相频率为2MHz。压控振荡选用集成VCO芯片V940ME30,其工作频率为5500MHz~5850MHz, 调谐灵敏度为80MHz/V,供电简单仅需5V,并且该芯片具有很好的谐波抑制以及较好的线性度。

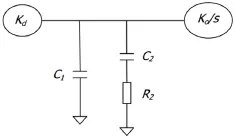

环路滤波器是锁相环电路中的重要组成部分,设计滤波器的一种方法就是采用开环增益带宽和相位裕量决定相应器件的值。相位裕量通常在30~70度,本设计中选取45度,而环路带宽一般选择为鉴相频率的10%。考虑信号的杂散和锁定时间,环路带宽的选择一般为鉴相频率的1/10,所以环路带宽为200KHz。为了确保环路的稳定,在开环响应单位增益频率处定位最小相位移点。为了降低相位噪声,使用无源环路滤波器,其中二阶环路滤波器是较为简单的形式如图3所示。

图3 环路滤波器

由以上公式可得:

其中,时间常量t1和t2决定滤波器传递函数频率的零点和极点。相位裕量与系统的稳定性有很大关系,该频率处相位裕量的计算公式为:

由上式可以求的

把(12)式代入(10)式中,由此可以求得相位裕度最大值:

化简得:

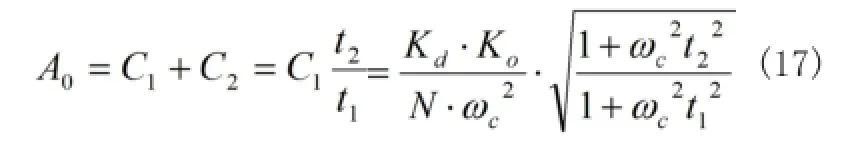

根据该锁相环的开环传递函数(6)式和(8)式以及环路带宽的定义可以得出环路滤波器总的电容A0,即:

因此,其他元件的值也就很容易得出了:

联合(5),(6),(18),(19),(20)式,把器件参数设计条件代入就可求的符合设计要求的滤波器的参数值。计算的:C1=31.8Pf,C2=207.8pF, R2=10.49K。

2.2锁相环电路仿真与分析

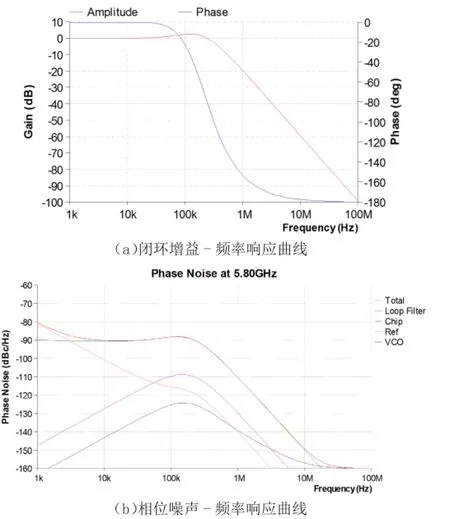

锁相环电路利用仿真软件ADIsimpll进行仿真,根据以上分析选择芯片ADF4106,确定输出频率为5.8GHz,鉴相频率为2MHz;选择二阶无源环路滤波器,并设置参数相位裕量为45度,环路带宽为200KHz;压控振荡器灵敏度KO=80MHz/V,则由公式(1)知主分频器N=f0/fr=5800/2=2900。对锁相环进行仿真后得到电路原理图如图4所示,由图可以看出环路滤波器仿真得到的参数值与计算出的参数值基本一致。

锁相环时域、频域曲线图如图5、图6 所示,其中图5为频率-时间曲线图,环路滤波器输出相位误差-时间曲线图,图6分别为闭环增益与相位噪声曲线

图4 锁相环仿真电路图

图5 环路滤波器时域仿真图

3 结论

本文分析了锁相环频率合成的结构模型,介绍了一种C波段微波锁相环频率合成器的设计。

图6 环路滤波器频域仿真图

(1)利用ADF4106为核心芯片,微波频率能够直接达到5.8GHz,省略了倍频部分,精简了电路结构;

(2)确定VCO芯片、外部晶振以及环路滤波器的结构,得到鉴相频率、环路带宽、相位裕度等参数值,并且详细分析了环路滤波器各个参数的值。

(3)利用仿真软件对锁相环进行仿真,得到的仿真参数与计算结果基本一致,并且锁相环能够快速锁定,噪声较小,性能优异。

[1] Naoki Shinohara.Power without wires[J].IEEE Microwave Magazine,2011,(9):64-70.

[2] J.O.Mcspadden,J.C.Mankins. Space solar power programs and microwave wireless power transmission technology[J].IEEE Microwave Mag.2002, (9)46-57.

[3]汪海燕.基于ADF4113的锁相环频率合成PLL模块设计[J].安徽电子信息职业技术学院学报,2015,(1):14-16.

[4]方明志,佘世刚,周毅,等.锁相环有源滤波器设计及其参考杂散的影响[J].现代电子技术,2014,(9):73-76.

[5]张涛,陈亮.电荷泵锁相环环路滤波器参数设计与分析[J].现代电子技术,2008,(9):87-90.

[6]袁浩,宁媛,崔陆月.集成电路中高速锁相环的研究[J]. 现代机械,2014,(6):61-65.

[7] 潘焱, 田华, 魏安全.无线通信系统与技术[M]. 北京:人民邮电出版社,2011.3.

[8] 高立俊.基于ADIsimPLL 3.1的锁相环环路滤波器设计[J].现代电子技术,2013,(15):56-58.

Design and simulation of C band microwave phase locked loop frequency synthesizer

Zhang Ruicheng,Li Yuhong

(College of Electrical Engineering,North China University of Science and Technology,Tangshan Hebei,063009)

With the development of high frequency technology, microwave energy transmission systems are often used in higher frequency.In order to rectifying antenna can get high output voltage,reducing the system volume and reducing the cost of the device,a C-band microwave phase-locked loop frequency synthesizer is designed.Through to ADF4106 as a core circuit,choose suitable pressure controlled oscillator chip,determine Phase discrimination frequency,frequency division coefficient,loop filter structure and parameters,and the phase lock loop(PLL)is simulated,the related loop parameters and algorithms for computing results are basically the same.The system has a very high operating frequency, omitted many of the frequency doubling of the high frequency system,simplifying the structure of the system and reducing the cost of the device.

C Band;phase locked loop;frequency synthesizer;ADF4106

张瑞成(1975-),男,河北唐山,教授,博士,主要研究方向:电力系统分析。

李玉红(1991-),女,河北唐山,硕士研究生,主要研究方向:无线电能传输.