时间测量电路系统的设计*

2016-11-01赵建军高霞芳唐海峰

赵 恩,赵建军,高霞芳,唐海峰,方 钊

(昆明理工大学 理学院,云南 昆明 650500)

时间测量电路系统的设计*

赵恩,赵建军,高霞芳,唐海峰,方钊

(昆明理工大学 理学院,云南 昆明 650500)

研究设计了一种基于FPGA(Field Programmable Gate Array)技术设计的时间数字转换电路,其具有将多通道时间信号转化为数字信号,数据缓存处理,以及多通道数据组合输出的功能。采用FPGA技术,利用Xilinx公司Virtex II Pro系列芯片XC2VP30-FF896,采用粗时间和细时间相结合的计数计算方法设计时间数字转换电路模块。采用状态机设计的方法,利用FIFO管道实现准确有效地传输数据,解决了多通道传输所带来的数据重复的问题。该时间测量电路系统的设计具有精度高、成本低和应用领域广泛等特点。

时间数字转换电路;通信协议;先进先出;状态机

1 基于FPGA的时间测量电路系统设计

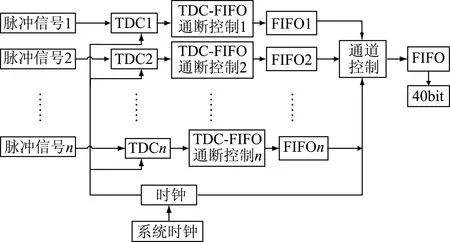

时间是高能物理实验中的一个重要测量参数。目前,时间的测量方法主要有2种:1)采用专用的时间测量芯片(ASIC TDC);2)采用基于FPGA的时间数字转换(Time Digital Converter,TDC)[1]电路。专用的时间测量芯片大多都是针对具体的应用而开发的,对于设计的灵活性、普遍性存在一定的不足,并且其开发周期相对较长。本文采用FPGA技术,利用Xilinx公司Virtex II Pro系列芯片XC2VP30-FF896,封装为ff896。时间测量电路包括TDC电路、TDC数据存入FIFO的通断控制模块、FIFO缓存模块和多路通道控制模块,最终形成40位的时间测量数据。时间测量电路的构成示意图如图1所示。

图1 时间测量电路的构成示意图

2 TDC电路的设计

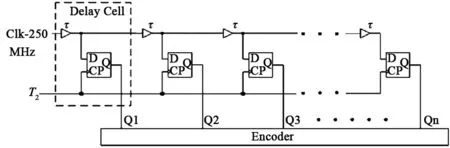

TDC模块采用粗时间和细时间计数相结合的计算方法。秒以上的时间计数为粗时间计数,秒以下的计数精度为细时间计数。对于粗时间的测量,采用二进制计数器的方法来实现,由时钟模块产生,该测量方法已经比较成熟,计数长度从秒到年,实现秒、分、时、日、月和年的计数。对于细时间的测量[2],4 ns至秒以上的计数精度通过调用DCM(时钟数字管理模块),将系统时钟进行倍频提高计数频率;4 ns以下至皮秒以上的精度采用时间内插法进行设计,并经过格雷码编码,在保证计数准确度和精度的同时,减少了对FPGA资源的占用率,提高了数据处理的效率。对于倍频的设计,利用Xilinx公司的ISE14.7软件工具,采用系统时钟倍频的方式,添加带有倍频功能的IP核,将Virtex II Pro开发板的系统时钟频率从100 MHz通过DCM倍频到250 MHz。为了进一步提高细时间计数的精度,4 ns以下的时间计数采用内插法设计。时间内插技术通过在时钟周期T内插入多个延时单元实现更高的时间分辨率[3]。延迟单元的延迟线通过调用FPGA中的逻辑单元Slice内的原件实现,通过半手动半自动的方式对底层的原件布局布线进行编辑来实现,并将细时间在最短的时间锁存,以提高数据的准确性。内插技术的结构框图如图2所示,包括查找表、触发器、多路选择器和进位链等元件。

图2 内插技术的结构框图

3 FIFO数据缓存模块

在FIFO的工作过程中,数据的写入和读出是按顺序进行的,一旦给其上电,写读指针都指向第1个存储单元,每当收到写读指令时,写读指针都加1,当写读指针指向存储器最后一个单元时,写读指针又回到初始位置,形成环形地址[4]。FIFO缓存分为同步和异步等2种,用于解决不同的系统数据传输速率不匹配的问题,本设计采用异步FIFO。异步FIFO作为一个缓冲存储器,将数据在2个不同的时钟间进行交换,能够顺序存储连续的数据,之后按照先进先出的原则输出这些数据;因此在雷达、数据通信、图像处理及多媒体技术等方面有着很广泛的应用[5]。

本文将FIFO数据缓存模块设计分为2类:1)多通道的支路FIFOi的设计,用于缓存时间数字电路TDC生成的细时间数据;2)总FIFO的设计,用于存储合并后的粗细时间,存储形成总的TDC数据。具体方法是利用Xilinx公司的ISE14.7软件工具,添加IP核,生成异步FIFO,产生TDC数据的多通道FIFOi的缓存模块以及总FIFO的缓存模块。TDC产生的时间-数字信号写入到总FIFO时的数据模块如图3所示。

图3 总FIFO的数据格式

4 TDC数据写入FIFOi通断控制的设计

由于通道FIFOi的写入周期小于TDC模块产生数据的周期,那么在TDC还没有产生新数据之前,该通道会不停地读取原数据,造成数据的重复写入。TDC-FIFO通断控制模块可以控制TDC所产生的数据不会重复地写入通道FIFOi。通断控制模块的设计原理是利用数据比较器,对通道内的数据和TDC模块产生的数据进行比较,通过控制FIFOi的写使能,当数据相同时停止写入,否则写入FIFOi有效数据。

5 通道控制模块

支路FIFOi-控制模块-总FIFO的原理图如图4所示。通道控制模块控制FIFOi的支路数据正确地写入总FIFO,每隔1 s向总FIFO中写入1次粗时间数据,当有新的细时间数据产生时,通道控制模块控制细时间的插入,将细时间数据写入总FIFO,和粗时间数据进行合并,产生40位的时间数字数据。利用FPGA技术设计通道控制模块的状态机FSM如图5所示。

图4 支路FIFOi-控制模块-总FIFO的原理图

在图5中,S0状态是指当复位脉冲信号到来时,将电路整个设计系统进行复位;S1状态是指当TDC模块没有产生细时间和粗时间时,状态机进入空闲等待的状态;S2状态是指当有细时间到来时,令支路FIFOi的读使能有效,令总FIFO的写使能有效,将TDC产生的时间-数字信号写入总FIFO缓存中;S3状态是指当有时间-数字信号的粗时间数据到来时,令支路FIFOi的读使能无效,停止数据从支路FIFOi向总FIFO的写入,令总FIFO的写使能有效,将TDC产生的粗时间数据写入总FIFO。

6 总结

本文设计了一个基于FPGA技术的高精度时间测量电路系统,提出了TDC的具体设计方案和多通道数据的组合输出。解决了多通道传输所带来的数据重复的问题,使整个系统具有数据采集精度高、编程设计灵活和传输可靠的优点。

[1] 范欢欢.基于FPGA的时间数字转换电路的若干关键技术的研究[D]. 合肥:中国科学技术大学,2015.

[2] 唐海峰,赵建军,吴光敏,等. 基于FPGA的皮秒计数设计[J]. 新技术新工艺,2016(1):40-42.

[3] 张敏. 皮秒分辨率的FPGA-TDC技术研究[D].西安:西安电子科技大学,2013.

[4] 李东,赵志凯.一种高性能异步FIFO的设计与实现[J].微电子学与计算机,2010,27(8):145-148.

[5] Elrabaa M E S. A new FIFO for transferring data between two unrelated clock domains[J]. International Journal of Electronics, 2012, 99(8):1063-1074.

*国家自然科学基金青年科学基金资助项目(11103069)

责任编辑郑练

Time Measurement Circuit System Design

ZHAO En, ZHAO Jianjun, GAO Xiafang, TANG Haifeng, FANG Zhao

(Kunming University of Science and Technology, Kunming 650500, China)

Study and design a time measurement circuit based on FPGA (Field Programmable Gate Array) technology, its function includes: and use a multi-channel time signal can be converted to digital signals, data cache handling, and the combination of multi-channel data output. Use FPGA technology with Xilinx company Virtex II Pro series chips XC2VP30-FF896, and use coarse time and fine time of phase counting method to calculate the TDC module design. The transmission methods use state machine design method with FIFO pipe to realize the accurate and effective data transmission, solve the multi-channel transmission data brought by the repeated problems. The time measurement circuit system design is with high precision, low cost, application field widely and so on.

TDC, communication protocol, FIFO, state machine

TN 06

A

赵恩(1991-),女,硕士研究生,主要从事嵌入式系统等方面的研究。

赵建军

2016-04-28