HVNMOS 管的工艺参数分析

2016-10-29贺雪群

贺雪群

(厦门理挚半导体科技有限公司,福建 厦门 361008)

工程技术

HVNMOS 管的工艺参数分析

贺雪群

(厦门理挚半导体科技有限公司,福建厦门361008)

以测试数据分析了CMOS工艺下影响高压N管HVNMOS耐压值的几个参数。

高压N管;工艺参数;耐压值

在电路设计中,即使是低压的设计,也难免要应用到高压部分,但又不能改变工艺,在这种情况下,高压管应用而生。下面我们以HVNMOS为例子来具体分析。

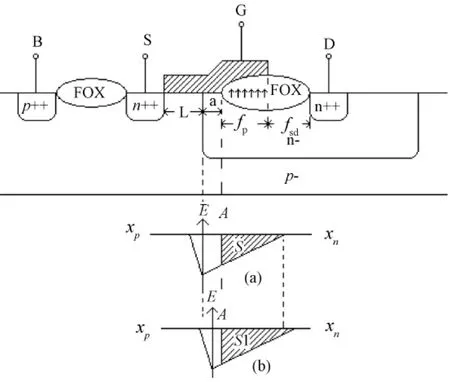

在高压管中,我们就是要保证D端所加的高压经过场释放到大G端下面后小于栅穿电压。图1是一个CMOS工艺下HVNMOS的剖面图[1],也就是在A点时,要保证VD-VG<V栅穿。D端是一个低搀杂的N-区,与G端有一定的交叠量。总的D、S电压VDS等于两个三角形的面积之和:

图1 HVNMOS晶体管剖面图及漏端横向电场示意图

D端N-与G端交叠量,即a的大小,不可太小,也不可太大。既要考虑在有套版偏差的情况下管子能正常工作,又要尽量提高管子的工作电压。VD=VDS-V阴影,从上面两个图可以看出,如果适当缩小a的值,D端在A点的电压会降低。

影响耐压值的参数有:1)poly1gate覆盖在场氧FOX即场板的值fp;2)fp到D端高浓接触区的space,即HVNMOS剖面图上的fsd(fpspacedrain);3)沟道长度L。

在测试中,以某工艺为例,做了一系列的图形,在其他参数不便的情况下,分别改变以上三个参数,然后测试击穿电压。具体的测试方法为:S、B、G短接并接-20V电压,D端电压从-20V到40V、步进0.2 V的加压,检测D端电流Id、b端电流Ib,s端电流Is,若出现击穿使Id、Ib任意一个突然增大的情况,停止扫描。

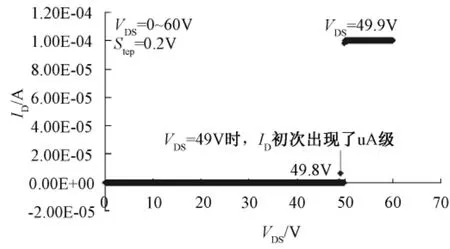

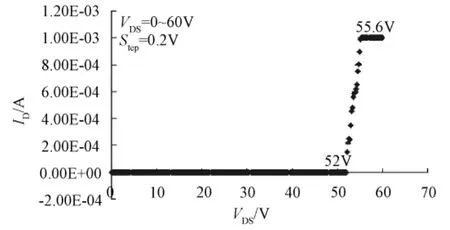

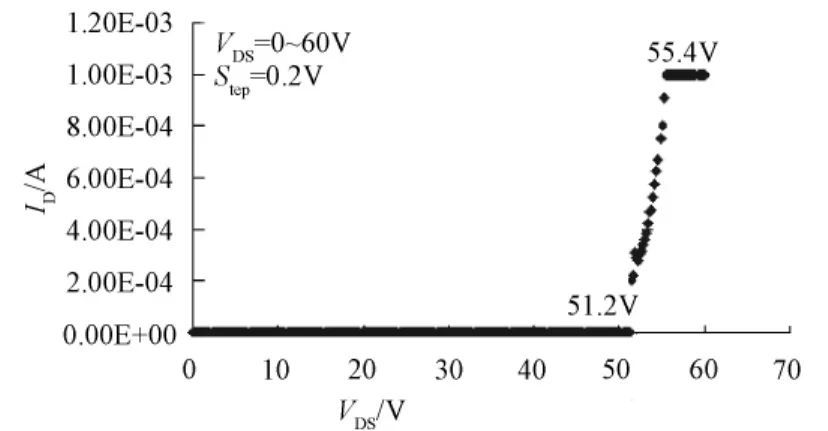

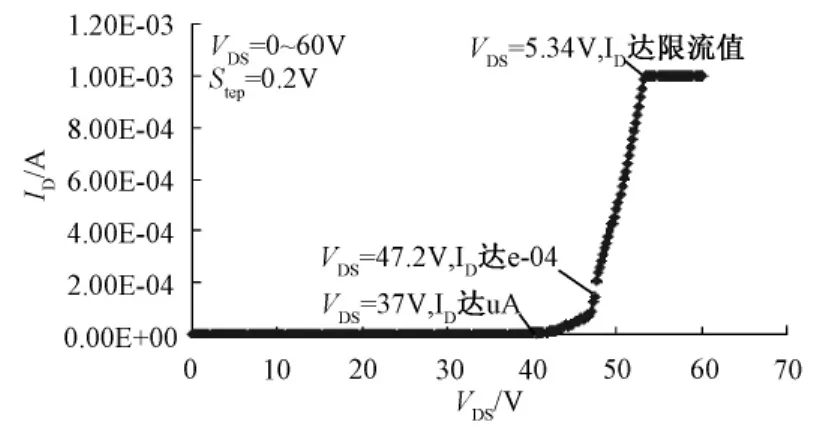

1)fp的改变对击穿电压的影响:W/L=40/4,m=2,fsd=3.0 um,fp分别取0.8um、1.2um、1.6um,得到的击穿图分别如图2—图4。

总结:从击穿曲线看,所有的击穿都属于次表面击穿,且击穿发生后直至测试所加的最高电压60V,栅极都没有电流,可见场板起到了两个作用:将击穿压在次表面并保护栅氧不被击穿。三个图形的耐压值分别为46.6V、48.2V、48.9V,有上升的趋势,可见击穿部位的深度在逐渐的增加。从测试数据看,击穿都是发生在n-/p-之间。

图2 Fp=08u m的击穿图

图3 Fp=1.2μm的击穿图

图4 Fp=1.6μm的击穿图

2)fsd对耐压值的影响:W/L=40/4,m=2,fp= 2.0u,fsd分别取0.4μm、0.8μm、1.2μm、1.6μm、2.0μm、3.0μm,得到的击穿图分别如图5—10。

图5 fsd=0.4μm的击穿图

图6 fsd=0.8μm的击穿图

图7 fsd=1.2μm的击穿图

图8 fsd=1.6μm的击穿图

图9 Fsd=2.0μm的击穿图

图10 Fsd=3.0μm的击穿图

总结:从理论上分析,如果fsd太小的话,管子则会因d与fp之间的电场太大而造成击穿。从测试得到的击穿曲线来看,fsd的改变对耐压值的影响并不大。从电压的角度来看,除fsd=1.6μm之外的5个图形,耐压值在51V和52V两个点上徘徊,管子达到限流值时的电压值也基本相同;从得到的击穿曲线来看,除第4组外,其余5个曲线基本上相似。4组的击穿曲线很漂亮,d端加到一定的电压后管子立即就被击穿了。

3)L值对耐压值的影响:W/L=10,m=2,fsp=3.0,fp=2.0,L分别取1.5μm、2.0μm、2.5μm,得到的击穿图分别如图11~13。

图11 L=15u/1.5μm的击穿图

除L=1.5μm时,管子在VDS=37V时就发生了d/s穿通之外,其余的都是d/b次表面击穿。在设计高压管的L时,要考虑到结的耗尽和横扩,不能太小。

图12 L=20u/2.0μm的击穿图

上面讨论的是单边HVNMOS,只有D端可耐高压,如果要双边耐高压,则S端结构也要与D端相同。

图13 L=2.5μm的击穿图

[1](美)黑斯廷斯.模拟电路版图的艺术[M].北京:电子工业出版社,2007:416.

(编辑:刘楠)

HV MOSTransistor Parameters Analysis

He Xuequn

(Xiamen Lizhi Sem iconductor Technology Co.,L td.,Xiamen Fujian 361008)

This paper analyzes the impact of test data under high voltage CMOS process N HVNMOS tube voltage value of several parameters.

high pressure pipe parameters N;technological parameter;withstandingvoltage

TN141.1+6

A

2095-0748(2016)11-0040-03

10.16525/j.cnki.14-1362/n.2016.11.17

2016-04-25

贺雪群(1978—),男,湖南南县人,本科,工程师,从事IC版图设计工作,对工艺以及电路均有研究。