一种分布式时钟同步系统设计

2016-10-26赵永发

赵永发,周 磊

(扬州大学 信息工程学院,江苏 扬州 225000)

一种分布式时钟同步系统设计

赵永发,周磊

(扬州大学 信息工程学院,江苏 扬州 225000)

分布式时钟同步系统是分布式系统协同工作的基础,在时间同步技术基础上,设计了一种分布式时钟同步系统。该系统以IRIG-B(InterRange Instrumentation Group)时间基准信号为时间同步源,不仅可以为机器提供高精度时钟信号,在一段时间内保持高精度,而且可以以较小的体积嵌入到产品中,提高便捷性。实验结果表明,该系统可以为机器在不同温度条件下提供高精度时钟信号,而且具有较高的时钟稳定度。

分布式时间同步;时间守时;时钟稳定度;恒温晶体

0 引言

随着信息技术的不断发展,对信息采集的速度和精度要求越来越高,机器之间的时钟同步要求也越来越高。因此,分布式时钟同步系统应运而生,该系统可以协调分布式网络中的节点时间,为网络中的节点提供准确时钟。但是由于分布式网络环境的复杂性,时钟本身温漂、网络延时和成本因素等影响,系统有时不能为机器长时间提供高精度的时钟。因此,设计高精度、稳定、低成本的同步系统是必要的。

目前,时钟同步主要有2类方法,一类方法是通过Network Time Protocol(NTP)服务器来提供时间信息,如文献[1-7]中都采用了网络时间来同步机器的时间,再通过补偿算法来矫正网络时间,以此来减少网络延时误差。但是,此方法得到的时间因为线路长短,电脑时间分辨率和环境等原因,误差有随机性,同步精度只能达到几十ms左右,对于实时性同步性很高的信息采集机器来说精度是不够的。而且机器必须接入网络才可以得到时间,这也大大限制了机器使用的范围。另一类方法是通过解析GPS(Global Positioning System)的时间信息,来实时同步机器时间,GPS可以提供精度很高的时间信息,可以达到ns级别。通过解析GPS的时钟同步系统精度也可以达到μs级别,如文献[8-12]都是先通过同步GPS的时间信息来产生对应的时间码,再使用时间码来同步机器时钟。这样可以得到高精度的时间信息,但是随着机器数量的增加,使用此方法每一台机器必须配备一台GPS时间同步机器产生时间码,成本大大增加。由于机器使用的流动性,GPS时间同步机器需要一起移动,但是必须是可以接收到GPS信号的地方,这样又限制了机器的使用,机器的便捷性减弱。

为解决以上问题,本文从第2类方法思路出发,通过同步GPS源的基准时间信号,得到高精度的时间信号。为提高便捷性和降低成本,提出了一种同步GPS源的IRIG-B码的方法。在此方法的基础上使用FPGA器件,51单片机和恒温晶体完成了多机器时间同步系统的硬件实现。该系统可以以很小的体积和较低的成本嵌入到产品中,为机器提供同步时钟源,从而达到在便捷性的基础上提高精度且降低成本的目的。

1 系统设计原理

系统接收IRIG-B时钟信号来同步时间。时钟同步系统同步之后需要进入守时状态,守时状态影响时钟精度的因素主要是本地时钟的精度,首先本地时钟精度需要满足要求。

1.1时钟误差分析

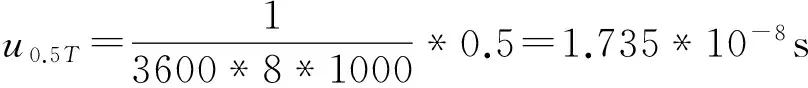

时钟同步系统要在系统同步完成后保持精度,首先系统内部时钟源精度需要满足要求。同步GPS时间同步系统的IRIG-B码为几十ns的误差,误差可以忽略。同步时钟按照1 kHz输出、连续工作8h、误差不大于0.5个时钟周期计算,时钟输出精度为:

(1)

式(1)的时间误差为一个时钟周期的误差要小于3.47*10-8s,机器信息采集一般误差要小于0.5个时钟周期,那么误差为:

(2)

现采用JKOC36-25.6M型号的恒温晶体,标称频率为 25.6MHz,工作温度为-40℃~70℃,在此范围内,它的短期频率稳定度优于 5E-12(阿伦方差),频率温度稳定度<±5ppb(不带隐含参考温度,ppb为10-9),日老化<±0.5ppb,年老化<±0.05ppm。工作电压为 5V,输出方波,高电平为 2.85V,低电平为 0.25V,占空比为 45%~55%。短期稳定度可以满足要求,现主要考虑频率温度稳定度:

u温度=5*10-9s,

(3)

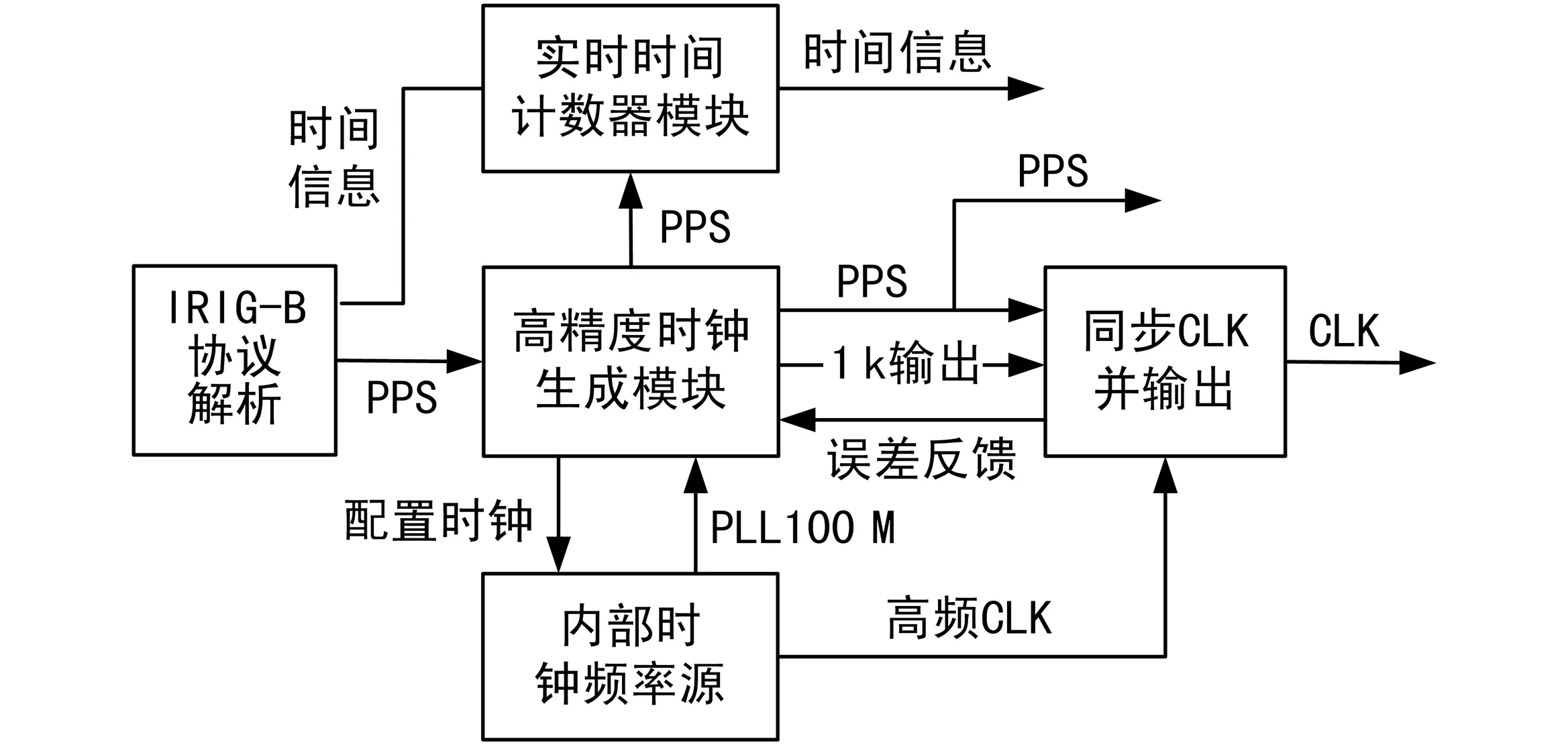

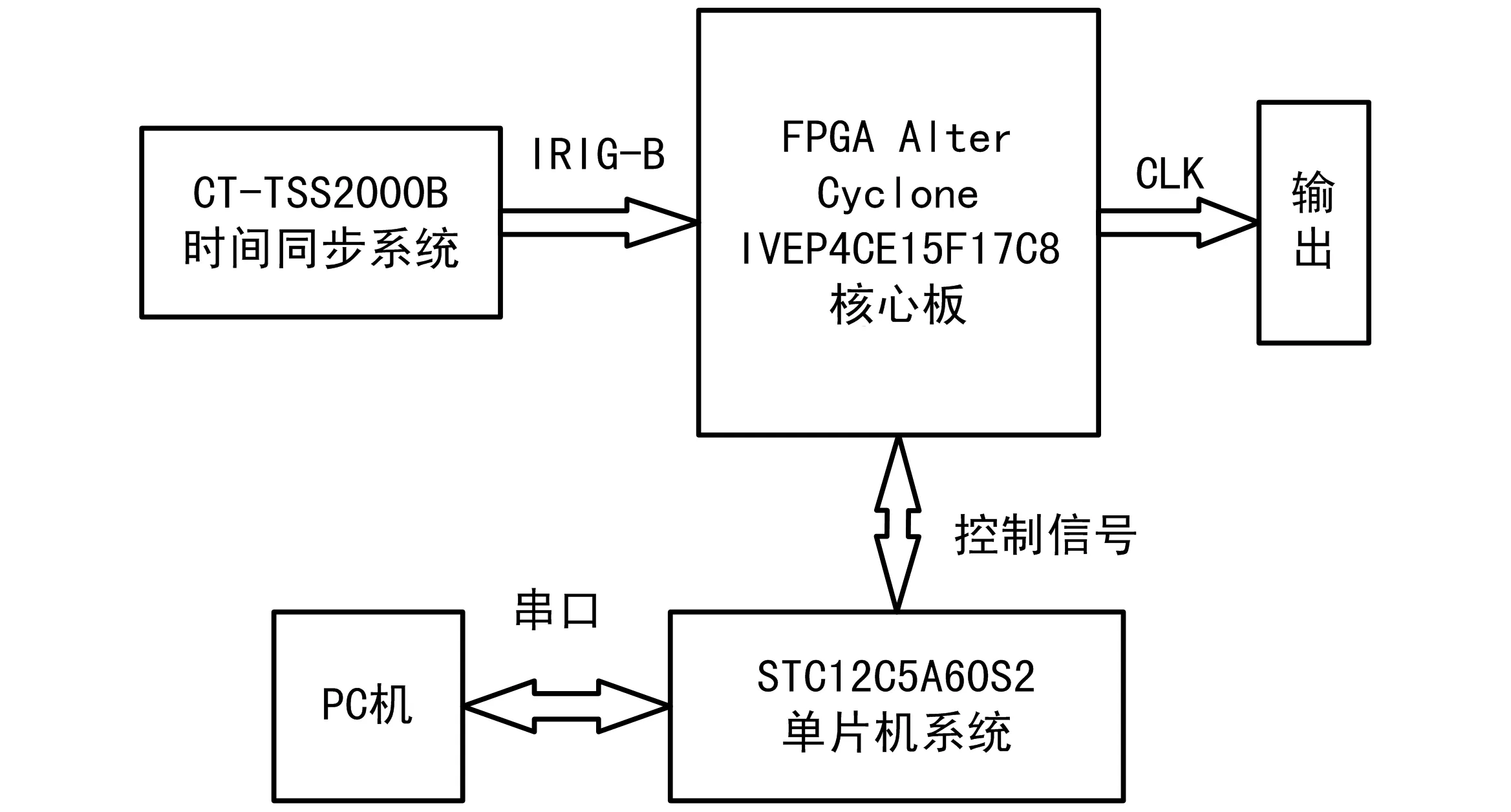

u温度 (4) 由式(2)、式(3)和式(4)可得采用JKOC36-25.6M型号的恒温晶体可以满足时钟按照1 kHz输出、连续工作8 h、误差不大于0.5个时钟周期的要求(计算温度对恒温晶体的影响造成的累计误差,按照最大误差计算)。 1.2时钟同步方案 时钟同步方案结构图如图1所示,主要由协议解析模块,实时时间计数器模块,高精度时钟生成模块和内部时钟源模块组成。FPGA器件接收CT-TSS2000B时间同步系统输出的IRIG-B,解析IRIG-B得到标准秒脉冲PPS和时间信息。将PPS和时间信息分别送到高精度时钟生成模块和实时时间模块。JKOC36-25.6M 恒温晶体为FPGA器件提供外部时钟,再通过锁相环电路倍频到100MHz的频率为高精度时钟生成模块提供基准时钟。在同步时,高精度时钟生成模块通过PPS秒脉冲来同步本身的时钟,并调整输出时钟的参数,实时时间模块直接接收解析的时间信息。在守时时,高精度时钟生成模块根据同步时时钟调整后的参数输出时钟,实时时间模块通过接收高精度时钟生成模块输出的PPS秒脉冲来更新时间。在同步半小时后,可以断开时钟源,进入守时状态。系统除了可以生成kHz的时钟,还可以通过锁相环动态生成MHz的时钟,输出时钟频率可以通过STC12C5A60S2单片机来控制。 图1 时钟同步方案结构 1.3高精度时钟生成和守时模块设计 高精度时钟生成模块的主要作用是,实现高精度时钟的生成方案以及守时方案,它由同步整形电路、相位比较电路、启动电路、分频电路和分频系数控制电路组成。该模块的结构如图2所示。 PPS秒脉冲接入高精度时钟生成模块模块之后,先经过同步整形电路,输出一个系统时钟(100MHz)周期宽度的秒脉冲PPS_Pulse。启动电路接收到PPS_Pulse信号之后,在信号的的上升沿发送启动信号给分频电路。分频电路在启动信号的上升沿启动,以初始分频系数108-1生成PPS_C秒脉冲信号,并将PPS_C秒脉冲信号送给相位比较电路。相位比较电路接收PPS_Pulse信号和PPS_C信号,并以系统时钟为单位计数2个秒脉冲的相位差,并将相位差传递给启动模块。启动模块接收到相位差之后,在PPS_Pulse的上升沿判断相位差是否小于20,如果连续20次相位差小于20个系统时钟周期,表明恒温晶体已经稳定,则发送启动信号给分频系数控制电路。分频系数控制电路接收相位差信号,调整分频系数并传递给分频电路。分频电路使用新的分频系数生成PPS_C信号,并传递给相位比较电路。相位比较电路再将相位差传递给启动电路模块和分频系数电路模块。如此循环,不断调整分频系数,同步0.5 h后,分频系数基本收敛稳定,可以断开时钟源。此时,可得到高精度的秒脉冲信号,再用秒脉冲信号复位系统所需要的时钟信号,以此来消除时钟信号的累计误差,达到较长时间保持时钟精度的目的。 在此过程中,启动电路一共有3个状态来控制其他电路的启动。启动信号模块在PPS_Pulse脉冲的上升沿发送启动信号给分频电路,分频电路启动之后,启动电路获取相位差,若相位差连续20次小于20,发送启动信号给分频系数控制电路。启动电路的策略如图3所示。 图3 启动电路状态转换 相位比较电路共有3个状态,来计数2个秒脉冲的相位差,为启动电路和分频控制电路提供依据。在PPS_Pulse的上升沿开始计数,在PPS_C的下降沿停止计数。停止计数之后判断计数值是否过大,如果数值大于256就重新计数,小于256便输出计数值。相位比较电路的状态转换图如图4所示。 分频系数控制电路共有4个状态,如图5所示。通过相位差来调整分频系数。分频控制电路接收到启动信号,开始启动,接收相位比较电路的相位差,再经过处理得到调整之后的分频系数。调整策略主要从时钟突变和随机误差考虑,分别采用加权和平均的方法来处理随机误差和突变的影响。 图4 相位比较电路状态 图5 分频系数控制电路状态 转换 转换 系统硬件装置采用成都可为科技有限公司的CT-TSS2000B时间同步系统输出的IRIG-B(InterRange Instrumentation Group)码作为同步时钟源,FPGA芯片EP4CE15F17C8核心板用来实现同步方案,完成时钟同步系统的主要工作。STC12C5A60S2单片机最小系统系统作为控制器,控制FPGA时钟输出的频率。JKOC36-25.6M 恒温晶体作为EP4CE15F17C8芯片的外部时钟源。电脑上位机软件可以通过串口与单片机最小系统通信,来控制时钟的输出。系统硬件框图如图6所示。 图6 系统硬件框图 系统开始运行,CT-TSS2000B时间同步系统首先接收GPS信号完成时间同步,完成同步之后输出IRIG-B时间基准信号。FPGA核心板接收IRIG-B信号,解析出时间信号和PPS秒脉冲,经过0.5 h时间完成同步。通过上述高精度时钟生成方法,输出PPS标准秒脉冲和高精度时钟。使用人员可以通过PC机应用软件与单片机控制器通信,实现时间信息查询和输出时钟频率的控制。 3.1实验环境 在实验中,为了证明本系统达到要求,在不同温度下可以保持精度。本文使用高低温交变试验箱作为外部温度变化的模拟,高低温交变试验箱是用于测试和确定电工、电子及其他产品及材料进行高温、低温、或恒定试验的温度环境变化后的参数及性能。系统硬件装置采用CT-TSS2000B时间同步系统输出的IRIG-B(InterRange Instrumentation Group)码作为同步时钟源,采用Alter公司Cyclone IV系列EP4CE15F17C8芯片的核心板实现同步方案,STC12C5A60S2单片机系统作为控制器和JKOC36-25.6M恒温晶体作为EP4CE15F17C8芯片的外部时钟源。 3.2实验结果 3.2.1温度试验 为了测试在不同温度下,系统的时钟精度是否达到要求。本次温度实验分别设定高低温交变试验箱的温度在-10℃,-5℃,0℃,10℃,20℃,30℃,40℃,45℃和50℃,在室温下(25℃)同步完成之后,来测试温度对系统时钟精度的影响,每个温度实验时间为1 h。得到温度与时钟误差关系图如图7所示,实验表明在0℃~30℃误差最小,通常1 h<20μs。随着温度的降低和升高,误差略有增大,通常小于40μs。1 h的试验通常误差已经稳定,可以预见为机器提供8 h的时钟可以满足要求。在-10℃~50℃之内满足要求,已达到高精度,低成本的要求。 图7 温度与时钟误差关系 3.2.2时钟稳定度试验 在本实验过程中,记录了常温下PPS_C秒脉冲在同步时的分频数。同步时的分频数表示时钟的稳定度,随着时间的推移,分频数的变化趋势如图8所示。 图8 时间与分频数偏移量关系 图8表明,在常温下,时钟的分频数在一定范围内波动,分频数在108-4~108+2之间波动,均值在108-1左右,波动范围在±3之内,具有较高的时钟稳定度。 本文从设备的便捷性和成本角度出发,提出了一种同步GPS时间同步系统的IRIG-B码的方法。在此方法的基础上使用FPGA器件,51单片机和恒温晶体完成了多机器信息采集时间同步系统的硬件实现。该方法通过同步基准时间信号源,并在断开信号源之后,可以在一定时间内保证时钟的精度。通过该方法达到了在误差不大于0.5个时钟周期的精度要求下,1 k的时钟输出,可以连续工作8 h。该系统可以以很小的体积和较低的成本嵌入到产品中,为其他采集系统提供同步信号源。在进一步的研究中将进一步提高精度和系统的稳定性。 [1]丁永红,徐强,汪芸.基于 NTP 的 ORBUS 时间同步系统[J].东南大学学报(自然科学版),2006,36(3):477-482. [2]李杏.网络时钟同步及时钟服务器稳定性研究[D].北京:北京化工大学,2012. [3]徐金平.网络时钟同步的研究[D].北京:北京化工大学,2004. [4]辛欣,游雄,刘芳,等.分布式虚拟地理环境中时间同步问题研究[J].测绘工程,2010,19(1):21-24. [5]张红亮.分布式系统时钟同步技术的研究与应用[D].长沙:国防科学技术大学,2002. [6]王刚,黄飞,乔纯捷,等.分布式网络时钟同步研究[J].仪器仪表学报,2008,29(11):2 399-2 403. [7]孙祥祥.分布式系统时钟同步协议的研究与实现[D].杭州:杭州电子科技大学,2014. [8]刘靖宇.基于 CAN 总线的分布式系统的时钟同步算法研究[D].青岛:青岛科技大学,2006. [9]熊慧.CAN 总线分布式系统高精度时钟同步技术的研究[D].武汉:华中科技大学,2007. [10]陈丕龙.分布式测试系统中的 GPS 时钟同步系统设计[D].太原:中北大学,2011. [11]龚晓春.分布式微型航天器的时钟同步研究[D].哈尔滨:哈尔滨工业大学,2007. [12]陈班贤.分布式水电厂监控时钟同步系统的研制[D].成都:电子科技大学,2013. 赵永发男,(1991—),硕士研究生。主要研究方向:嵌入式系统。 周磊男,(1980—),博士,讲师。主要研究方向:电子系统集成和专用集成电路设计。 Design on a Distributed Clock Synchronization System ZHAO Yong-fa,ZHOU Lei (CollegeofInformationEngineering,YangzhouUniversity,YangzhongJiangsu225000,China) The distributed clock synchronization system is the foundation of coordinated operation of distributed system.Based on the time synchronization technology,this paper designs a distributed clock synchronization system.Byusing IRIG-B(InterRange instrumentation group) time ignal as time synchronization source,this system can not only provide high-precision clock signal for the machine and maintain high precision within a period of time,but also improve the convenience with smaller volume embedding to the product.The experimental results show that the system can provide high-precision clock signals in different temperature conditions,and it has higher stability. distributed time synchronization;time keeping;clock stability;constant temperature crystal 10.3969/j.issn.1003-3106.2016.10.02 2016-06-23 国家自然科学基金资助项目(61376025,61301111);江苏省高校自然科学基金资助项目(13KJB510039);江苏省普通高校研究生科研实践计划项目(SJZZ_0182)。 TN919 A 1003-3106(2016)10-0008-04 引用格式:赵永发,周磊.一种分布式时钟同步系统设计[J].无线电工程,2016,46(10):8-11.

2 硬件实现

3 实验结果

4 结束语