一种面向空间机械臂运动控制的容错计算机体系结构

2016-10-19梁常春唐自新

侯 亮,梁常春,张 沛,唐自新

(北京空间飞行器总体设计部 空间智能机器人系统技术与应用北京市重点实验室,北京100094)

一种面向空间机械臂运动控制的容错计算机体系结构

侯 亮,梁常春,张 沛,唐自新

(北京空间飞行器总体设计部 空间智能机器人系统技术与应用北京市重点实验室,北京100094)

针对现有航天抗辐照高可靠处理器难以满足空间机械臂运动控制运算量大的问题,结合机械臂运动控制算法的特点,提出了一种由双机主模块和多机从模块组成的面向空间机械臂运动控制的容错计算机体系结构。该体系结构中,主模块以航天专用抗辐照处理器为核心进行设计,从模块以商用现货(COTS)器件为核心进行设计,其中从模块负责运动控制运算,主模块负责从模块运算结果的表决及任务管理、健康管理等工作。系统容错性能和可靠性分析结果表明,该运动控制计算机体系结构容错能力强、可靠性高,在空间机械臂领域具有良好的应用前景。

空间机械臂;运动控制计算机;容错;计算机体系结构

1 引言

随着我国航天事业的快速发展,对空间机械臂的需求不断增多。空间机械臂的运动控制计算机负责整个机械臂系统的运动规划、传感器信息融合、伺服控制器的调度以及整个机械臂系统的健康管理等,是空间机械臂智能控制的核心,运动控制计算机的性能直接决定了空间机械臂的控制性能。在机械臂运动控制运算中含有大量的浮点乘加运算、三角函数运算和反三角函数运算,对星载计算机的性能要求很高。基于可靠性考虑,星载计算机一般会采取抗辐照设计[1],但航天抗辐照加固处理器难以满足机器人运动控制算法的要求。文献[2]利用FPGA(Field Programmable Gate Array,现场可编程逻辑门阵列)实现了基于CORDIC算法的专用协处理器,提高了运动控制运算的速度,但由于路径规划算法流程复杂,运算种类多,采用FPGA难度较大,灵活性也较差,难以适应多种任务的需求。并且由于FPGA是单粒子敏感器件,在空间应用中需要对FPGA采取各种抗辐射加固措施[3-4],增加了应用难度和系统复杂度。文献[5]基于商用现货(COTS)器件设计了双机备份的空间机器人计算机,采用了错误检测与校正(EDAC)系统、看门狗和防闩锁电路等可靠性措施,但由于其采用双机备份设计,不具有纠错功能,在发生故障的情况下系统无法继续运行,系统连续工作的能力无法保证。

本文结合空间机械臂运动控制算法的特点,提出一种面向空间机械臂运动控制的容错计算机体系结构。该体系结构计算机以航天专用抗辐照处理器和商用现货产品(COTS)为核心进行设计,核心运算由商用现货产品负责,主模块负责任务管理及从模块输出结果的表决。

2 空间机械臂运动控制算法特点分析

以机械臂最典型的笛卡尔空间直线规划为例,给定目标点的位姿,要求机械臂末端从当前位姿以规定的速度直线运动到目标位姿。

图1 机械臂末端运行轨迹Fig.1 Trajectory of the end-effector

图2 典型的机械臂直线规划流程Fig.2 Typical linear path-planning procedure

笛卡尔空间直线规划流程[6]如图2所示。控制器以初始关节角度、期望目标点位姿、期望速度和加速度等为输入,进行规划总时间和加速时间的计算,然后按固定的路径规划周期进行运动规划计算,每个周期结束时以各关节规划角速度为输出。

由图2可见,机械臂的运动控制具有典型的周期性特点:一个完整的运动是由顺序执行的众多周期性的单步运动组成。空间机械臂的运动速度一般都比较小,以加拿大为国际空间站研制的大型遥操作臂系统(SSRMS)为例,末端最大线速度为0.36 m/s[7],在一个控制周期内运动距离很小,因此对控制周期精确度要求不高。由于空间机械臂运动速度慢,因此对单步运动周期的要求不高,但考虑到机械臂控制稳定性以及末端轨迹精度的要求,一般要求机械臂的单步运动周期在50~200 ms。

机械臂的运动控制运算量大,运算过程复杂[8],根据对某直线路径规划算法的分析结果,每一个路径规划周期(50~200 ms)需要进行12 801次乘法运算、246次除法运算、13 346次加法运算、397次减法运算、318次三角函数运算和42次取模(求余数)运算,且上述运算均为单精度浮点运算,。某机械臂控制器选用了TI公司的C6000系列浮点DSP TMS320C6713对上述路径规划算法进行了实现,DSP工作主频为225 MHz,运算能力为1.35 GFLOPS。在此运算能力下,控制器完成一次路径规划所需的时间约为5 ms。以目前在国内航天领域广泛应用的高性能处理器BM3803处理器[9]为例,在峰值工作频率下其运算能力为23MFLOPS,不考虑工作频率降额的情况下,其完成一次路径规划所需的时间大约为300 ms。

经上文分析可知,传统的针对宇航应用的抗辐照处理器运算性能难以机械臂运动控制器需求,而商用现货器件虽然性能高,但无抗辐照指标,可靠性差。本文提出一种试图结合上述器件优点的设计方案。

3 运动控制计算机设计

3.1 系统总体设计

本文设计的运动控制计算机的运算核心由双机主CPU模块和多机从CPU模块组成,其中主CPU模块以航天高可靠性CPU为核心进行搭建,其主要功能为完成整个运动控制计算机的健康管理、从模块的故障检测及数据判决,主模块可根据需求工作于双机热备份或双机冷备份工作模式。从CPU模块以高性能的商用CPU为核心进行搭建,其主要功能为完成运动控制计算机中运算量较大的核心运动控制算法,工作于多机热备份状态。整个系统的原理框图如图3。

图3 运动控制计算机原理框图Fig.3 Schematic diagram of the motion control computer

主从CPU模块间可通过单机内部总线进行数据的传输,且主从CPU模块之间有硬指令和遥测通道,可用于主CPU模块监视从CPU模块的状态(如工作电压),并通过相关状态控制从CPU模块的工作模式(如加断电、复位等)。

3.2 系统工作原理

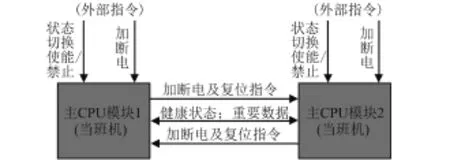

主CPU模块工作于双机温备份状态,分为当班机和非当班机,双机可交互状态信息,并可互相控制复位和加断电。从CPU模块工作于多机热备份状态,其设备间无数据交互。

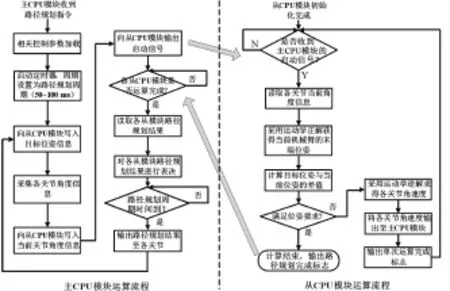

主CPU模块当班机在进行运动控制时采用时间触发的方式运行,时间周期为路径规划周期。在每一个路径规划周期,主CPU模块需要根据接收到的各关节的当前角度、角速度以及相机的测量数据、力传感器数据等,根据控制模式,将相关数据输出至各从CPU模块,并启动从CPU模块的运算,在从CPU模块计算完成后,读取各从CPU模块计算结果并进行表决判断,然后将表决后的各关节的规划角度和规划角速度输出至各关节。

从CPU模块采用任务触发的方式运行。在加电启动或复位并完成初始化后,处于等待状态,只有收到主CPU模块的启动指令后才进行运算,运算完成后置位相关状态位,通知主CPU模块计算完成。系统的信息流图如图4所示。

图4 系统信息流图Fig.4 System information flow

整个系统完成一次路径规划的工作流程如图5所示。

图5 系统路径规划工作流程图Fig.5 Flow-chart of the path-planning procedure of the system

4 系统性能分析

4.1 系统时间分布分析

根据图5所示的系统工作流程,整个计算机的时间分布如图6所示。

各符号含义如下:

1)Tp:完成一次路径规划运算所需时间。

2)Tm1:主CPU模块采集关节数据并写入从CPU模块的时间。

图6 系统时间分布图Fig.6 Time distribution of the system

3)Tcd:从CPU模块完成一次路径规划运算所需时间。

4)Tm2:主CPU模块读取从CPU模块数据并表决后输出的时间。

为保证系统正常运行,要求Tm1+Tcd+Tm2<Tp。Tm1和Tm2为主从CPU模块数据交互的时间。在路径规划过程中,主从CPU模块需交互的数据包括各关节的位置、速度以及相关传感器的测量信息,数据量在几十字节量级。主从CPU模块间采用并行数据总线进行数据传输,以BM3803处理器[9]为例,其对存储区及IO区的访问速度最快可达到3个系统时钟周期,即使主频为20 MHz,在数据总线宽度为较窄的8 bit的情况下,其传输速率可达50 Mbps以上,因此上述数据传输在1 ms之内完全可以完成,考虑一定裕量,将数据交互时间分配为5 ms。

假设路径规划周期Tp为50 ms,扣除掉分配给主从模块数据交互的时间,分配给从CPU模块的运算时间为45 ms,只要Tcd<45 ms,即可满足系统要求,而对各从CPU模块之间的同步性能无要求。由于从CPU模块运算起始时间在每一路径规划周期均进行同步,不存在误差累积的过程,因此从CPU模块可进行同构或异构设计,大大提高了系统设计的灵活性。

4.2 系统容错性能分析

对于主CPU模块,本文采用的是双机温备份的工作模式。当班机负责运动控制,非当班机对当班机进行状态监控,当班机主CPU模块需要将自身的健康状态数据以及运动控制的相关重要数据输出至非当班机主CPU模块的状态,用于非当班机主CPU模块监视当班机主CPU模块,并在当班机主CPU模块故障时接替其进行工作。对于主CPU模块,可实现“故障-安全”的目标。主CPU模块故障检测用数据信息流如图7所示。

图7 主CPU模块间信息流Fig.7 Information flow between the master CPU module

对于从CPU模块的故障,由于采用了多机热冗余结构,其运算结果需要通过主CPU模块进行表决,主CPU模块根据表决结果对从CPU模块的工作状态进行控制,如复位或加断电,主从CPU模块间的信息流入图8所示。瞬态故障同时发生在多个从CPU模块上的概率很低,某采用COTS器件的星载计算机[10],其在轨数据显示在16个月的时间中,发生了523次复位事件,平均每天1.1次。因此,只要从CPU模块正常工作的数量不少于3个,主CPU模块可实现对从CPU模块故障的检测和纠正,而不影响整个系统的正常运行,可实现“故障-运行”的目标。而当从CPU模块正常工作的数量为2个情况下,主CPU模块可对从CPU模块的输出结果进行比对,此时能实现故障的检测,可实现“故障-安全”的目标。

图8 主从CPU模块信息流Fig.8 Information flow between the master and slave CPU module

4.3 系统可靠性分析

本文设计的系统为典型的表决系统,为具有检错功能,应保证从CPU模块至少有2台正常工作。假设单个从模块的可靠度为RC,从模块的数量为n,系统中可正常工作的模块数量为i,则从CPU模块组成的表决系统的可靠度RNMR如式(1):

假设单个主CPU模块的可靠度为RZ,主从CPU模块通信及接口部分的可靠性近似为1,为方便分析,主CPU模块按照故障率更高的热备份状态进行分析,则整个计算机系统的任务可靠度如式(2):

假设主CPU模块的失效率为1×10-6/h-1,从CPU模块由于采用了低等级器件,其失效率相比主CPU模块要高。以从CPU模块失效率λc与主CPU模块失效率λz的比值Nλ为横坐标,系统10年末期的可靠性RS为纵坐标,可得系统可靠性RS与Nλ的函数关系如图9所示。

由图9可见,整个系统的可靠性主要受从CPU模块数量n和单个从CPU模块失效率的影响。如果采用最常见的三模冗余系统(n=3),当从CPU模块的失效率为主CPU模块的2倍时,从CPU模块的组成的表决系统的可靠度会高于单个主CPU模块的可靠度。随着从CPU模块失效率的增加,表决系统的可靠度逐渐降低,甚至会低于单个模块的可靠度。因此在实际应用中,为保证系统可靠性,应严格控制从CPU模块的失效率,在满足性能要求的情况下,尽可能选择失效率低的元器件,如对处理器的一些外围器件,如存储器、接口器件等,尽量选择高质量等级的器件,避免采用过多的从CPU模块提高系统的可靠性,简化设计。

图9 10年末期可靠度Fig.9 Reliability of 10 years telophase

5 结论

本文在对空间机械臂运动控制算法特点进行分析的基础上,提出了一种面向空间机械臂运动控制的容错计算机体系结构,该体系结构只要求从CPU模块的性能满足路径规划需求,对从CPU模块的内部结构以及各从CPU模块之间的同步性能无严格要求,很好地满足了空间机械臂运动控制计算机的高性能和高可靠要求,便于工程实现,具有广泛的适用性。后续可考虑针对从CPU模块的瞬时故障进行实时的在线纠正和恢复,从而进一步提高系统的容错性能和系统可靠性。

(References)

[1]Hillman R,Swift G,Layton P.Space processor radiation mitigation and validation technologies for an 1800 MIPS processor board[C]//Radiation and Its Effects on Components and Systems,2003.RADECS 2003.Proceedings of the 7th European Conference on.IEEE,2003:347-352.

[2]史国振,孙汉旭,贾庆轩,等.空间机器人专用控制计算机体系结构研究[J].计算机集成制造系统,2008,14(9):1810-1817.Shi Guozhen,Sun Hanxu,Jia Qingxuan,et al,Dedicated control computer architecture for space robot[J],Computer Integrated Manufacturing Systems,2008,14(9):1810-1817.(in Chinese)

[3]Yui C,Swift G,Carmichael C.Single event upset susceptibility testing of the Xilinx Virtex II FPGA[C]//Military and Aerospace Applications of Programmable Devices and Technologies Conference(MAPLD),2002.

[4]邱金娟,徐宏杰,潘雄,等.SRAM型FPGA单粒子翻转测试及加固技术研究[J].电光与控制,2011,18(8):84-88.Qiu Jinjuan,Xu Hongjie,Pan Xiong,et al,Study on testing and harden technique of single event upset for SRAM-based FPGA[J],Electronics Optics&Control,2011,18(8):84-88.(in Chinese)

[5]谢宗武,魏然,金明河,等.基于商用现成器件设计星载计算机关键模块的研究[J].高技术通讯,2008,18(12):1285-1290.Xie Zongwu,Wei Ran,Jin Minghe,et al.Research on key technologies of on-board computer design with commercial offthe-shelf devices[J].Chinese High Technology Letters,2008,18(12):1285-1290.(in Chinese)

[6]王伟.空间机械臂路径规划研究[D].哈尔滨:哈尔滨工业大学,2008.Wang Wei.Research on Path Planning of Space Manipulator[D].Harbin:Harbin Institute of Technology,2008.(in Chinese)

[7]李大明,饶炜,胡成威,等.空间站机械臂关键技术研究[J].载人航天,2014,20(3):238-242.Li Daming,Rao Wei,Hu Chengwei,et al.Key technology review of the research on the space station manipulator[J].Manned Spaceflight,2014,20(3):238-242.(in Chinese)

[8]杨明远,孙汉旭,贾庆轩,等.七自由度空间机械臂避障路径规划方法[J].航天器工程,2011,20(4):65-71.Yang Mingyuan,Sun Hanxu,Jia Qingxuan,et al.Research on path planning for 7-DOF space manipulator to avoid obstacle[J].Spacecraft Engineering,2011,20(4):65-71.(in Chinese)

[9]BM3803MG 32位空间处理器用户手册[M].北京:北京微电子技术研究所,2010.Usermanual of 32 Bit Space Processor BM3803MG[M].Beijing:Beijing Microelectronics Technology Institute,2010.(in Chinese)

[10]Barnard A,Nwosa C.COTS based on-board-computer on South Africa's sumbandilasat:A radiation and in-orbit performance analysis[C]//2011 IEEE Radiation Effects Data Workshop.2011.

A Fault-tolerant Motion Control Computer Architecture for Space Manipulator

HOU Liang,LIANG Changchun,ZHANG Pei,TANG Zixin

(Beijing Key Laboratory of Intelligent Space Robotic System Technology and Applications,Beijing Institute of Spacecraft System Engineering,Beijing 100094,China)

The motion control of space manipulator requires high processing capability,but the available high-reliability and anti-radiation processor has low performance in computation.To solve this problem,a fault-tolerant motion control computer architecture was proposed considering the characteristics of the motion control algorithm.The system consisted of the double-backup master CPU module and N-backup salve CPU module.The CPU of the master module was high-reliability and anti-radiation processor while the slave module was COTS processor.The master module was in charge of the task management,health management and voting of the slave module whose main task was motion control computation.The architecture proposed in this paper was verified to be fault-tolerant and with high-reliability.It has promising application potentials in space manipulator.

space manipulator;motion control computer;fault-tolerant;computer architecture

V446

A

1674-5825(2016)05-0550-05

2016-01-12;

2016-08-08

国家自然科学基金(61573058)

侯亮(1985-),男,硕士,工程师,研究方向为星载计算机。E-mail:13811714268@163.com