纳米CMOS电路在单粒子效应下可靠性分析

2016-10-18赵智超吴铁峰

赵智超+吴铁峰

摘要:随着电子元器件的尺寸在不断的发生变化,使得电容和电压不断的降低,纳米CMOS电路对单粒子效应(SEE)的敏感性更高,并且由于单粒子的串扰和多结点翻转现象明显增加,使得工作的可靠性受到一定的影响。为了更好的保证纳米CMOS电路在SEE下的可靠性,从多方面来对其进行分析和研究,最后通过研究发现,影响纳米CMOS电路在SEE下的可靠性的焦点可能是:抗单粒子瞬态的加固研究、CMOS电路的抗辐射加固设计研究、仿真及加固研究等。

关键词:纳米CMOS电路;单粒子效应;可靠性

中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2016)21-0261-02

随着科学技术的不断发展,各种电子元器件和技术也在进行着不断的改进。航天和航空领域逐渐的使用微处理器和混频器等电子元器件,其需要受到环境严厉的考验。对国内外的数据进行分析统计,在空间环境中发生航天器故障中,单粒子诱发发生故障率高达28.5%,所以来讲,SEE对集成电路的可靠性有着严重的危害。从基本电力损伤原理、可靠性评价、单粒子对电路的影响等多方面来对纳米CMOS电路在SEE下的可靠性的研究进行阐述,提出了在研究中所面临的问题。

1 对单粒子效应对电路产生的影响进行分析研究

软错误率(soft error rate, SER)是指SEE对电路所产生的一系列的影响,其中软错误率数值越低,则单粒子效应对集成电路的影响就越小,呈正比关系;反之,软错误率数值越高,则单粒子效应对集成电路的影响越严重。因此,SER数值的大小就成为了衡量SEE对集成电路影响程度的一种关键性方式。SER是元器件尺寸和临界电荷的函数,并且SER数值不会根据电子元器件尺寸的大小而发生改变。其次,单个高能粒子的存在,使得存储器的数据改变,并且会对微纳电子电路产生致命的伤害,所以需要建立出计算SER数值的模型,即建立一个软错误率数值评估模型。

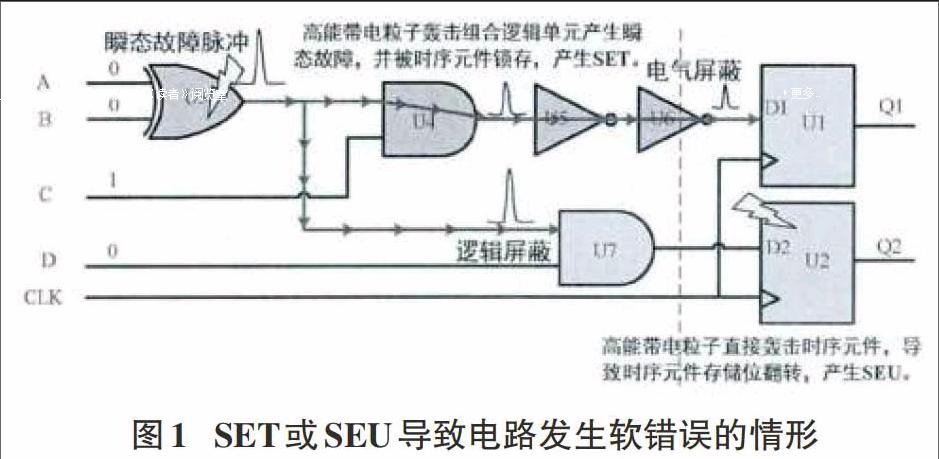

电路的软错误率数值和临界电荷值之间的关系非常的密切,两者呈反比的关系,即临界电荷数值越大,则电路的软错误率数字越小。因此说,需要对临界电荷进行充分的研究和了解。电子元器件尺寸的不断减小、结电容和工作电压也在不断地下降,从而导致SEU临界电荷值降低,对软错误率的敏感性增强。SEU临界电荷数值的变化与电路的形状、工艺技术有着一定程度的联系。(如图1所示)比如,在对90nm工艺的SRAM发生SEU所需的临界电荷进行分析研究时发现,不同的电流模型所产生的结果存在较大的差异性。由此可知,软错误率的误差已经上升到两个数量级。

在建立SEE模型时,借助多种方式和多种手段来进行,通过研究发现,随着电子元器件的尺寸在不断的发生变化,使得电容和电压不断的降低,纳米CMOS电路对单粒子效应(SEE)的敏感性更高,并且由于单粒子的串扰和多结点翻转现象明显增加,使得工作的可靠性受到一定的影响。科学技术的不断发展,工艺技术也在逐渐提高,元器件的尺寸向纳米尺度进行改进时,单粒子瞬态杜数字电路的影响逐渐的显现出来。纳米工艺电路中电离辐射的不稳定性、耦合效应等多方面的因素都会数字电路的单粒子瞬态产生影响。

2 可靠性评估及加固设计的研究

随着社会的不断发展,科学技术也在快速的发展中,IC的集成度也在不断的提高,使得IC的微纳电子元器件的数量呈指数增加,使得集成电路在单粒子效应下的可靠性逐渐降低。半导体元器件的可靠性与时间概念、失效概念、概率统计等多方面有着密切的联系。2006年将二进制判决图和代数判决图两种方式运用在对集成电路可靠性的研究中,由此来对逻辑电路中软错误的敏感度进行评估,从多方面来对集成电路的可靠性进行综合性的分析。与此同时,也对高k栅电介质等在单粒子效应下的可靠性进行了系统性的分析和研究。

研究者不仅仅借助现有的方式对集成电路的可靠性进行系统性的研究外,还对集成电路可靠性的评估进行分析。2001年,将非常数故障率的模型作为基础研究条件,并且提出了一种较为科学合理的评估方法,并且在2008年以信号概率为基础条件,提出了对纳米CMOS电路的可靠性研究分析方法,研究认为:电子元器件的尺寸逐渐的向纳米尺寸进行改进,使信号概率成位多个故障同时发生的函数。以概率转移矩理论等多种理论为基础条件,建立SEU和单粒子串扰多方面影响下,纳米CMOS电路可靠性的研究模型,对信号概率模型等进行定义,从而形成对应的函数。由于函授的建立受到多方面因素的影响,在此基础上建立了纳米CMOS电路可靠性的综合评估模型。

使用抗辐射加固技术对现有系统在辐射环境下可靠性进行研究,并且提高其可靠性。目前,国内主要的抗辐射加固技术有:工艺技术加固、设计加固等。其中最为主要的技术是设计加固和系统加固。工艺技术加固是从工艺的角度上来对电子元器件的抗辐射能力进行提高。设计加固是将标准的CMOS工艺作为前提条件,采用多元化的设计方式来实现的加固技术。但是采用这种方法不能进行通用,需要根据集成电路的具体结构和用途来进行专业化的设计。系统加固借助软件或硬件系统,对其进行加固的。此外,加固技术还包含其他的改进方面:时间冗余、C单元冗余等方法。

此外,国内外优秀的专家研究者对SET的加固设计也进行关注。2004年,深亚微米集成电路的可靠性加固设计中,主要对故障容错性和功率消耗两方面的因素进行考虑。2006年,逐渐的将电源电压和器件尺寸优化技术进行广泛的使用,提出了关于70nm集成电路可靠性和功耗折衷的加固方式。对70--180nm的集成电路来讲,借助逻辑门的多元化逻辑形式对概率进行遮掩,并且对遮掩概率数字最小的逻辑门进行技术加固,不仅使得集成电路的可靠性大大增强,并且还能将使面积、功耗和延时进行最小化处理。2008年,以关联功能性冗余互连线的选择性为基础,借助集成电路的逻辑性功能,提出了可以最大限度的减少软错误的设计方法,使得SET能够有效的降低,从而达到设计要求的输出的概率,有效的提高系统的可靠性。2012年,以物理机制作为前提条件,采用抗辐射设计技术对90nm的 CMOS电路进行技术加固,使得SET的脉冲宽度能够有效的减少,最大限度的发挥抗辐射性能。E Smith依托两模冗余技术对时序电路中SET的发生进行系统的分析和检测,当发生SET时,系统会发出指令,对电路进行“冻结”,随着时间的不断推移,SET逐渐消失,系统发出指令,对电路进行“解冻”,由此来实现时序电路的抗SEU和SET加固。

3 结语

随着电子元器件的尺寸在不断的发生变化,使得电容和电压不断的降低,纳米CMOS电路对单粒子效应(SEE)的敏感性更高,并且由于单粒子的串扰和多结点翻转现象明显增加,使得工作的可靠性受到一定的影响。对其所遇到的问题进行系统的分析和研究,有利于最大限度的发挥其功效,促进社会的发展。

参考文献:

[1] 刘保军,蔡理,董治光.纳米FinFET器件的单粒子效应研究[J].原子核物理评论,2014(4).

[2] 卓青青,刘红侠,王志.三维H形栅SOINMOS器件总剂量条件下的单粒子效应[J].物理学报,2013(17).

[3] 刘必慰.集成电路单粒子效应建模与加固方法研究[D].国防科学技术大学,2009.