基于FPGA的水下多路数据采集存储系统

2016-10-14肖大为

喻 鹏,肖大为,姬 庆

基于FPGA的水下多路数据采集存储系统

喻 鹏,肖大为,姬 庆

(海军工程大学,武汉430033)

设计了以FPGA器件SPARTAN-6系列为核心的多通道数据采集存储系统,通过FPGA对扩展AD和存储卡的工作时序控制,实现数据采集存储功能。该系统具有可靠性强,采集速度快,体积小,存储空间大和功耗较低的特点。

FPGA 数据采集 数据存储

0 引言

随着对海洋开发力度的加大,水下信号采集在军事、民用上需求越来越大。相比于陆地上,水下数据采集存在着工作环境复杂,数据通讯困难的问题,所以一般均采用先采集存储后取出来进行数据分析的方法。这对采集可靠性、采集工作时长、存储容量要求较高。

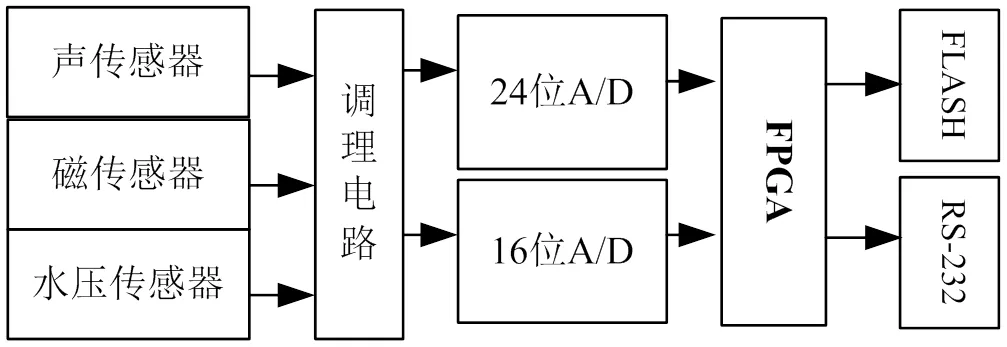

本系统初步设计具有6个采集通道,实现对声信号(声信号和声包络信号)、磁信号(磁信号分x、y、z三路)、水压信号的采集存储。通过对声、磁、水压信号的提取不仅可以对水下目标的特征进行识别,同时也能够对目标方位进行判别,这对军用及民用探测领域都有一定的使用价值。本系统工作效率高,能连续工作100 h,存储容量大(32G)、成本低,应用性强。

1 系统组成结构

水下采集的信号首先经过信号调理模块进行处理,然后经过AD采样送入FPGA中,经过数据处理后存储到存储器中。与A/D芯片的接口采用FPGA,A/D的串行数据需要经过内部的FIR滤波器进行滤波后串行输出给FPGA,FPGA完成数据处理,存入FIFO(先进先出存储器),当数据存储量达到一定状态时,进行位校验运算,校验完成后将数据写入FLASH。

整体设计如下:

图1 物理场采集模块原理框图

FPGA选用的XILINX公司出品的SPARTAN-6系列的XC6SLX9芯片,它拥有144个管脚,接近100个可用管脚,含4个时钟倍频器。

AD芯片选用AD7671。由于本系统的采样速率要求高,采样字长为16位,选择美国AD公司生产的AD7671作为采集电路模块的模数转换器。该芯片单+5V供电,最大功耗仅为112mW,符合低功耗设计原则,适合于电池供电系中应用;精度为16位;采样速率为800KSPS(正常模式),可满足系统要求。

存储芯片选用三星公司生产的K9GB08U0A型,它属于NAND型FLASH存储器,容量32G,3.3V供电,体积小,数据读取存储速度快。FLASH型存储介质具有高密度、高速体系结构、低价格,高可靠性、低功耗等特点,成为记录器系统最常用的存储介质。而NAND型FLASH的数据线与地址线分时复用,这样就大大减小了芯片的封装体积,读写操作以页为单位,擦除以块为单位,因此编程和擦除的速度快,体积小,价格低[1],基本满足要求。

2 硬件电路设计

2.1信号调理模块设计

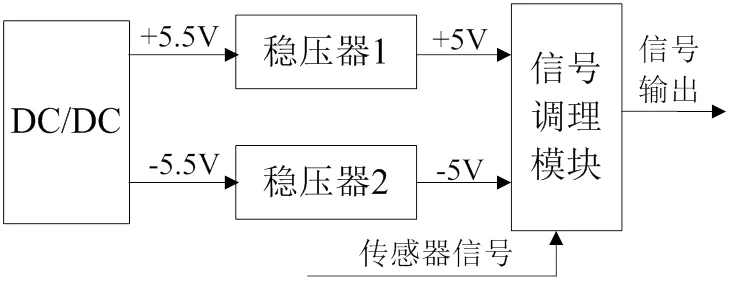

信号调理模块对传感器输出信号进行放大、滤波等信号预处理,满足信号采集要求。主要包含电源变换模块、放大滤波电路和数字滤波电路。其中数字滤波电路实现各个信号数字滤波。电源变换电路如图2。

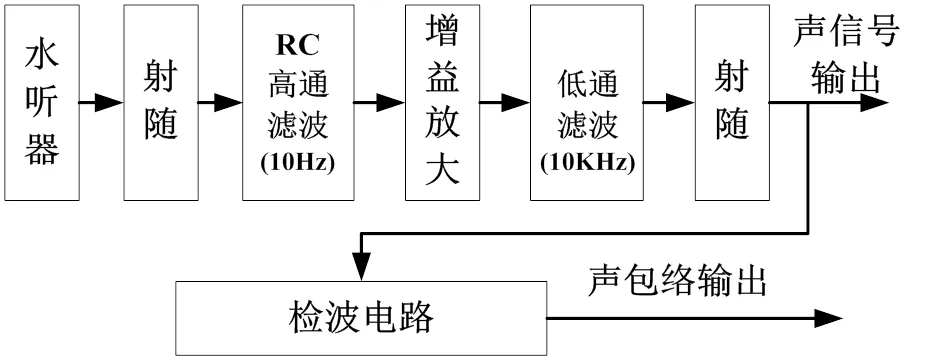

水声信号在传播过程中衰减得非常严重,换能器接收到的水声信号通常比较微弱,一般为μV级信号,不适合A/D转换器直接采样。因此,必须先经过信号调理电路的处理[2]。为实现对声信号采集,声信号调理电路需要完成对声传感器输出信号的调理功能。其主要参数为:10Hz~10 kHz的带通滤波,带内波动≤1dB,通带增益40dB,输出端噪声≤ 5mV,±5V供电,输出声调理信号和声包络信号,电路原理如图3所示。

图2电源变换电路

图3 声调理电路原理

2.2采集和存储模块设计

采集和存储模块设计了六路模拟信号输入,分别为声、声包络、水压、磁场X、磁场Y和磁场Z,设计分辨率为65 μV,总记录深度为32G字节,设计功耗<600mW。

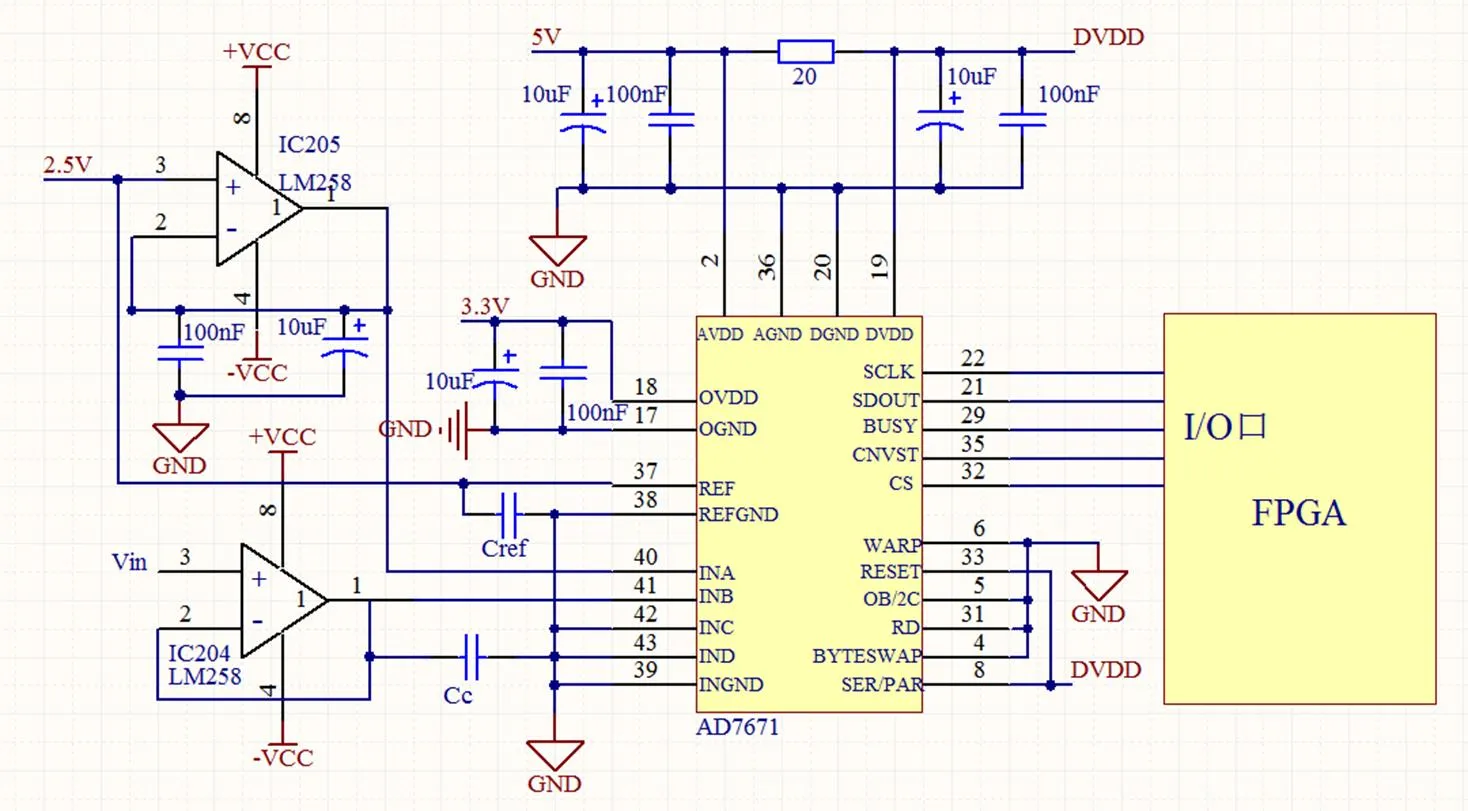

图4 FPGA与AD连接电路图

与A/D芯片的接口采用的FPGA不仅接收A/D的数据,同时它也是A/D的时钟提供者。在设计上,FPGA使用了20MHz的外部晶振,经过分频后输出给6路A/D,其中声采样采用320 kHz采样(A/D的FIR滤波器会8分频数据),输出40 kHz,其他5路采用320Hz采样,40Hz输出。A/D的串行数据输出到FPGA后,FPGA完成串并转换,并进行电压转换,完成电压值的矫正。

设置AD7671转换器工作在正常模式,输入模拟信号电压范围为±5V,数据吞吐量800kSPS,转换结果串行输出。需要三组电源:模拟5V电源(AVDD),数字5V电源(DVDD),3.3V逻辑参考电源(OVDD与FPGA一致)。由于一共有6路信号需要采样,则需要通过FPGA分别控制6个AD采样器的进行流水采集和数据传输。为降低干扰,提高采样精度,参考数据手册,设计如图4采集电路。

AD传送的数据首先存入FIFO(先进先出存储器),当数据达到一定状态满时,进行位校验运算,校验完成后将数据写入FLASH,存储模块电路图如图5。

本存储芯片采用数据线与地址线复用的方式读取和存储数据,读写操作以页为单位,擦除以块为单位[3]。存储时,首先由8路I/O口传送写命令,然后由I/0分4次写入地址,并进行锁存,之后再由I/O口写入数据,写入结束后传输写入结束命令,写入完成。读操作、擦除操作过程与上述写操作基本一致。

3 实验仿真

FPGA芯片控制整个电路时序,FPGA使用了20 MHz的外部晶振,经过分频后输出给6路A/D以及存储芯片作为时钟信号,同时通过部分I/O口控制各个芯片的工作时序。

图5 FPGA与FLASH连接电路图

利用QUARTUS软件仿真采集模块的工作时序。FPGA输出信号有SCLK(子时钟),CS(片选信号),CNVST(启动采集转换信号),输入信号为BUSY(采集转换状态信号),SDOUT(串行输出数据)。部分仿真图如图6。

图6 采集时序仿真图

其工作过程为:由CNVST窄脉宽信号独立促发芯片开始采样,采样完成并进行转换之后BUSY由高电平变为低电平,FPGA检测BUSY信号,通过控制CS信号对AD转换后数据进行读取,其中SCLK信号为FPGA提供的同步信号,由SDOUT串行输入转换结果。

4 结语

本文设计了以FPGA为核心控制器件,多片A /D器件流水高速采集并利用FLASH进行大量存储的系统,重点对采集和存储模块进行介绍,设计了采集模块和存储模块的硬件电路,并利用verilog语言编程仿真实现。本系统采集通道的可依据需要进行扩展,通用性较强,在水下信号采集领域具有一定的应用价值。

参考文献:

[1] 任勇峰. FLASH存储器的高速写入方法. 电脑开发与应用, 2001, (5): 5~6.

[2] 赵志刚.舷侧阵主、被动自导实验系统的硬件设计[D]. 西安: 西北工业大学, 2007.

[3] 李士照,任勇峰. 某水下用记录器的设计及实现. 中北大学硕士学位论文, 2013.

[4] 王彦. 基于FPGA的工程设计与应用[M]. 西安: 西安电子科技大学出版社, 2007.

Multi-channel Signals Sampling/Storage System Based on FPGA

Yu Peng, Xiao Dawei, Ji Qing

(Naval University of Engineering, Wuhan 430033, China)

TP273

A

1003-4862(2016)10-0058-03

2016-05-09

喻鹏(1992-),男,硕士在读。研究方向:军用目标特性及探测。