基于Vivado HLS的FFT IP核设计与实现

2016-10-13张俊涛付芳琪曹梦娜

张俊涛,付芳琪,曹梦娜

(陕西科技大学电气与信息工程学院,西安710021)

基于Vivado HLS的FFT IP核设计与实现

张俊涛*,付芳琪,曹梦娜

(陕西科技大学电气与信息工程学院,西安710021)

研究基于Xilinx高层次综合工具HLS设计FFT IP核的新方法,并在Zynq平台上搭建音频频谱显示系统用于对设计的FFT IP核进行测试。首先用MATLAB生成1 024点FFT算法所需要的旋转因子,然后用C语言编写FFT算法程序后经HLS综合成IP核并进行了两次优化,与优化前相比延迟时间节省了19%到40%,LUT资源节省18.5%。测试结果表明,所设计的FFT IP能够成功地实现音频信号的频谱分析。

高层次综合;FFT;IP核;设计;频谱;测试

FFT算法在数字信号处理中占有非常重要的地位,用于对信号进行频谱分析。FFT既可以通过软件编程的方式实现,也可以用FPGA实现。由于FPGA具有并行处理的特点,因此基于FPFA实现的FFT具有更高的运算速度和可靠性。但设计FFT IP核需要掌握硬件描述语言,并在提高时序等性能方面需要进行反复仿真和优化,为满足频谱处理在精度和实时性方面需要,开发难度大。

HLS是Xilinx新一代开发平台Vivado中内嵌的高层次综合工具,通过C、C++或SystemC对信号或数字处理进行建模,然后通过HLS转换成RTL模型,大大提高了FPGA开发效率,加速了FPGA在高性能数字信号处理领域的应用。

本文基于HLS设计FFT IP核,与传统实现方法相比降低了设计难度,缩短了设计时间,并便于优化处理以提高速度和资源利用率。

1 FFT原理

FFT是离散傅里叶变换DFT的快速算法。FFT算法可分为两大类,基于时域抽样法和基于频域抽样法。本文使用基-2时域抽样FFT算法,下面是该算法具体介绍。

1.1基-2时域抽样FFT算法原理

时域抽样法FFT处理N=2M的离散信号x(k),首先将变量k按奇偶分为两列,每列长度为N/2。

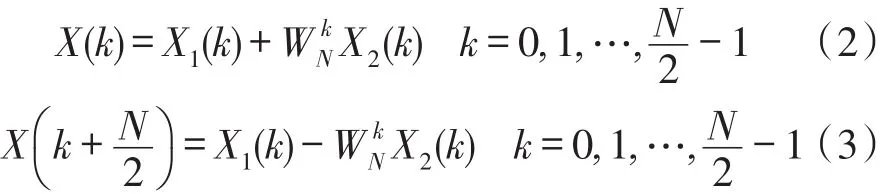

考虑X1(k)和X2(k)具有周期性,周期为N/2,同时旋转因子所以X(k)可以分解成前后长度为(N/2)的两段,其结果如下式所示。

上式是一次分解后FFT算法,对于N=2M点离散信号来说可以将其进行log2N次分解来实现FFT算法,也就是说该算法由M级碟形运算构成,每一级有N/2个蝶形运算。M级FFT算法其复乘次数为复加次数为NL=NlogN,与

3) 对景也从一个侧面体现出文化的渗透,它反映出特定阶级的思想文化与价值观念,它是一种符号、一种意象,记录了一座城市的历史.

2DFT算法相比复乘运算量大大减少,因此易于工程上实现[1-3]。

2 高层次综合工具HLS简介

Vivado HLS工具的应用突破了以往开发FPGA时采用HDL文本语言设计系统造成的瓶颈,通过C、C++或System C可以对信号或系统实现直接建模,是FPGA开发的一种全新的设计理念和想法。开发人员通过HLS开发工具完成以All Programma⁃ble SOC为基础、利用软硬件协同设计方式的产品开发。利用HLS设计工具对FPGA进行开发时效率就能够得到很大程度的提高,用户不再需要具有特别扎实的硬件知识和熟练HDL编程就能够建立数学模型,因此HLS在FPGA开发中将占据着重要的地位和实用价值,对数字信号的发展起到了极大的推动作用,加速了FPGA在高性能信号和数据领域的推广。这种方法能减少FPGA的开发时间,还可以在很大程度上利用已经存在的可靠软件代码。

基于Vivado HLS进行设计的流程图1所示,其中最关键的任务是利用C或C++语言编写一个具备特定作用的函数和适用该设计的测试平台,该平台可以检测搭建的系统的正确性和性能,然后再通过C仿真器对模型所具备的功能进行检验。若结果满足对设计提出的需求,便使用Vivado HLS工具把C模型转换为相应的RTL级模块[4-5]。有了RTL模块之后,就可以通过HLS内置的仿真器来检验建立的架构和功能。

图1 Vivado HLS设计流程图

3 FFT IP核设计

从FFT原理可以看出,旋转因子在计算中起着非常关键的作用。由于旋转因子可表示为为求旋转因子的值,必须计算正余弦函数值。在序列N很大的情况下,计算正余弦的运算量很大,直接影响FFT的运算速度,所以旋转因子的产生方式以及产生所占用的时间会直接影响整个运算速度[6-7]。

本文首先用MATLAB产生所将需要的旋转因子放在数组里存储,然后使用Vivado HLS工具实现FFT算法并封装成IP核。通过对存储器进行查找获取需要的旋转因子值,以存储空间来换取运算速度的的提高。

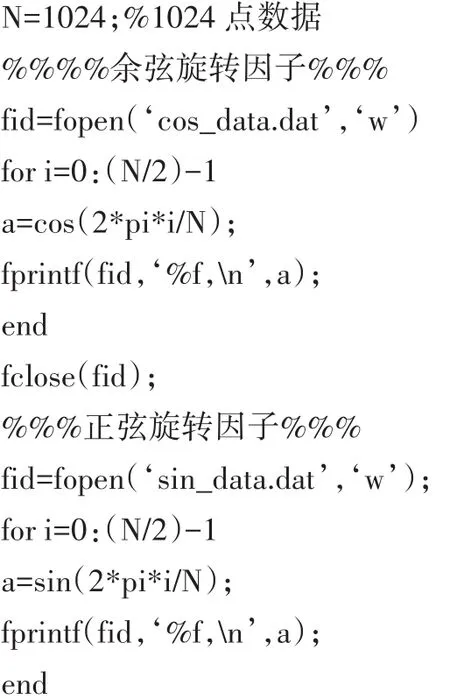

3.1旋转因子的生成

本文采用查表法,利用MATLAB软件生成所需要的旋转因子的正弦系数与余弦系数并将它们保存在文档中用于碟形单元计算,使以后计算1024点的FFT时可以直接调用,避免了进行碟形运算时才开始计算所需要的旋转因子,这样很大程度上减少计算复杂度节省了时间[10-12]。根据WN潜在的对称性,因而只需要计算N/2长度的WN系数值就足够,旋转因子的正弦部分写入到sin_data.dat文件中,余弦部分写入到cos_data.dat文件中,生成旋转因子的MATLAB代码如下所示。

3.2利用HLS设计FFT IP核

由于HLS可以运行C/C++/System语言,本文直接使用C语言完成FFT算法编程,并对FFT算法进行优化,使其性能与速度都有所提升,将FFT算法转换成硬件实现并创建FFT IP,供在Vivado中搭建音频频谱分析系统时使用。

(1)新建Vivado工程,利用Vivado HLS工具导入FFT设计的C源代码fft.c,头文件fft.h、旋转因子sin_data.dat和cos_data.dat。部分代码如下。

(2)导入共同的测试数据in.dat以及系统的测试程序fft_test.c。

(3)进行硬件配置,时钟周期选择10(ns),part se⁃lection选择为:Zedboard,芯片型号为xc7z020clg484。

(4)运行“Run C simulation”命令执行C仿真,测试FFT程序设计的正确性。在运行c仿真的过程中,Console(控制台)窗口内给出仿真过程相关的信息。图2所示的是0~1 023共1 024点数据经过FFT运算后在控制台打印的输出结果。在保证测试数据相同情况下,利用MATLAB自带FFT算法来验证所设计算法正确性,图3是调用MATLAB内自带FFT函数输出结果。通过对比分析由于精确度不一样,在允许范围内产生微小的误差,证明算法设计是正确的。

图2 控制台打印结果

图3 MATLAB仿真结果

(5)将FFT算法进行综合,综合成功后成功生成System C、VHDL、和Verilog格式的RTL文件。通过查看性能分析报告,Pipelined栏下面显示“no”表示循环没有实现流水线操作,访问存储器没有执行优化操作,因此此处实现的FFT算法并未达到最优。使用HLS工具可以从粗优化、精优化、总线化3个方面对设计进行优化,实现算法从串行运算到并行运算的转换,从而提高对数据的处理速度。优化完成后,对FFT算法再进行综合。

①粗优化命令。对copy2add、stage1_loop循环执行pipeline流水线操作命令,该命令的作用是使函数执行方式由串行执行变为全并行执行,对顶层函数fft进行dataflow数据流粗粒度优化操作。

②精优化命令。根据要处理数据的类型和位宽,进行优化,降低资源消耗。本次设计中输入数据为16 bit音频信息,因此可以将输入数据类型设置为uint16:即16 bit宽度的无符号整型数据,程序中的数据类型根据实际情况也设置成相应的类型。

③顶层函数的端口总线设置。为了提高对大量数据的处理速度,采用AXI4 Stream的方式来进行数据的处理,即CPU通过使用streaming方式直接和IP通信。

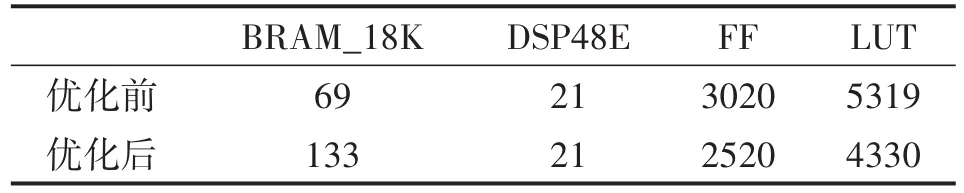

表1所示是运行FFT算法优化前后所占用的延迟和吞吐量信息,表2给出了该算法优化前后所占用的资源信息。通过观察可以看出1024点的FFT算法延迟时间经过优化之后大大减少,资源占用除了BRAM_18K增多,FF和LUT均减少了很多,最终提高了FFT算法性能和资源利用率。

表1 优化前后延迟和吞吐量信息

表2 优化前后资源占用情况

(6)将经过优化操作的FFT程序进行C/RTL联合仿真,测试生成的RTL代码的正确性,经过程序验证可以得出和用C仿真相同的结果,表明C语言实现的RTL代码是正确的。然后将生成的RTL代码以IP的形式导出,供接下来在FPGA上进行频谱分析时使用。

3.3HLS工具实现FFT IP核优势

使用Vivado HLS高级综合工具来实现FFT IP核优势在于大大减少工作量,缩短FPGA开发周期。我们仅需要用C、C++、System C等高级语言来完成FFT算法描述,HLS工具负责将算法转换成RTL级实现,将用高级语言描述的算法中的各个模块按照一定的规则和传统的硬件实现所需模块进行一一的映射,而以往FPGA实现FFT IP核时需要考虑5个模块即输入选择模块、存储模块ROM、存储模块RAM、蝶形运算模块、时序控制模块在硬件上如何实现,这使设计变得复杂而且对不熟悉硬件描述语言的工程师而言更为困难增加了工作量。

4 FFT IP核测试系统的搭建

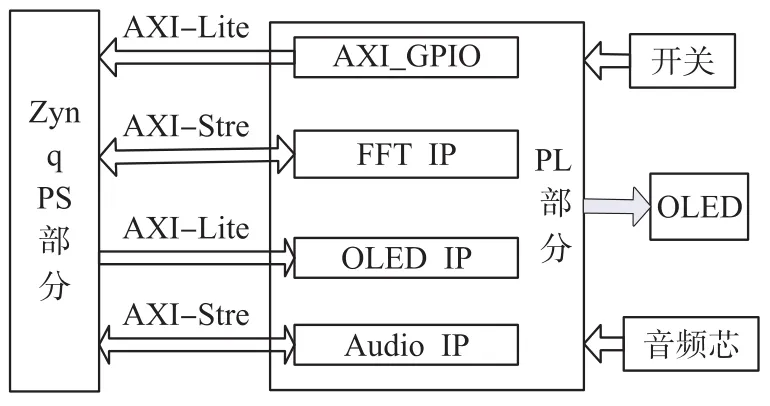

搭建一个完整的频谱显示系统,以测试FFT IP核的正确性。系统主要包含FFT IP核、用于显示的OLED IP核以及控制音频信号采集的Audio IP构成。对设计的各个子模块分别进行设计和验证,最终搭建出完整的系统。通过软硬件协同设计[8]这种方式设计并调试搭建的硬件系统和编写的控制程序,完成软件和硬件各自的设计之后,把两个部分结合起来协同调试系统,随机播放一段音频信号,并由音频输出接口得到随机的音频信息,在经过硬件PL部分的FFTIP实现频谱处理后传送到OLED进行频谱的实时显示。完整的能够实时显示随机音频频谱的硬件系统结构如图4所示。

图4 频谱显示系统结构图

整体系统的搭建是在Vivado环境中完成的,系统测试是以软硬件协同设计的思想来实现的。整个验证过程包括硬件部分和软件部分,硬件部分是在Vivado环境中搭建测试系统,软件部分利用Vivado设计套件提供的SDK工具编写频谱显示系统的驱动程序以及控制程序,然后是将硬件系统生成的比特流文件烧写至开发板中,利用软件编写的程序进行运行方式的控制。

4.1音频频谱显示系统搭建

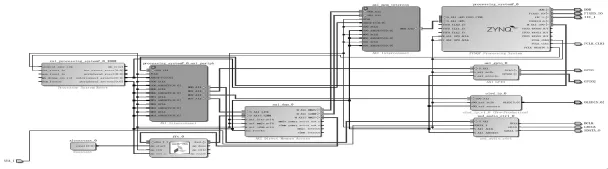

在Vivado开发环境下搭建整体系统,利用自己创建的FFT IP、OLED IP、音频IP以及Xilinx提供的IP来完成完整的频谱显示系统的搭建,将产生的比特流烧制Zynq系列的ZedBoard开发板上[9-10]。可以通过在OLED观察音频频谱来判断是否能够正确的测试所设计的系统。图5为使用自己设计FFT IP核搭建的音频显示系统。

图5 使用自己设计FFT IP搭建频谱显示系统

利用SDK软件将各个IP核的驱动模块统一起来,组成一个完整的系统,进行音频频谱信息的显示。

4.2系统测试及结果分析

在电脑上的播放器播放一段音频,通过耳机输出到开发板,经FFT IP核处理后在OLED上显示出音频信号的频谱图。图6为自己设计FFT IP核频谱分析结果。

图6 自己设计FFT IP频谱分析结果

结果表明使用HLS高层次综合工具设计的FFT IP能够完成对信号的频谱处理并输出频谱信息,说明HLS高层次设计工具在实际应用中能够发挥重大的作用,在已有IP不能满足设计要求时,不用使用传统HDL语言生成IP的方法,使用Vivado HLS工具进行算法设计优化生成RTL级模型最后以IP-XACT等多种可以让别的Xilinx工具识别并接受的类型格式输出并转化为IP的方式,可以显著的提高生产效率。

5 结束语

利用Vivado高层次综合工具HLS使用C语言进行FFT算法编程仿真优化并封装成IP核,充分体现了Vivado HLS的优势,为不熟悉HDL语言人员提供一种新的设计思路。另外,由于所设计的FFT IP核输入部分可以是实数,而且FFT IP核本身可以进行倒序输入顺序输出,因此与Xilinx提供的FFT IP核相比,不需要进行数据的前处理和后处理。

[1]王华英,于梦杰,刘飞飞,等.基于快速傅里叶变换的四种相位解包裹算法[J].强激光与粒子束,2013,25(5):1129-1133.

[2]杨晶,康宁,王元庆.基于低成本FPGA的FFT设计实现[J].电子器件,2013,36(4):506-509.

[3]陈天峰,师剑军,崔琼.基于数据重复的快速傅里叶算法改进[J].探测与控制学报,2013,35(5):79-82.

[4]James Hrica.利用赛灵思Vivado HLS实现浮点设计[J].今日电子,2013(1):34-38.

[5]徐家惠,戚海峰,高健,等.基于Vivado HLS的AC97音频系统设计[J].实验室研究与探索,2014,33(12):36-37.

[6]顾艳丽,周洪敏.基于FPGA的新型高速FFT算法研究与实现[J].电子器件,2008,31(4):1249-1251.

[7]陈丰,潘翔.基于FFT的矩形阵波束形成算法[J].传感技术学报,2006,19(6):2588-2590.

[8]唐守龙,刘昊,陆生礼,等.浅谈SoC设计中的软硬件协同设计技术[J].电子器件,2002,25(2):183-186.

[9]黄翔,王小华,黄学新.基于FPGA的频谱分析仪的设计与研制[J].微型机与应用,2011,30(24):20-22.

[10]Abdullah S S,Nam H,Mcdermot M,et al.A High Throughput FFT Processor with no Multipliers[C]//Computer Design,2009. ICCD 2009.IEEE International Conference on.IEEE,2009:485-490.

[11]Xiao X,Oruklu E,Saniie J.Reduced Memory Architecture for CORDIC-Based FFT[C]//Circuits and Systems(ISCAS),Proceed⁃ings of 2010 IEEE International Symposium on.IEEE,2010:2690-2693.

[12]Malashri A,Paramasivam C.Low Power and Memory Efficient FFT Architecture Using Modified CORDIC Algorithm[C]//Infor⁃mation Communication and Embedded Systems(ICICES),2013 International Conference on.IEEE,2013:1041-1046.

张俊涛(1966-),男,汉族,陕西西安人,教授,硕士生导师,研究方向为软件无线电、信号与信息处理、EDA技术及应用;

付芳琪(1990-),女,山西运城人,硕士研究生,研究方向为信号与信息处理、EDA技术及应用,1297412322@qq.com。

Design and Implementation of FFT IP Core Based on Vivado HLS

ZHANG Juntao*,FU Fangqi,CAO Mengna

(Shaanxi University of Science and Technology Institute of Electric and Information Engineering,Xi'an 710021,China)

A new method of designing FFT IP core based on Xilinx high-level synthesis tool HLS is studied,and a audio spectral display test system is built for testing the FFT IP core.First twiddle factors of 1 024-point FFT algo⁃rithm aregenerated with MATLAB.Then FFT algorithm program written in C language is integrated into the IP core and is optimized twice.Compared with the previous optimization the delay time has saved 19%to 40%,LUT re⁃sources have saved 18.5%.The test result shows that FFT IP core successfully implements spectral analysis of the audio signal.

high-level synthesis;FFT;IP core;design;spectrum;test

TN851

A

1005-9490(2016)02-0374-05

EEACC:614010.3969/j.issn.1005-9490.2016.02.026

2015-06-02修改日期:2015-07-14