基于FPGA和ADV212的图像实时压缩系统设计

2016-10-13张会新曹翱翔胡海风孙宝海

张会新,曹翱翔*,胡海风,孙宝海

(1.中北大学仪器科学与动态测试教育部重点实验室,太原030051;2.电子测试技术重点实验室,太原030051)

基于FPGA和ADV212的图像实时压缩系统设计

张会新1,2,曹翱翔1,2*,胡海风1,2,孙宝海1,2

(1.中北大学仪器科学与动态测试教育部重点实验室,太原030051;2.电子测试技术重点实验室,太原030051)

设计了一种基于FPGA和ADV212为核心的图像数据实时压缩系统。该系统采用LVDS传输图像数据,利用FPGA为主控单元完成图像数据的接收,以及对ADV212的模式配置,数据写入,读取并把压缩数据实时上传到上位机,经过实际测试,该系统处理速度高,压缩较好,失真度小,具有较高的实用价值。

电子技术;图像压缩;FPGA;ADV212;LVDS

随着航天技术的发展,测量功能越来越完善,传输的数据量也越来越大,对无线传输带宽的要求越高。遥感图像是测试领域的一个重要技术之一,随着分辨率的提高,数据量越来越大,这样占用的带宽就越多,为了缓解带宽的压力,提高遥测系统无线带宽的利用率[1,2],本文提出并设计了一种图像实时压缩系统,该系统是以FPGA为逻辑控制核心,利用硬件压缩芯片ADV212实现图像压缩,具有实时性好,操作灵活,速度快、可靠性高、压缩比可以灵活调整等优点。该系统很好地解决了无线传输带宽较小与原始图像数据较大之间的矛盾。

1 系统总体设计

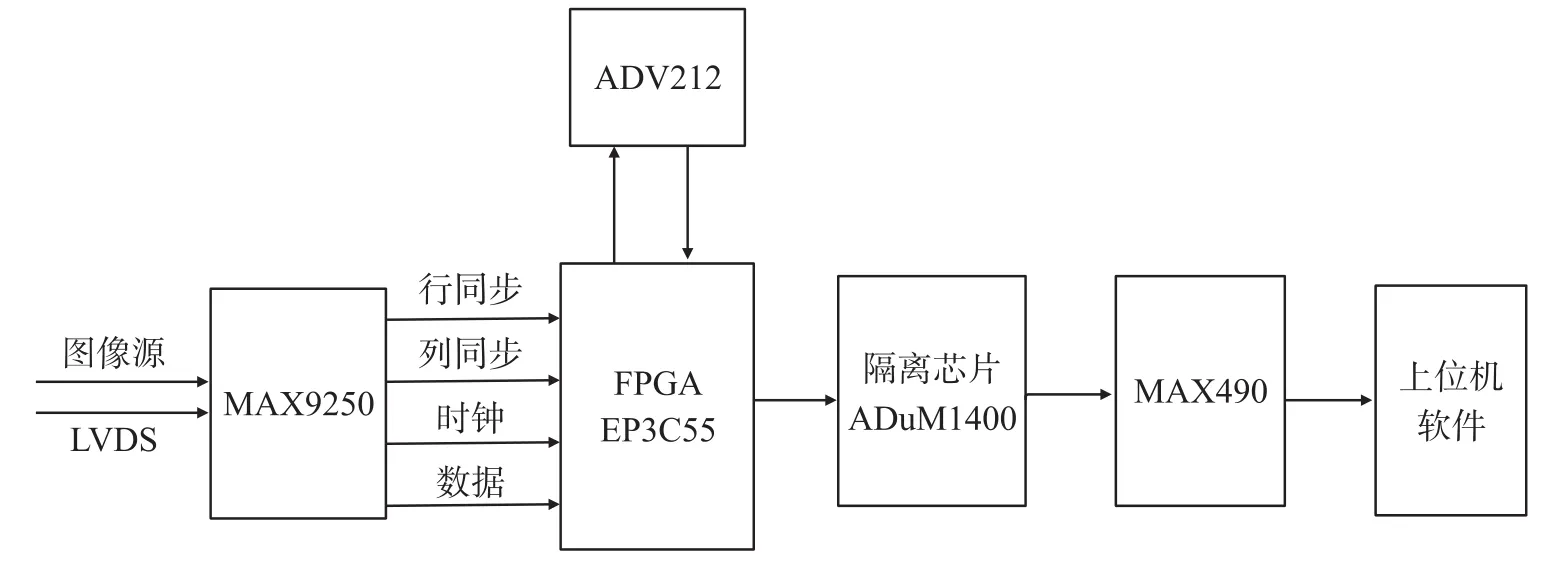

该系统能够把前端摄像头发送的图像数据接收下来并实时压缩通过422接口传送出去,最终通过上位机软件显示出来。图1为该系统的结构图。先通过LVDS解码芯片MAX9250,将前端摄像头已经处理成LVDS信号的图像源解码出来,FPGA通过判别图像数据帧头来识别图像的有效数据,将图像数据写入用来缓冲的FIFO中,然后再从缓冲中读取图像数据写入视频压缩芯片ADV212中,经过压缩后再把压缩的数据通过RS422接口实时的上传到上位机,并显示出来。

图1 系统结构图

2 系统软件设计

系统软件实现主要是通过在FPGA内编程实现,主要分为图像接收模块,图像压缩模块,数据传输模块3个功能模块。

2.1图像接收模块

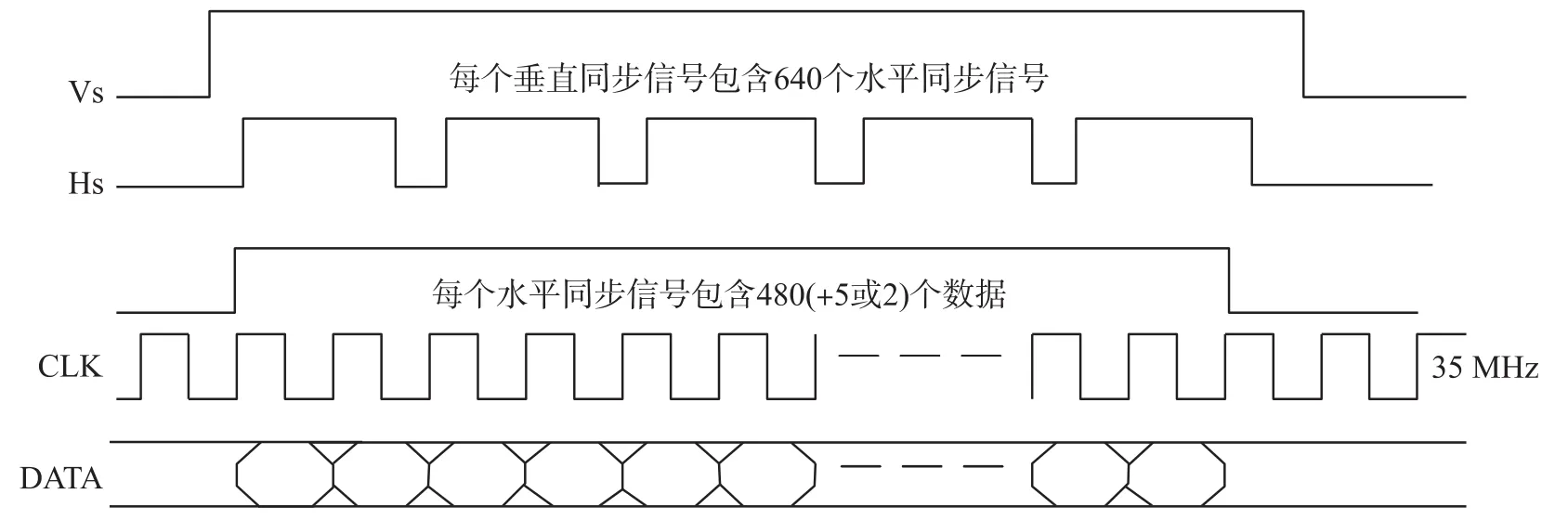

图像源的时序如图2所示,其中包括垂直同步信号Vs,水平同步Hs信号,时钟信号,图像数据。图像源的帧率为25帧/s,周期为40ms,图像尺寸为640×480×8 bit,每个垂直同步下面包含640个水平同步,每个水平同步下面包含480个时钟,其中第一个水平同步另包含帧头(55AAFAF900),最后一个水平同步包含帧尾(F9FA),时钟频率为35 MHz。

图2 图像时序图

数据接收过程中,为了确保每次能正确的把图像数据写进后面的缓冲FIFO中,则在写入FIFO之前首先通过数据比较器在图像数据中找到图像帧头55AAFAF900,然后使能后面的FIFO,把后面的图像数据写入到FIFO中。由于图像数据为8 bit,而ADV212的数据端口设置的为32 bit,在此设置的FIFO为32 bit,则在图像数据写入FIFO之前需要把4个数据转化为1个32 bit,这样图像的速率由35 MHz变为8.75 MHz。

2.2图像压缩模块

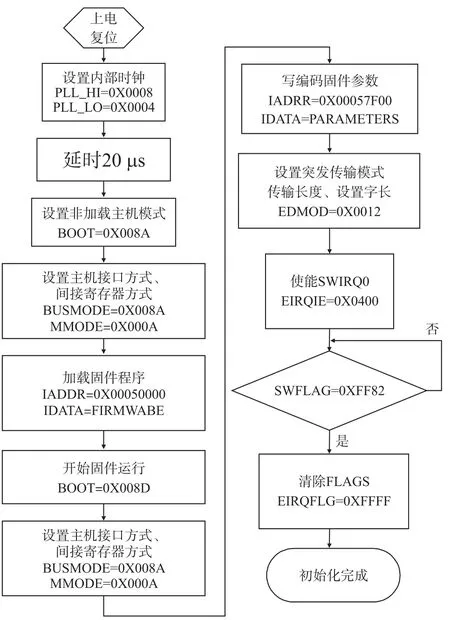

图像压缩模块是本系统的核心模块,该系统中使用专用的图像硬件压缩芯片ADV212,是ADI公司在2006年发布的一款专用图像压缩芯片,延迟小,功耗低,成本低,工作模式可以通过内部寄存器灵活配置,可以对静止图像和多种视频进行压缩处理[3,4]。ADV212的工作模式在上电后配置,初始化过程如图3所示。

该压缩模块使用的是encode模式,设置的MCLK为25MHz,JCLK经过4倍频为100MHz,压缩比为1∶48。为了充分的利用ADV212的速度,使用突发批量读写模式,设置的数据接口为32,缓冲深度为128,由于每帧图像的尺寸为640×480 pixel= 307 200 pixel,像素位数为8 bit,则需要写入600次,每次写入128个。

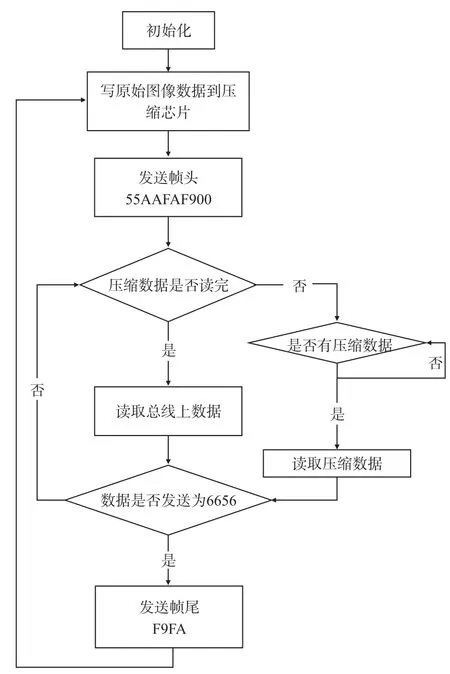

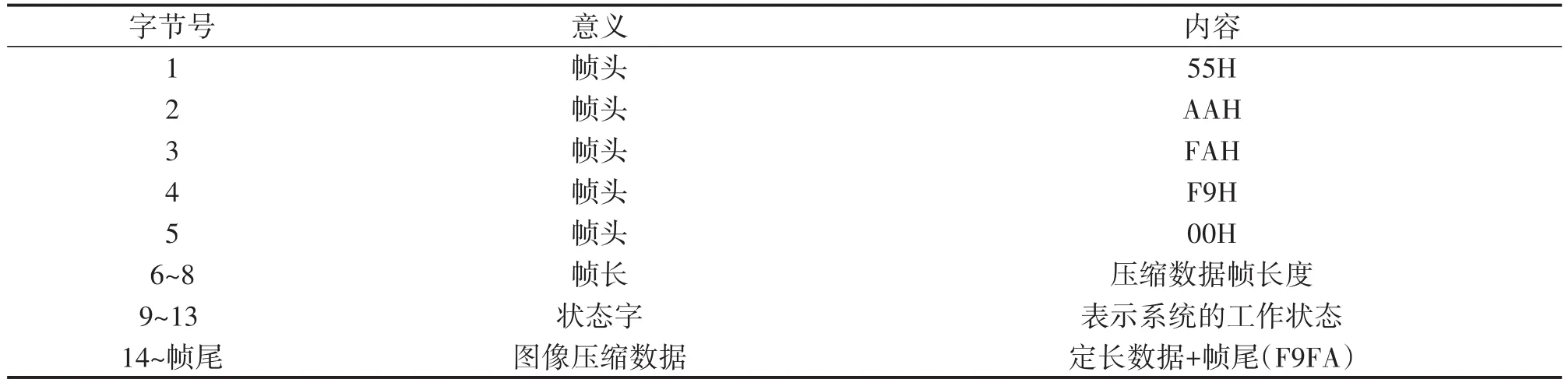

压缩图像的输出格式如表1所示,在读取每帧压缩数据之前,首先发送帧头55AAFAF900,压缩数据的长度,状态字,然后再发送压缩数据,如图5所示。由于针对不同的输入图像,压缩出来的数据长度有可能不一致,所以在读取压缩数据之前首先的判断当前帧的压缩数据是否已经读取完毕,如果没有读取完毕,则继续读取压缩数据;如果读取完毕,但不够每帧需要发送的数据,则继续把总线上的数据发送出去,保持传送的压缩数据包能够保持一定,压缩数据发送完毕完毕后,发送帧尾F9FA。数据压缩流程如图4所示。

图3 初始化流程图

图4 数据压缩流程图

表1 压缩图像输出帧格式

图5 测试数据

2.3数据传输模块

数据传输模块主要是把前端的压缩模块送出来的数据转化为异步串行数据,RS422接口的传输码率为2.4576 Mbit/s,起始位为1位,数据位8位,无奇偶校验位,停止位1位,数据连续的输出,周期为40 ms,每帧的最大传输数据量为40 ms×10-3×2.457 6×106/10=9 830,而压缩后的数据量和帧头帧尾共有6 671 byte,则能够满足传输要求。

3 系统测试及结论

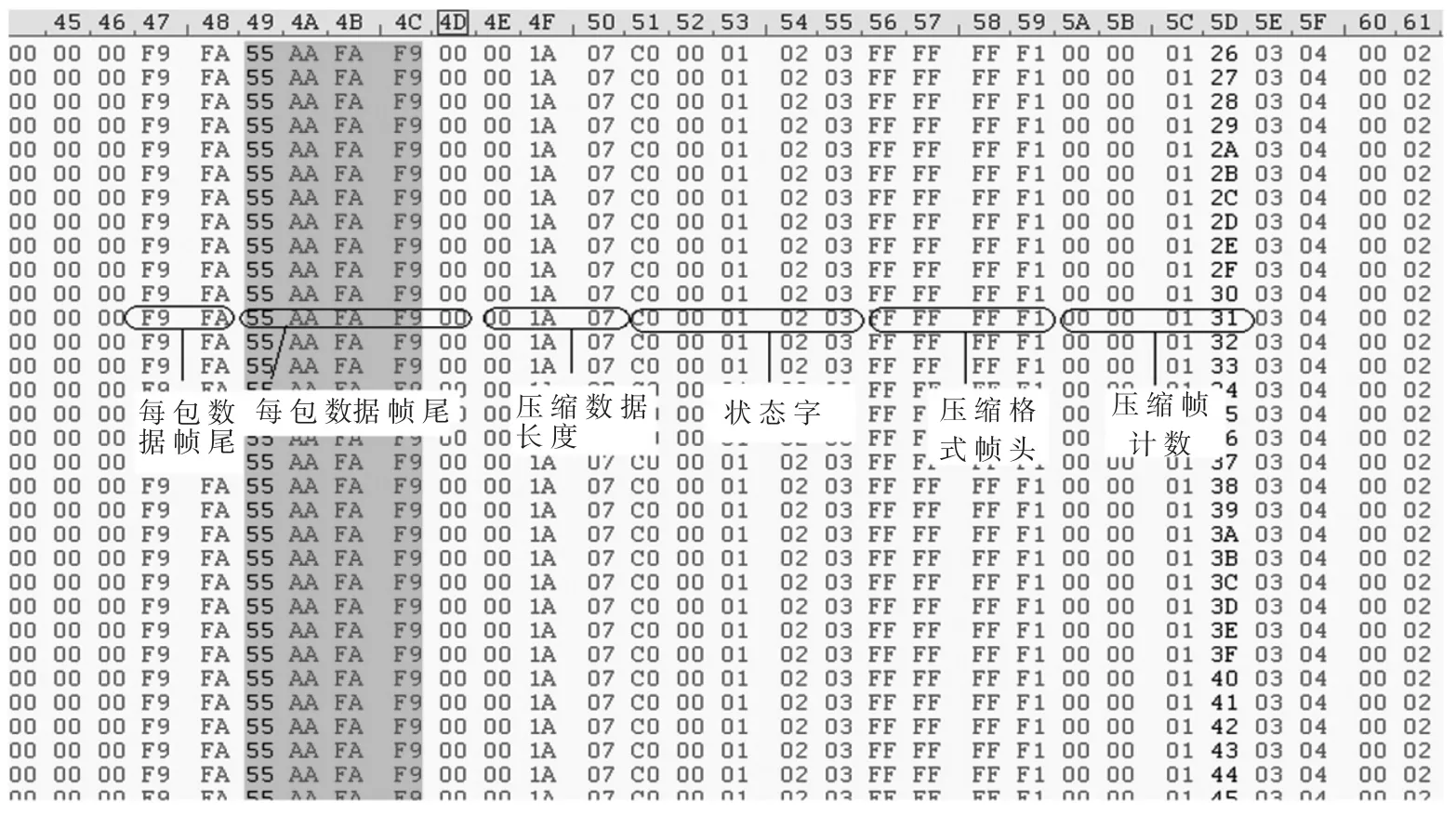

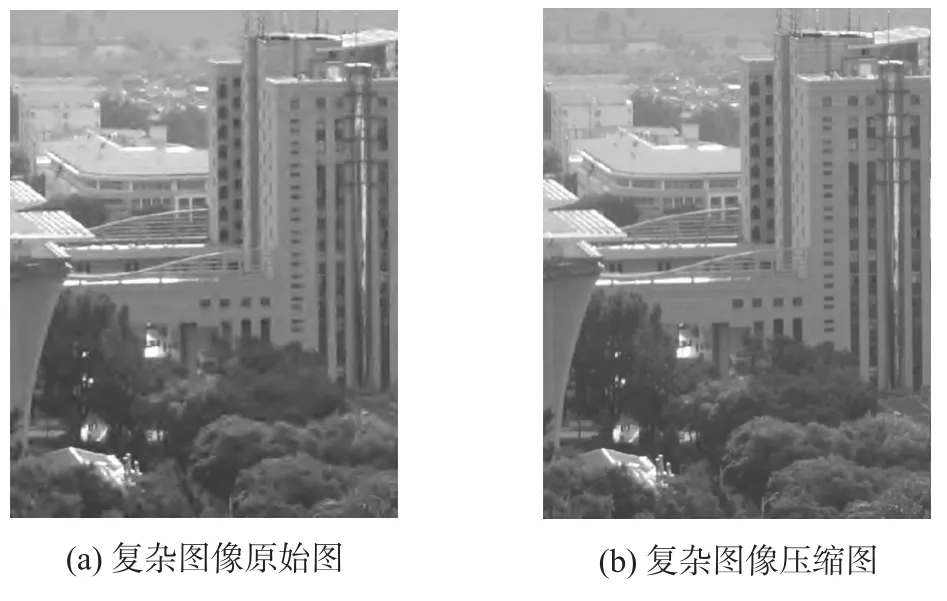

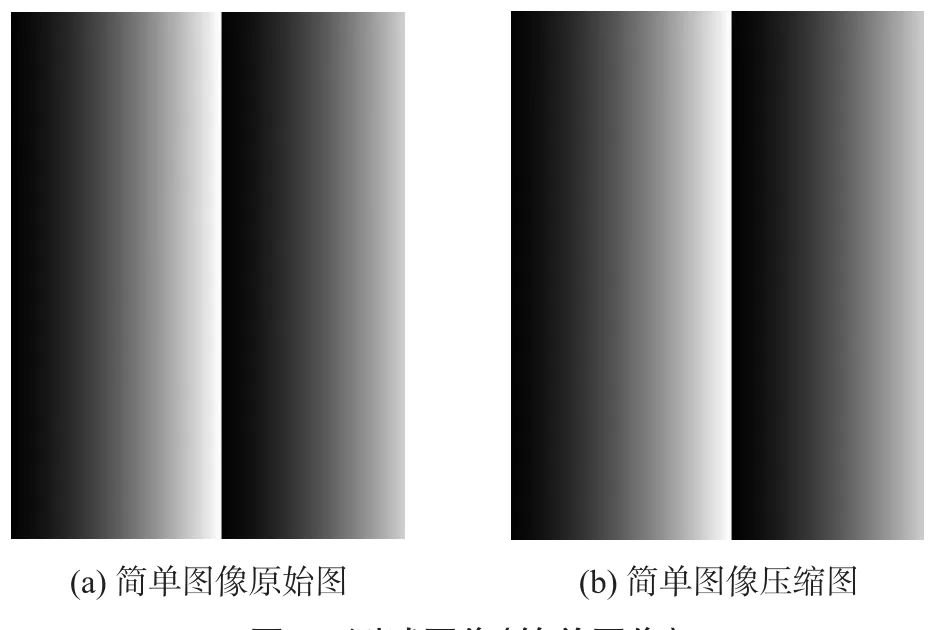

整个系统设计完成后,把前端发送的图像数据经过压缩模块压缩后,上传到上位机,用MTALAB软件编写图像显示软件显示压缩的图像,图6(a)、图7(a)为原始图像,图像尺寸为300 kbyte,图6 (b)、图7(b)为压缩后的图像,图像的尺寸大小为6.5 kbyte,实现的压缩比约为46:1,极大的减少的图像尺寸,为数据传输节约了带宽,从而保证的图像传输的实时性。测试表明,本文研究了一种基于ADV212的图像实时压缩系统,该系统能够可靠压缩前端摄像头传送的图像数据,处理速度快,压缩效果较好,失真较小,能够满足系统的要求。

图6 测试图像(复杂图像)

图7 测试图像(简单图像)

[1]薛旭成,张淑艳,李洪法,等.基于ADV202的遥感图像实时压缩系统设计[J].微电子学与计算机,2008,5(5):197-199.

[2]刘永征,刘学斌,胡斌樑,等.基于ADV212的JPEG2000静态图像压缩系统设计[J].电子器件,2009,6(3):504-508.

[3]袁宇望,卢亮.实时图像压缩存储系统的发展和应用[J].光电子技术,2005,6(2):113-116.

[4]张海江.遥测图像压缩系统的设计与实现[J].通信技术,2011,10(44):66-68.

[5]朱元元,刘成国,徐刚.基于FPGA的实时静态图像压缩系统设计[J].导弹与航天运载技术,2013,332(3):79-82.

[6]冯伟昌,林玉驰.基于FPGA的双通道实时图像处理系统[J].传感技术学报,2010,23(8):1118-1122.

[7]陈曦,高俊峰.压缩比可变的分块自适应量化算法的FPGA实现[J].电子器件,2007,30(4):1444-1450.

[8]韩志军,刘文怡,王浩,等.基于DSP的实时数据无损压缩实现[J].电子技术应用,2008,11(11):45-47.

张会新(1980-),男,汉族,黑龙江牡丹江人,讲师,北京航天航空大学在读博士,研究方向为抗过载存储技术及动态测试技术与仪器,zhanghx@nuc.edu.cn;

曹翱翔(1989-),男,汉族,安徽肥东人,研究生,研究方向为电子与通信工程,caoaoxiang@qq.com。

A Design of Real-Time Image Compression System Based on FPGA and ADV212

ZHANG Huixin1,2,CAO Aoxiang1,2*,HU Haifeng1,2,SUN Baohai1,2

(1.Key Laboratory of Instrumentation Science&Dynamic Measurement,Ministry of Education,North University of China,Taiyuan 030051,China;2.Education Science and Technology on Electronic Test&Measurement Laboratory,Taiyuan 030051,China)

The design of real-time image data compression system is based on FPGA and ADV212.The system takes advantage of LVDS to transmit image data and uses FPGA to receive the image data for the main control unit. At the same time,the system can configure the mode of ADV212,write the data and read the compression data to upload to PC.After the actual test,the processing speed of the system is more efficient,the compression effect of the system is better and the distortion of image is less.The system has a greater practical value.

electronic technology;image compression;FPGA;ADV212;LVDS

TP274

A

1005-9490(2016)02-0483-04

EEACC:722U10.3969/j.issn.1005-9490.2016.02.047

2015-03-12修改日期:2015-07-17