基于FPGA的全数字锁相环电机调速系统设计

2016-10-09陈欢

陈 欢

(无锡科技职业学院,214112)

基于FPGA的全数字锁相环电机调速系统设计

陈欢

(无锡科技职业学院,214112)

数字锁相环具有抗干扰能力强、锁相效果好等优点。而电机锁相控制系统调速精度高,易于用程序实现。本文介绍了一种基于FPGA的数字锁相环,用于电机调速系统的设计。

锁相环;FPGA;鉴相器;滤波器

0 引言

“锁相”概念的出现源自于对同步问题的研究,由荷兰科学家C. Huygens提出。法国科学家DeBellescize在1932年发表了对锁相环路的数学建模,并提出了同步检波理论,锁相技术的理论才得以初步发展和确立。模拟锁相环和后来出现的模数混合锁相环均存在固有缺陷,对噪声敏感,造成电路的抗干扰性能较差,影响电路设计的品质。随着数字电路技术的发展,数字锁相环不仅解决了模拟锁相环存在的器件饱和、零点漂移以及易受环境和电源的温度变换影响等缺点,还具备实时处理离散数据的能力。全数字化锁相环必将是未来发展的趋势。电动机锁相控制系统具有调速精度高、给定信号精度高和易于程序实现和计算机控制等优点。本文在数字锁相环和电机控制理论的基础上,对全数字锁相环调速系统进行探究,确定了由FPGA片内资源产生PWM参考波,用鉴相器、变模K加减计数器实现环路滤波器、脉冲加减电路和N分频电路,以此构成数控振荡器全数字锁相环。

1 全数字锁相环电机调速系统设计

1.1概述

全数字锁相环包含四个模块,鉴相器,K变模可逆计数器、脉冲加减电路、模N分频器。K变模可逆计数器起环路滤波器的作用,其滤波原理是通过设置一个门阀值进行滤波;脉冲加减电路和模N分频器相当于锁相环PLL中的频率振荡器。全数字锁相环通过脉冲计数器来实现,从而达到全数字的设计要求,只有计数器的实现还远远不够,还需要同步脉冲控制来实现。同步控制是全数字锁相环控制系统实现的关键。整个系统是在系统时钟的控制下,进行计数器计数的量化,将模拟信号转换成数字量。

1.2数字鉴相器

数字鉴相器用计数器实现,将输入参考信号和反馈信号的相位差Фe=Фin-Фout,经鉴相后输出包含相位误差信息的波形Se,控制K变模可逆计数器的计数方向。当环路锁定时,Se的输出是占空比为50%的方波,即输出的绝对相差为π/2。

1.3K变模可逆计数器

K变模可逆计数器滤除异或鉴相器输出Se的相位误差中的高频信号分量,促进环路性能稳定。Se输出信号控制K变模计数器的加减运算。当Se为高电平时,计数器会执行减运算,若计数器减为零时,就会输出BORROW信号即脉冲借位脉冲控制信号给脉冲加减电路;当Se为低电平时,加计数器会相应的执行加运算,若是计数的结果达到计数器预先设定的模值,就会输出进位脉冲CARRY信号。

可逆计数器的模的大小和数字锁相环的性能有直接关系,数字锁相环的跟踪步长由模的大小来决定。模值越小,跟踪步长会反方向变化越来越大,锁定时的相位误差就会越大,但是捕获时间会变短;模值越大,跟踪步长越小,相应的相位误差会变小,但信号捕获时间变长。可逆计数器的模是2的N次幂,由输入四位

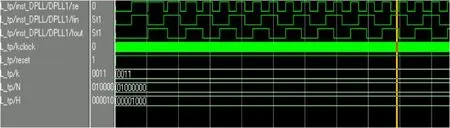

图1 全数字锁相环Modelsim仿真图

二进制信号K预设,当K的取值在0001~1111时,相应的模的变化范围为23~217。

在锁相环同步锁定的状态下,鉴相器的输出没有超前或滞后脉冲的输出信息,这意味着K计数器正常情况下是没有输出的;从而避免噪声对锁相环的误控作用,增强了系统抗噪能力。K值的适当取值对于环路的稳定性能也很重要。K值取得大时,少量噪声的干扰不会让计数器计满,因此也不会产生进借位脉冲。但是大的K值会造成捕捉带变小,加大环路捕获时间。反之,K值取得小,虽然可以加快环路的锁定,但是K计数器会较为频繁的产生脉冲控制输出信号,降低环路对噪声的抑制能力。

1.4数控振荡器

数控振荡器由脉冲加减电路和除N计数器构成,实现对输入参考信号频率和相位的跟踪及调整。本文的脉冲加减电路通过JK 触发器和D 触发器的组合来实现。当锁相环路进入锁定状态时,加减脉冲电路相当于二分频的分频器,此时锁相环电路并不会产生进位或者借位的脉冲信号。当有进位信号时,加减脉冲电路的功能不仅会将信号二分频,而且会在信号中加入半个时钟周期脉冲,以期提高输出信号的频率,减小与输入参考信号的相差。当有借位信号传入,输出信号的频率会降低,即输出信号中会减去半个时钟周期的脉冲。脉冲加减控制通过这种方式进行相位调节,最终实现闭环系统的相位锁定。考虑到实际电路中的延时,可能会有毛刺信号出现在逻辑输出信号中, 进而导致锁相环的误控或是锁相环锁相出现问题,鉴于毛刺信号可以在时钟控制下的D触发器弱化消除,因此脉冲加减电路用JK 触发器和D 触发器实现。

图1为全数字锁相环Modelsim仿真图,可以看出经过一段时间,相差锁定在90度。

2 结论

本文设计了一种全数字锁相环,用于电机速度控制,锁相效果较好。

[1] 魏建玮,高迎雪. 锁相环技术综述[J]. 科技信息职教与成教,2008,36

[2] Thomas Olsson.A digitally controlled PLL for So Capplications[J].IEEE Journal of Solid State Circuits,vol.39,No.5,May 2004.

[3] Ching-Tsai Pan,Fang,E.A Phase-Locked-Loop-Assisted Internal Model Adjustable Speed Controller for BLDC Motors[J].IEEE Journals, 2008, Page(s):3415-3425

[4] 肖龙,杨佩君,汤恩生. 基于软件锁相环的电机速度控制系统[J]. 航天返回与遥感,2006,27(3).

[5] 黄保瑞,杨世平. 基于 FPGA 的全数字锁相环设计[J]. 电子测试-微处理器与可编程控制器,2014.

Digital Phase-locked Loop Motor Speed Control based on FPGA

Chen Huan

(Wuxi Vocational College of Science and Technology,214112)

Digital phase-locked loop has the advantage of anti-interference and well phase-locked. Meanwhile,there is high accuracy in motor phase-locked control system which can be achieved by program. This paper presents an digital phase-locked based on FPGA so as to control the speed of the motor.

Phase-locked Loop;FPGA;Phase Detector;Filter