TFT阵列基板的电容充电电路的设计

2016-10-09徐永先

徐永先

(北京电子科技职业学院,100176)

TFT阵列基板的电容充电电路的设计

徐永先

(北京电子科技职业学院,100176)

液晶显示器尺寸越来越大,液晶栅极启动信号持续时间变短,液晶电容和存储电容的充电时间也随之减少,导致对液晶电容和存储电容充电不充分,造成横向微弱亮线的产生,使得画面品质下降。本文设计出TFT阵列基板电容充电电路,在当前行像素显示时,对下一行像素预充电,解决了液晶电容和存储电容充电不充分的问题。

TFT阵列基板;电容充电电路

从制造的角度来看液晶面板的话,可分为TFT阵列工序、液晶单元工序、液晶模块工序三类。在这些液晶面板制造工序中,尤其是TFT阵列工序决定液晶面板的显示性能,对面板制造成本的影响尤为突出。TFT阵列是对液晶进行驱动的电路基板。TFT和显示像素电极被排列在玻璃基板上,用于驱动TFT的栅极布线、输送加载在像素上的电压信号的信号布线纵横交错。

1 现有技术

在TFT LCD显示中,在屏的横向电极上输入扫描信号,输入的电压加在TFT的栅极上控制TFT的开关状态,而在纵向电极上输入显示数据电压信号,其信号电压加在TFT的源极上,提供显示图像所需的像素电压。而液晶电容一端接在TFT的漏极,电容的另一个极板是对面玻璃基板上的电极,即公共电极,它是同驱动电路的COMMON电压输出端连接在一起的。除了液晶电容外,为了克服在像素点上的电压的波动,要做出一个跟像素电容并联的一个电容,称为存储电容。存储电容的另一个电极可以利用栅线做出一个电容。当Gate电极送入扫描信号,打开像素上的TFT的同时,源驱动器Source Driver送入数据图像信号通过TFT向像素电容充电。当这一行扫描过后,TFT关断,像素电容保持这个电压。

栅极启动信号都要持续一段时间,这样有可能发生当前行的所有像素的TFT开关还是开启状态的时候,下一行的所有像素的TFT开关也被开启,数据信号同时加载到两行像素上,导致显示异常现象。现有技术的解决方法是减少栅极启动信号的持续时间,在下一行栅极启动信号来临前提前关闭当前行栅极启动信号,这样就保证了两个栅极启动信号不会有重叠的持续时间,避免了显示异常。但是也带来问题:每个像素可以等效成电阻和电容组成的充电电路,这个充电电路的充电时间和电阻、电容有关。电阻电容乘积越小,充电越快。如果要把电阻、电容变小,将对整个面板做巨大的改动,时间、金钱、人力都会有很大的损失。所以要采用新的设计,在栅极启动信号持续时间缩短的情况下,像素的液晶电容和存储电容也能充分的充电,不会有充电不充分产生横向微弱亮线,画面品质下降的后果。

2 改进的TFT阵列基板电容充电电路

本文提供一种新的TFT阵列基板,使得液晶电容和存储电容在栅极启动信号持续时间缩短的情况下也能够得到较充分的充电。如图1所示:

图1 改进的TFT阵列基版电容充电电路

图中水平的直线是栅极扫描线,用来提供栅极启动信号。垂直的直线是数据扫描线,用来给像素提供充电电压。栅极扫描线和数据扫描线通过TFT开关相连,TFT的栅极与栅极扫描线相连,源极与数据扫描线相连,漏极与液晶电容和存储电容的一端相连。液晶电容和存储电容相并联,另一端和公共电极之间有一电压Vcom。以上所描述的是当前技术单一像素的电路结构。

本文提出的设计又增加了TFT1、TFT2两个开关以及一个预存储电容CA。TFT1开关的栅极和源极与当前栅极扫描线Gate N相连,漏极与预存储电容的一端相连,预存储电容的另一端和公共电极之间有一电压Vcom。TFT1与预存储电容相连处引出一条导线,同TFT2的源极相连。TFT2的栅极与下一行栅极扫描线Gate N+1相连,漏极同下一像素TFT开关的漏极相连。这一设计应用到每一像素当中。

该电路的工作原理如下:当前行的栅极启动信号到来时,这一行像素的TFT开关都被打开,通过数据扫描线提供充电电压。因为TFT1的栅极、源极都和当前行的栅极扫描线相连,因此当前行的栅极启动信号到来时,TFT1开关打开,源极和漏极导通,通过当前行的数据扫描线给预存储电容充电。当前行的栅极启动信号关闭后,预存储电容留有一定的电压,TFT1关闭,预存储电容同当前栅极扫描线断开。下一行的栅极启动信号到来时,下一行像素的TFT开关都被打开,通过数据扫描线提供充电电压。因为TFT2的栅极同下一行的栅极扫描线Gate N+1相连,TFT2开关和下一行像素的TFT开关同时被打开,源极和漏极导通,预存储电容和数据扫描线同时向下一行像素的液晶电容和存储电容充电。当前技术单一像素的电路结构,像素只能由数据扫描线给充电。而本文提出的电路,在当前行像素充电时,也在给预存储电容充电,在扫描到下一行像素时,在数据扫描线充电的同时,预存储电容也在参与充电,故而像素电极能够快速地完成充电,保证液晶电容和存储电容充电足够充分,减少横向微弱亮线的产生,提高显示画面的品质。与改变TFT基板的电阻、电容相比,本文提出的设计更容易实现。

3 仿真验证

为了验证设计的正确性,用Multisim软件进行仿真。

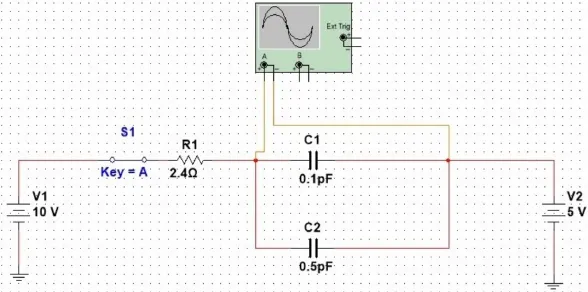

未加预存储电容时仿真原理图如图2。像素中的液晶电容建模为0.1pF的电容,存储电容建模为0.5pF的电容,两个电容并联连接。数据扫描线的电阻建模为2.4Ω的电阻,和两个电容一端串联。Vcom电压取值为5V,建模为一个5V的直流电压源,和两个电容另一端串联。数据线上的信号是方波,但是本文要验证的只是数据线上刚出现波形时像素的响应情况,因此把数据线上的信号建模为一直流源,电压的大小对应于方波的最大电压,即L127灰阶时的电压,取值10V,通过一个开关连接到数据扫描线的电阻上。

然后在两个电容的两端连接示波器,观察波形的上升沿。开关闭合后,像素迅速充电,从初始-5V的电压上升到+5V的电压所需的时间为9.95us。接下来把预存储电容加到电路中,见图3。

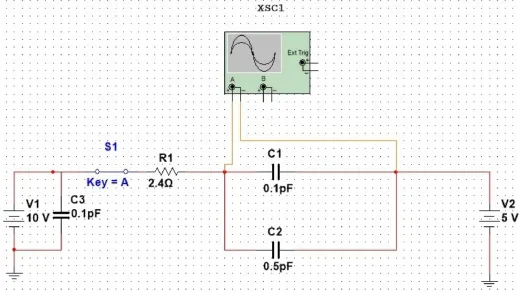

预存储电容和液晶电容、存储电容的大小相当,本文中把它建模为0.1pF的电容。因为预存储电容在上一行像素显示的时候就已经充电了,因此,把它和10V的直流源并联,开关打开,10V

图2 未加预存储电容

图3 加入预存储电容

的直流源就对它提前充电。开关闭合后,就是对当前行的像素充电。10V的直流源和充了电的预存储电容同时对像素充电,和之前相比,多了个预存储电容参与充电,因此充电时间会在一定程度缩短。

加入预存储电容后,从初始-5V到+5V的充电时间缩短了,为9.34us。和之前9.95us相比,缩短了0.61us。因此可以看出加入预存储电容后,像素的充电时间可以一定程度的缩短,因此本文中提出的设计有一定的效果。

4 结束语

通过仿真可以看到本设计的效果。但是本文只对一个像素进行了设计和仿真,并没有对整行甚至整个液晶屏的像素进行设计和仿真。因此后续的工作还要以本文的成果为依据,继续对整个液晶屏进行设计和仿真,来获得更大的成果。

[1]颜重光.TFT-LCD背光设计策略[J]电子产品世界.2005.14

[2]张春兵.快门式3D显示中信号驱动方法与3D串扰的研究[J]液晶与显示.2013.04

[3]林鸿涛.TFT-LCD中驱动信号对线残像的改善研究[J]液晶与显示.2012.03

徐永先,1978年4月,男,北京电子科技职业学院,助理实验师,硕士。研究方向:电子与通信。

TFT array substrate capacitor charging circuit design

Xu Yongxian

(BEIJING POLYTECHNIC,100176)

The LCD size becomes more and more large and the LCD gate startup signal duration becomes shorter.The charging time of liquid crystal capacitor and storage capacitor becomes shorter.So it causes inadequate charging of liquid crystal capacitor and storage capacitor and causes appearance of faint light lines.The picture quality declines.This paper has designed a TFT array substrate capacitor charging circuit.When the current line of pixels are displaying,it pre-charges the next line of pixels, solving the inadequate charging problem of liquid crystal capacitor and storage capacitor.

TFT array substrate;Capacitor charging circuit