一种IRIG-B码解码器的设计与实现

2016-09-19余飞侠范晓东

陈 伟,王 宇,余飞侠,范晓东

(安徽四创电子股份有限公司,安徽 合肥 230031)

一种IRIG-B码解码器的设计与实现

陈伟,王宇,余飞侠,范晓东

(安徽四创电子股份有限公司,安徽合肥230031)

针对现有靶场仪器组串行时间码解码器解码精度低、工作稳定性差等问题,将微处理器与现场可编程门阵列相结合,提出一种新的解码器实现方案:采用最新的片上系统控制器,在其内部配置了微处理器系统及可编程逻辑单元;串行时间码码元识别由相应的硬件逻辑单元控制,保证已识别的秒脉冲边沿精准;微处理器系统控制已识别的时间码流的解码及输出,由此节省了硬件资源、提高了解码效率;最后通过现场运行及仪器监测证明该方案串行时间码解码精度和稳定性优于现有解码技术,其授时精度能够满足时间同步的要求。

片上系统控制器;现场可编程门阵列;微处理器;靶场仪器组串行时间码

0 引言

美国靶场间仪器组(inter-range instrumentation group,IRIG)提出了靶场仪器组串行时间码(B type format of IRIG,IRIG-B)[1],广泛应用于时间信息传输系统中。IRIG-B码具有世界通用、接口标准化、适用于远距离传输等特点。在我国,工业控制、通信、气象、航天、电力系统测量与保护等领域的测试设备均采用IRIG-B国际时间标准作为时统设备的时间同步标准[2-3],并制定了相应的国军标。目前国内的IRIG-B解码采用的核心控制器大都为现场可编程门阵列(field-programmable gate array,FPGA),资源消耗量大、解码精度低、工作效率和稳定性差;因此需要有由更高效的控制器、有效的解码算法实现即插即用、授时精度高及运行稳定的新型解码器。SmartFusion2系列芯片是Microsemi公司的最新65 nm工艺的片上系统产品,,是基于Flash架构FPGA发展而来,内部集成166 MHz的Cortex-M3硬核处理器,不占用FPGA的逻辑资源,能够为用户提供高安全性、高可靠性及超低功耗等性能[4-5]。本文方案采用SmartFusion2作为解码器核心控制器,将FPGA和微处理器Cortex-M3优势相结合,实现高精度授时和高可靠性的时统设备IRIG-B码解码器。

1 IRIG-B码简介

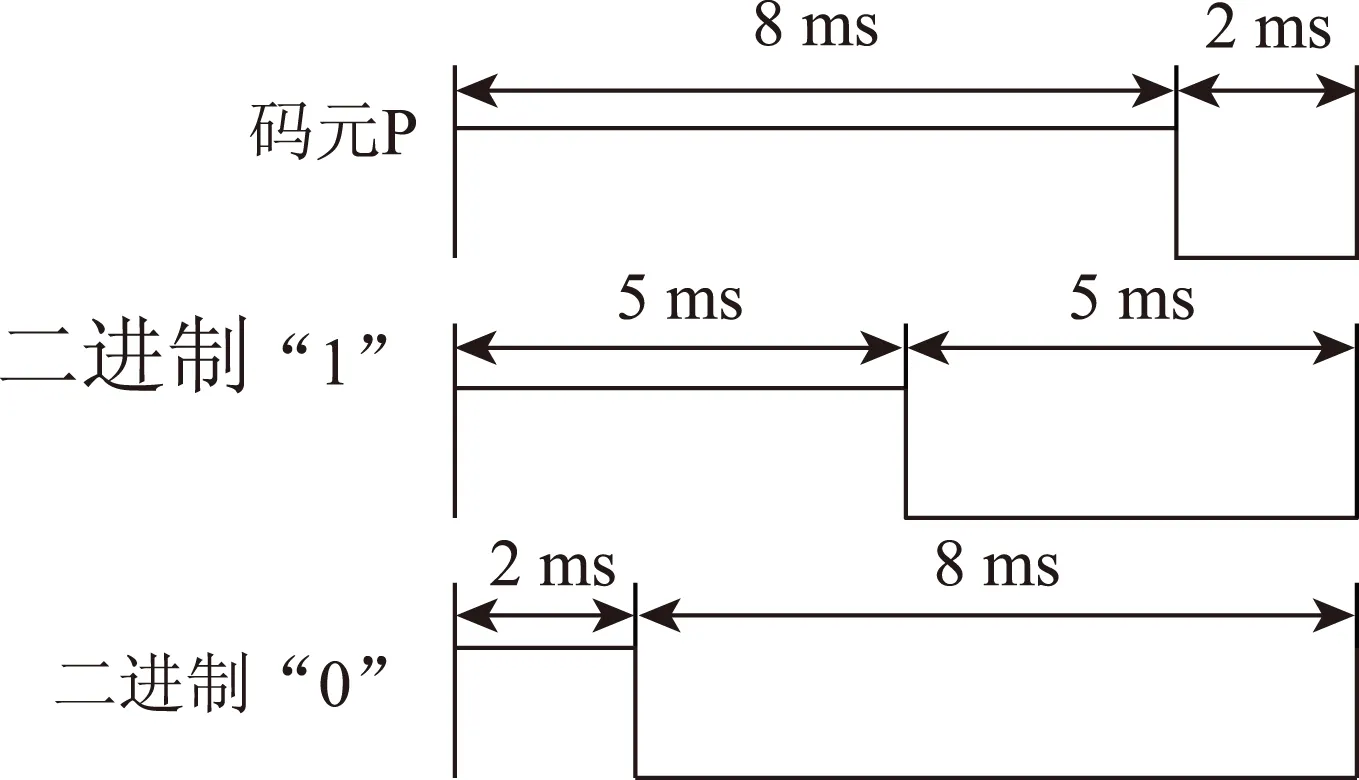

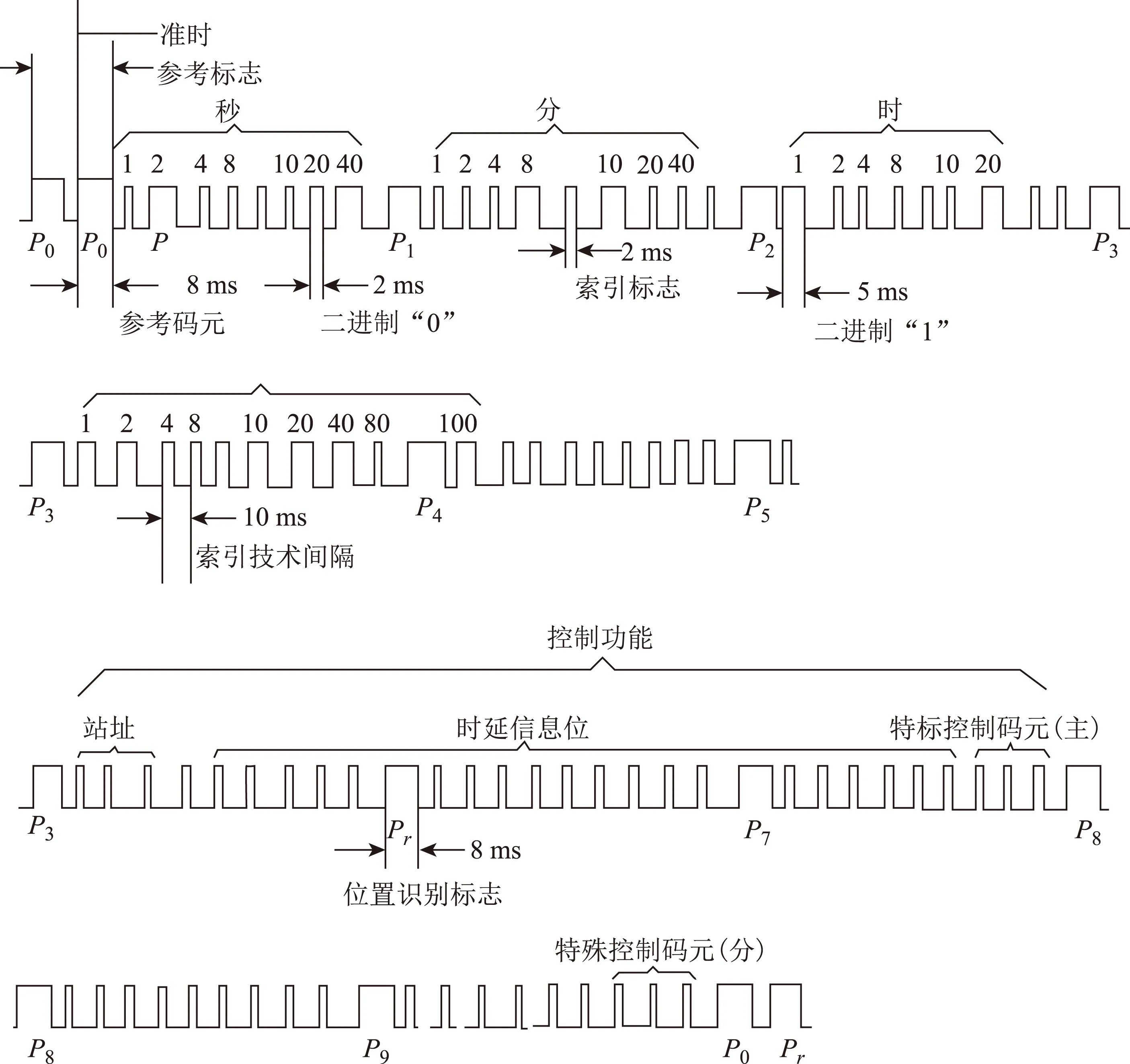

IRIG-B码是一种串行的时间格式码[6-10],DC码为IRIG-B码的直流码,DC码的帧周期为1 s,由100个码元组成,每个码元10 ms,码元宽度有8 ms、5 ms和2 ms 3种,分别代表码元P(位置识别标志或基准码元)、二进制的1以及二进制的0,如图1所示。为了便于传输和提取B码中的信息,每10个码元中有1个位置识别标识,分别称为P1、P2、…、P9、P0。帧参考标志是由位置识别标志P0和相邻的基准码元Pr组成的,Pr的前沿即是每帧的准秒时刻,也就是从该准秒时刻起,按秒、分、时、天等时间信息进行编码,最终形成DC码,如图2所示。

图1 DC码码元图

图2 IRIG-B(DC)码信号波形

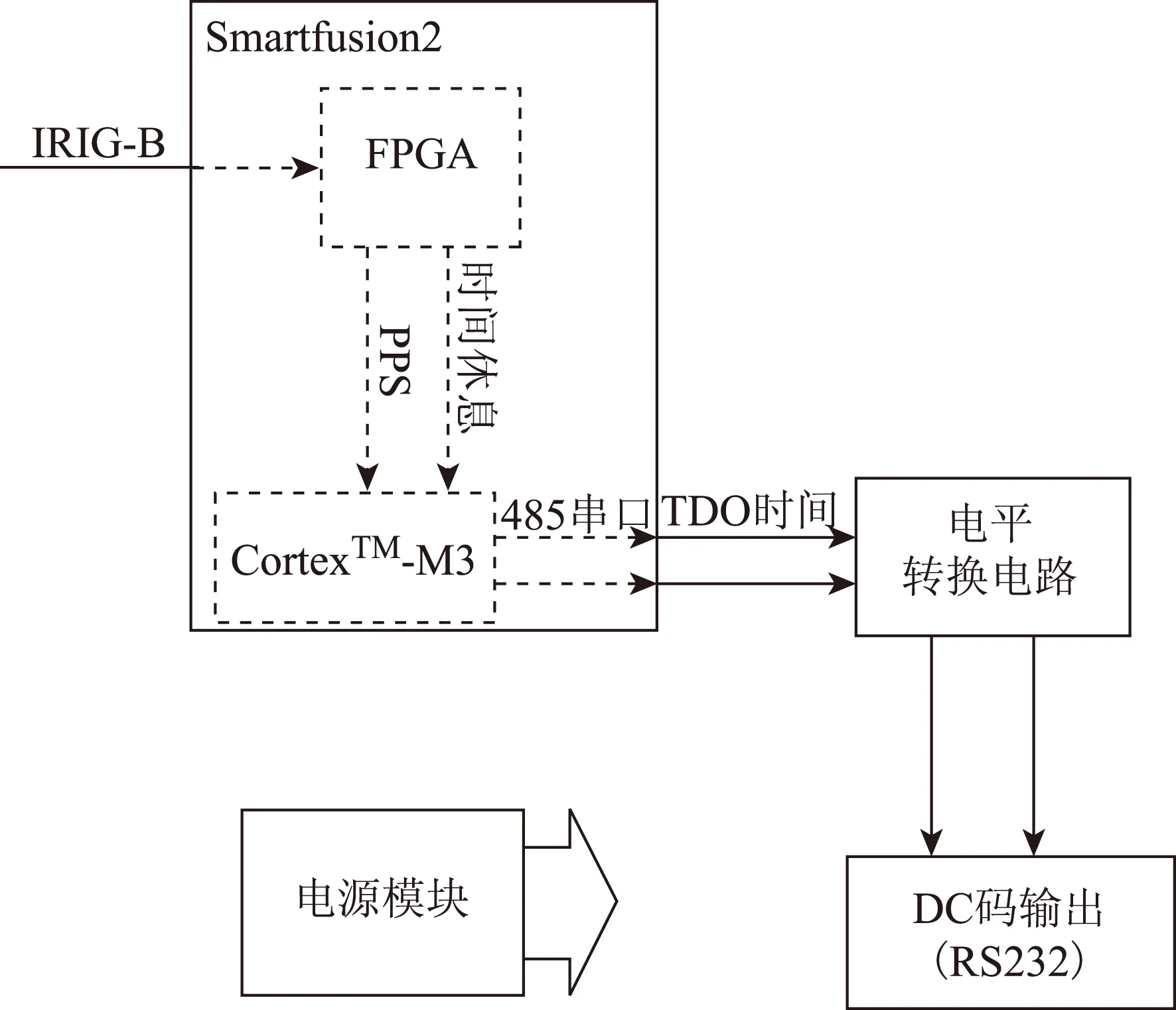

2 硬件电路设计

IRIG-B码信号解码器的整体硬件电路设计框架如图3所示,这里的SmartFusion2在其内部配置了FPGA和Cortex-M3硬核处理器。

图3 硬件电路设计框架

首先将标准的IRIG-B码信号作为SmartFusion2的输入信号,这里SmartFusion2采用Microsemi公司的M2S010芯片;接着在SmartFusion2中,先通过FPGA接收输入信号IRIG-B码,识别出秒脉冲(pulse per second,PPS)和对应的二进制码元,将1个PPS送入Cortex-M3微处理器,将对应的二进制码元送入双端口的随机存取存储器(random access memory,RAM),Cortex-M3微处理器根据输入的1个PPS同步读出FPGA中RAM里二进制码元,并进行解码;根据IRIG-B码协议提取出对应的时间信息,然后将其转换成字符格式的实时时间常数(time of data,TOD)信息;同时TOD信息被送到Cortex-M3微处理器的串口输出脚,进入电平转换电路,从而将TOD信息直观显示到电脑串口调试助手上。这里采用芯片MAX3232SOP对TOD信息进行驱动并转换成匹配的电平信号。

此外,整个硬件电路设计中,还需要电源模块,以满足各芯片对供电电压的需求,分别需要电压为+5 V、+3.3 V;这里采用电源转换芯片LT1963ES8以完成+6.5 V到+5 V的转换,集成电路LT1963EST-3.3以完成+5 V到+3.3 V的转换。

3 软件程序设计

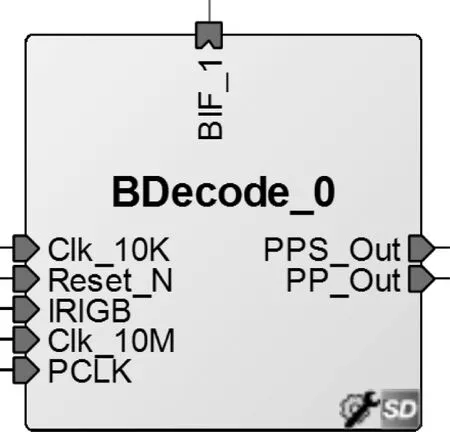

IRIG-B码信号解码器的软件设计主要是基于FPGA及Cortex-M3微处理器系统(microcontroller subsystem in SmartFusion2,MSS)而完成,如图4所示,其中FPGA主要负责MSS的构建、IRIG-B码中1个PPS和对应码元识别及码元存储的程序设计,MSS主要负责读取存储器中对应码元并解码输出的程序设计等。

图4 总体软件设计程序

3.1IRIG-B码解码方法简述

根据IRIG-B码波形,在本设计中每1 ms视为1 bit,有脉宽为高电平1,否则为低电平0,则IRIG-B码中3种码元“P”“1”和“0”分别用二进制表示为1111111100、1111100000和1100000000,即十六进制0x3fc、0x3e0和0x300。则一帧IRIG-B码为100码元即为1 000 bit二进制码流。

首先通过FPGA识别以上3种码元,并得出帧参考标志PP_Out;其次根据PP_Out和IRIG-B码上升沿开始计数,计满99,则其后相邻的IRIG-B码上升沿为准秒时刻PPS_Out,即为同步的1个PPS;同时,根据PP_Out开始提取此帧的100码元并转换成1 000 bit码流,并存入双端口RAM中,FPGA程序如图5、6所示;MSS根据准秒时刻标志PPS_Out产生中断,读出FPGA中RAM中1 000 bit码流,并进行解码,根据IRIG-B码协议,提取出对应的时间信息并转换成字符格式的TOD信息,并将此TOD信息通过串口发送出去。

图5 IRIG-B码解调核的FPGA程序

图6 IRIG-B码解调核的FPGA内部程序

3.2FPGA程序设计简述

在FPGA里完成的程序设计主要有以下几个方面:

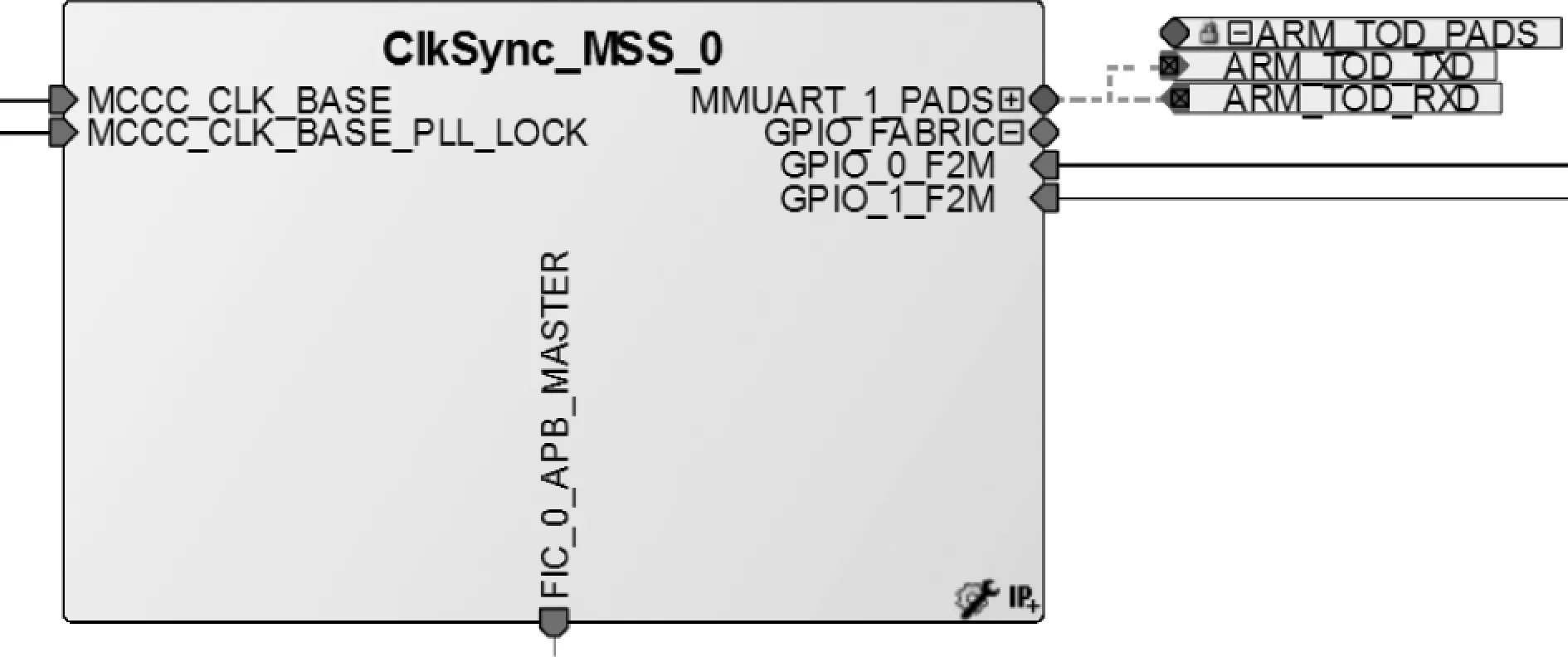

1)设计锁相环、复位电路。从而给FPGA程序里各个设计模块和微处理器系统MSS提供参考时钟与复位。2)构建MSS。包括中央处理器、通用输入输出(general purpose input output,GPIO)模块、串口通信模块、外围总线(advanced peripheral bus,APB)等,如图7所示。

图7 Cortex-M3微处理器系统MSS的FPGA程序

3)定制码元识别模块。主动识别IRIG-B码中3种码元“P”“1”和“0”,并分别用二进制表示为111111100、1111100000和1100000000,即十六进制0x3fc、0x3e0和0x300;同时主动识别IRIG-B码的上升沿和下降沿。

图8 IRIG-B码元识别模块的FPGA程序

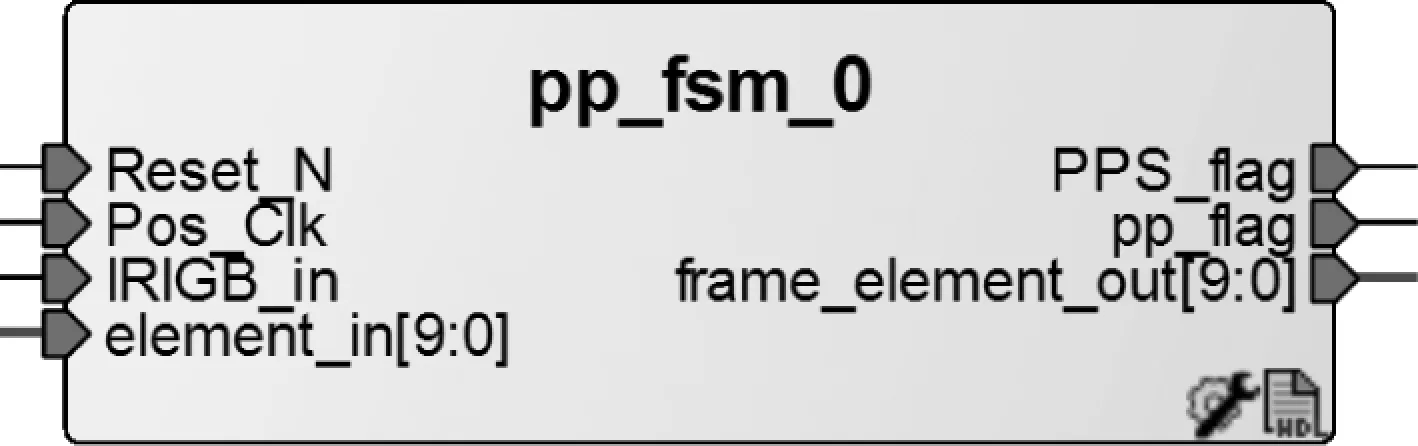

4)定制IRIG-B码解码模块。根据输入IRIG-B码的上升沿Pos_Clk和二进制码元element_in,可主动识别IRIG-B码的帧参考标志PPFlag;当识别出PPFlag的同时,自上升沿Pos_Clk来,输出二进制码元,以得到完整的一帧IRIG-B码的二进制格式;当识别出PPFlag的同时,根据输入的IRIGB_in上升沿开始计数,当计满99,下一相邻的IRIGB_in上升沿即为准秒时刻标志PPSFlag,即为同步的1个PPS。

图9 IRIG-B码解码模块的FPGA程序

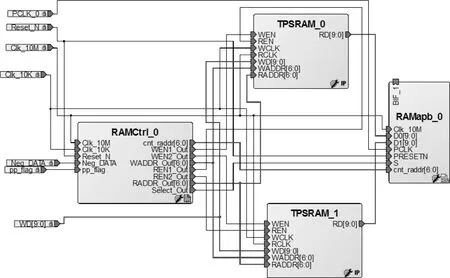

5)定制双端口RAM模块。从FPGA解码模块输出的二进制码流被写进RAM模块里,MSS通过APB总线从RAM模块中读出对应的二进制码流。在这里,FPGA程序采用了乒乓操作,即写RAM_0操作的同时进行读RAM_1操作,而写RAM_1操作的同时,进行读RAM_0操作,如此循环操作,如图10所示。RAM写时钟为10 kHz,写字长为10 bit,而RAM读时钟为10 MHz,读字长为10 bit;其中,RAM控制程序通过帧参考标志PPFlag来控制RAM_0、RAM_1的读写切换,通过10 kHz控制RAM写地址,通过10 MHz控制RAM读地址。

图10 双口RAM读写模块的FPGA程序

3.3MSS程序设计简述

在微处理器系统MSS里完成的程序设计,主要有以下几个方面:1)对MSS进行初始化。配置一个GPIO端口作为中断引脚,映射来自FPGA中识别出的1个PPS中断;再配置一个GPIO端口作为中断引脚,映射来自FPGA中识别出的帧参考标志PPFlag中断;配置一个APB总线主模块,读取FPGA中解出的IRIG-B码流;配置一个串口通信模块,发送已解出的TOD信息。2)当帧参考标志PPFlag中断到来时,通过APB总线开始读取FPGA中RAM里的IRIG-B码元并进行解码,得到秒、分、时、日、月、年等时间信息并保存在内部的一个结构体类型变量中。3)当秒脉冲中断到来时,开始向串口发送已解出的时间信息,格式为:

$TOD,时分秒,日,月,年*checksum/r/n

4 实验与结果分析

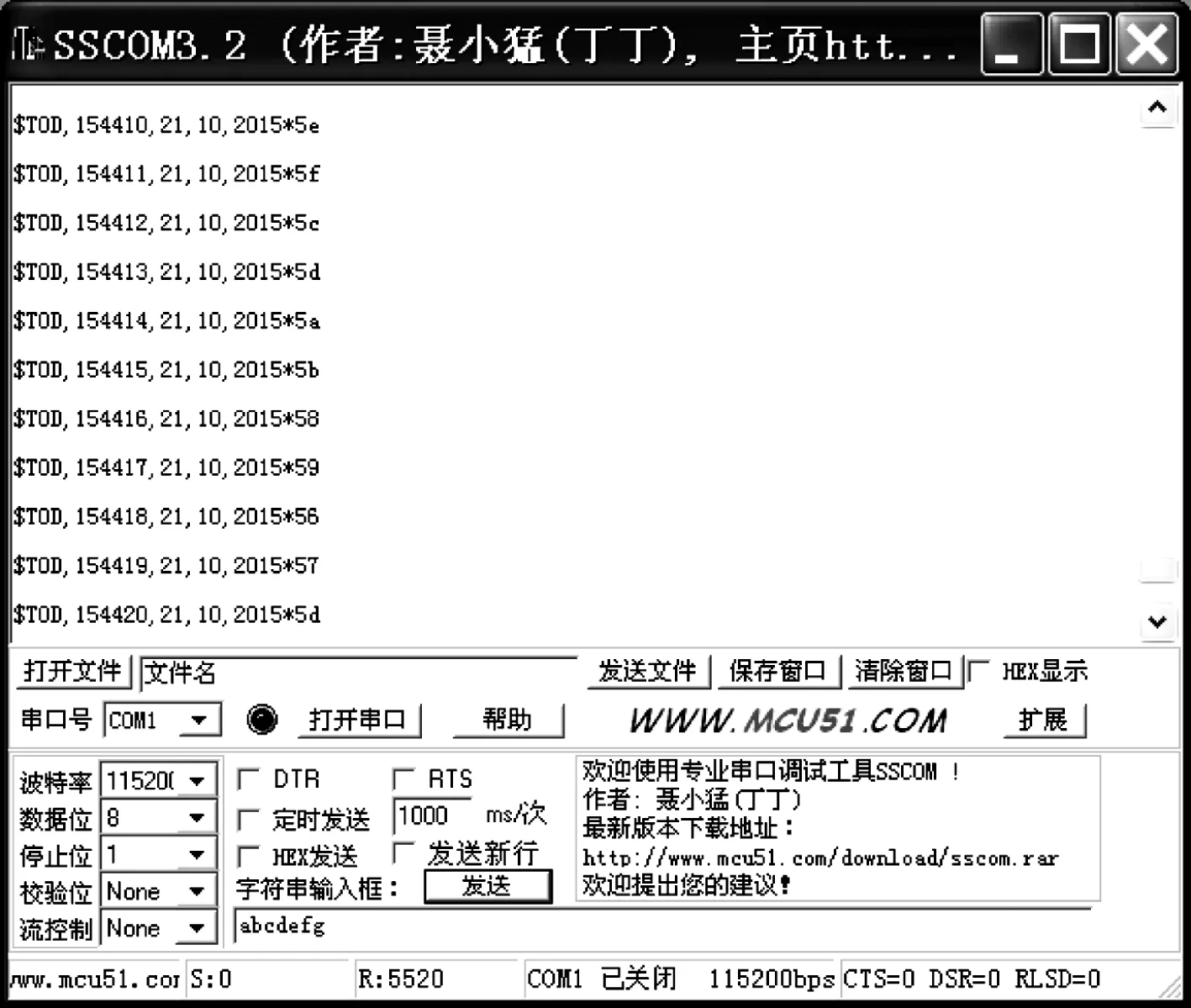

基于SmartFusion2芯片方案设计中FPGA部分采用Libero SoC v11.0设计软件,用硬件描述语言(verilog hardware description language,Verilog HDL)实现设计,Cortex-M3微处理器系统MSS部分采用Microsemi SoftConsole IDE v3.4编程软件设计,IRIG-B码信号由上海申贝公司的时间同步装置输出。根据本设计方案,接入IRIG-B码信号,系统上电,测试结果如图11所示。

图11 实验测试结果

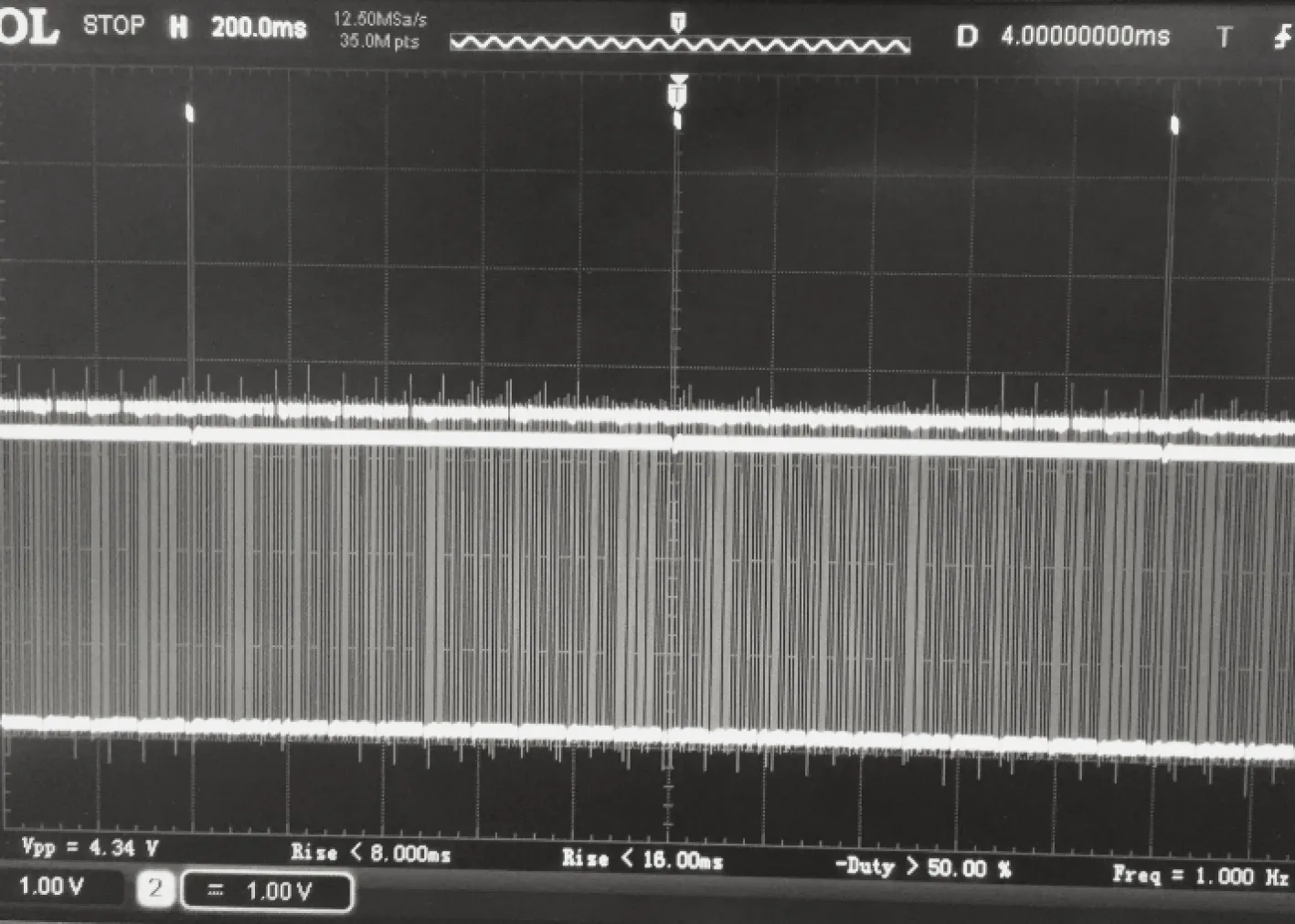

将串口输出接入电脑串口调试助手中,从图中可以看出,时间在1 s的跳变,时间跳变准确。用示波器监测秒脉冲输出端和串口输出端口,实验测试结果见图12。

图12 实验测试结果

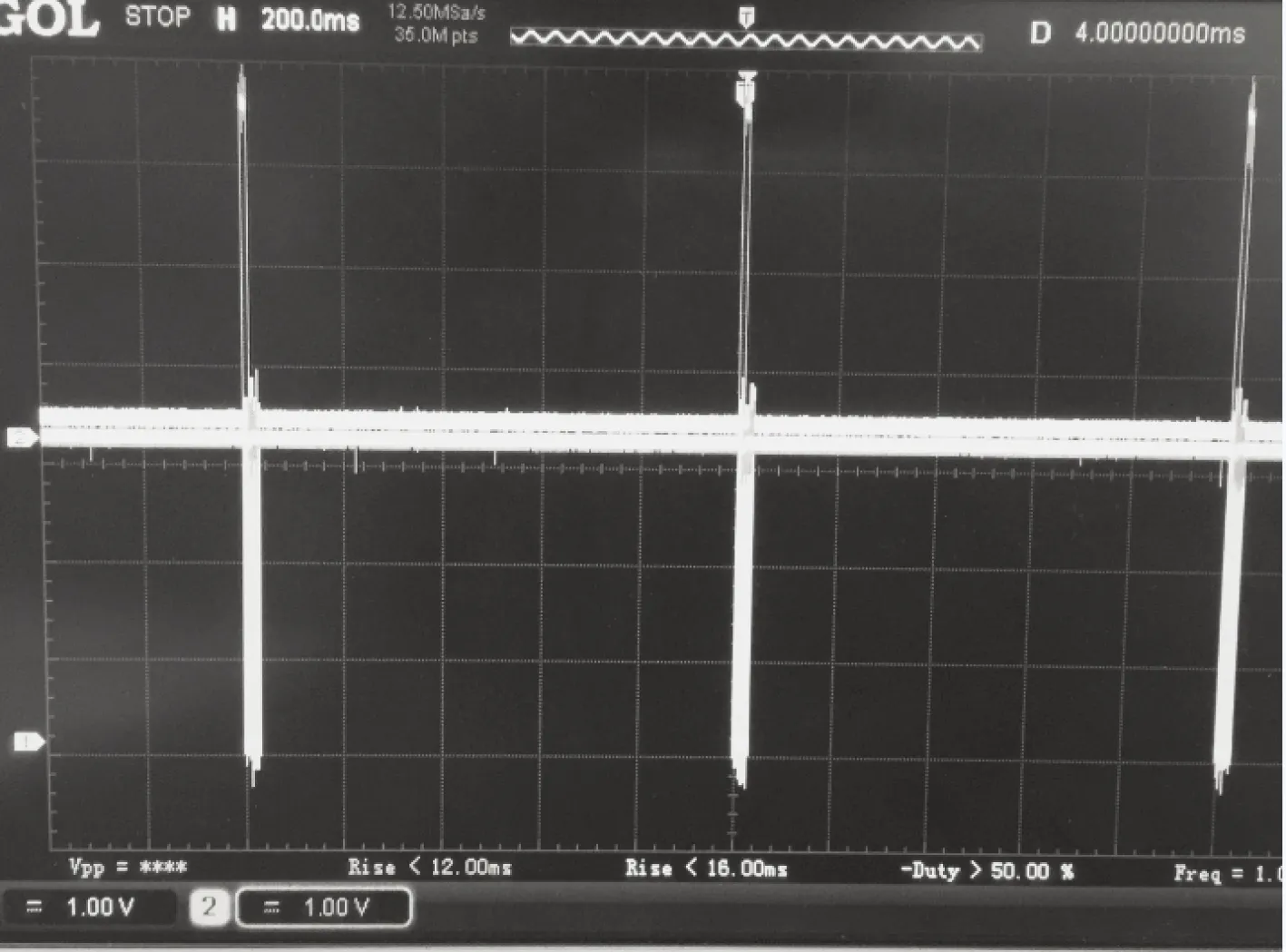

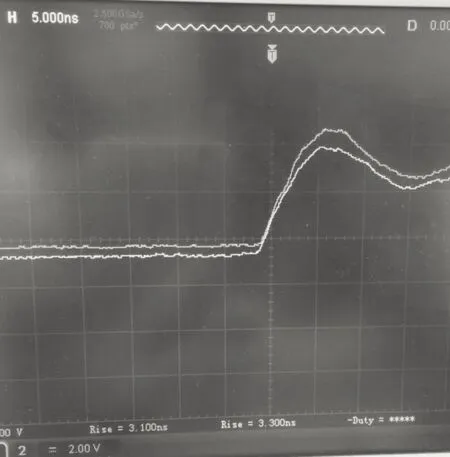

从图中可以看出,解调1个PPS之后相邻1帧解调的时间信息,解调的1个PPS和时间信息是IRIGB码同帧数据。用示波器监测IRIG-B码信号的输入端口和解出的秒脉冲1个PPS输出端口,测试结果见图13。从图中可以看出,每一解出的1个PPS对应1帧IRIG-B码输入信号。用示波器上升沿触发方式捕捉1个PPS上升沿,可获得如图14所示的波形。

图13 实验测试结果

图14 实验测试结果

由图14中可以看出,解出的1个PPS上升沿与IRIG-B码输入信号的准秒时刻对齐,且2者间的误差优于5 ns,则本设计的解码误差优于5 ns;因此该IRIG-B码信号解码器的设计完全符合设计要求。

5 结束语

本文分析了目前IRIG-B码解码技术实现的现状及存在的问题,介绍了IRIG-B码解码的基本原理,提出基于FPGA和Cortex-M3设计实现的IRIG-B码解码器,并结合某型时间同步装置进行了监测。监测结果表明,该IRIG-B码解码器能够满足时统设备授时的需求,提高IRIG-B码的授时精度、提升IRIG-B码解码效率、加强系统运行的可靠性。随着IRIG-B码在加速组网和授时系统中日益成熟,在今后工作中将进一步对IRIG-B码解码性能深入研究。

[1]The Timing Committee Telecommunications and Timing Group Range Commanders Council.IRIG standard 200-98 IRIG serial time code formats(Format B)[EB/OL].(2005-01-27)[2015-11-11].http://irigb.com/pdf/wp-irig-200-98.pdf.

[2]谭述森,李琳.北斗系统导航定位报告体制与工程技术[J].导航定位学报,2013,1(3):1-9.

[3]杨安洪,卜鲍强,姜忠武.双模授时技术在航天测控设备中的应用[J].导航定位学报,2015,3(1):88-91.

[4]Microsemi Corportion.Smartfusion2 Microcontroller Subsystem UG0331 User Guide,m2s_ug0331_microcontroller_subsystem_v10.pdf[EB/OL].(2015-06-01)[2015-11-11].http://www.microsemi.com/index.php?option=com_docman&task=doc_download&gid=130918.

[5]Microsemi Corportion.Smartfusion2 SoC FPGA Evaluation Kit UG0541 User Guide,m2s_ug0541_evaluation_kit_ug_v4.pdf [EB/OL].(2015-06-01)[2015-11-11].http://www.microsemi.com/index.php?option=com_docman&task=doc_download&gid=133574.

[6]王茂凌.基于FPGA的IRIG-B(DC)码解码[J].现代有线传输,2005(4):86-88.

[7]贾磊,崔永俊,杨兵,等,基于FPGA的IRIG-B(DC)码解码卡的设计[J].计算机测量与控制,2015,23(6):2143-2145.

[8]吴卫,陈建军,宋虎.基于FPGA的IRIG-B码解码器的实现[J].雷达与对抗,2009(3):37-40.

[9]顾阳阳,付道文.基于FPGA的IRIG-B码解码器设计[J].电子科技,2015,3(1):88-91.

[10]张建春,任记达.基于FPGA的IRIG-B码调制解调实现[J].现代导航,2012,8(4):305-308.

Design and implementation of a IRIG-B signal decoder

CHEN Wei,WANG Yu,YU Feixia,FAN Xiaodong

(Anhui Suncreate Electronics Co.,Ltd.,Hefei,Anhui 230031,China)

Aiming at the problem that the existing IRIG-B signal decorder is liable to low decoding precision and lack of running stability,the paper proposed a IRIG-B signal decoding scheme by integrating MPU(Cortex-M3) and FPGA:the latest SOC was selected that configures microcontroller subsystem in Smartfusion2 and logical unit of FPGA;the IRIG-B signal code recognizing procedure was controlled by the hard logic of FPGA for ensuring the accuracy of the rising edge of the recognized PPS;the decoding procedure of the recognized time stream and the time output was designed in MSS in order to save FPGA resources and improve decode efficiency.Finally,by the field operation with instrument monitoring,result indicated that the IRIG-B decoder could offer better accuracy and stability than exiting decode technology,and the timing accuracy could satisfy the requirement of time synchronization.

Smartfusion2;FPGA;Cortex-M3;IRIG-B

2015-11-11

国家电子信息产业发展基金项目(工信部财[2013]472号)。

陈伟(1987—),女,安徽合肥人,硕士研究生,研究方向为通信与信息系统。

10.16547/j.cnki.10-1096.20160319.

P127

A

2095-4999(2016)03-0094-06

引文格式:陈伟,王宇,余飞侠,等.一种IRIG-B码解码器的设计与实现[J].导航定位学报,2016,4(3):94-99.(CHEN Wei,WANG Yu,YU Feixia,et al.Design and implementation of a IRIG-B signal decoder[J].Journal of Navigation and Positioning,2016,4(3):94-99.)