用现场可编程门阵列设计IRIG-B码信号产生器

2016-09-19范晓东

范晓东,王 宇,陈 伟

(安徽四创电子股份有限公司,安徽 合肥 230031)

用现场可编程门阵列设计IRIG-B码信号产生器

范晓东,王宇,陈伟

(安徽四创电子股份有限公司,安徽合肥230031)

针对电力系统传统IRIG-B码编码设备体积大、结构复杂等问题,提出一种基于FPGA的IRIG-B码信号产生器的设计方法:首先阐述方法的设计思想;然后重点描述其FPGA硬件电路设计与NiosII软件编程过程。试验结果表明,通过该方法设计IRIG-B码信号产生器可有效缩小设备体积、增强系统稳定性。该设计已应用到了工信部电子信息产业发展基金资助项目BDS/GPS双模电力时间同步装置上,设备运行稳定、授时准确,达到了预期要求。

IRIG-B;FPGA;NiosII;BDS/GPS卫星模块;授时

0 引言

IRIG串行时间码由美国靶场时间仪器组(inter range instrumentation group,IRIG)[1]提出,用于设备及系统的时间同步,该码共有IRIG-A、B、D、E、G、H 6种格式。本文针对电力系统测控与保护等设备普遍采用的时间同步码IRIG-B码(简称B码)进行研究。电力系统厂站、变电站的时间同步系统的IRIG-B编码器大都采用单片机/精简指令集微处理器(advanced RISC machine,ARM)+复杂可编程逻辑器件(complex programmable logic device,CPLD)/现场可编程逻辑门阵列(field programmable gate array,FPGA)架构进行设计[2-6],电路较为复杂,资源利用率低,稳定性较差。因此需要一种设计简单、资源利用合理、体积小、功耗低、高稳定性的IRIG-B编码设备。FPGA适合于时序、组合等逻辑电路设计,同时具有实时性好、可靠性高、可编程、可移植性好等优势,广泛应用于工业控制领域。NiosII软核处理器[7]是FPGA生产厂商Altera公司推出的嵌入式处理器,是一种面向用户、可以灵活定制的通用精简指令集计算机(reduced instruction set computer,RISC)嵌入式处理器。

基于如上所述,本文介绍了一种基于FPGA NiosII软核处理器的IRIG-B码信号产生器的设计方法,给出其具体实现,并应用到电力时间同步装置上。

1 IRIG-B码简介

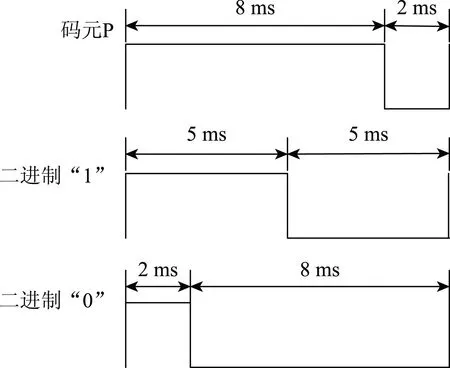

B码是一种串行的时间格式码,分为直流码(direct current code,DC)和交流码(alternating current code,AC)2种[8-9]。DC码的帧周期为1 s,由100个码元组成(如图1所示),每个码元10 ms,码元宽度有8、5和2 ms 3种,分别代表码元P(位置识别标志或基准码元)、二进制的1以及二进制的0,如图1所示。为了便于传输和提取B码中的信息,每10个码元中有一个位置识别标识,分别称为P1、P2、…、P9、P0。帧参考标志是由位置识别标志P0和相邻的基准码元Pr组成的,Pr的前沿即是每帧的准秒时刻,也就是从该准秒时刻起,按秒、分、时、天等时间信息进行编码,最终形成DC码。

图1 DC码码元图

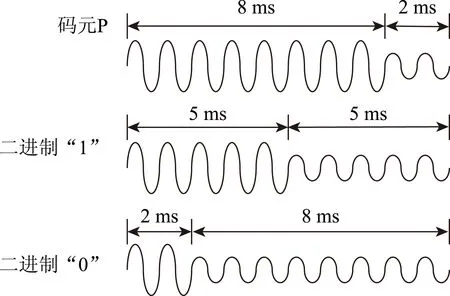

AC码的载波是1 kHz的正弦信号,幅度变化峰峰值范围为0.5 ~10 V,调制比U1/U0范围为2/1~6/1,即:二进制的0是由2个幅度为U1与8个幅度为U0的正弦信号构成;二进制的1是由5个幅度为U1与5个幅度为U0的正弦信号构成;码元P是由8个幅度为U1与2个幅度为U0的正弦信号构成,如图2所示。

图2 AC码码元图

2 总体设计思想

本设计充分利用电力系统厂站或变电站时间同步装置丰富的FPGA逻辑资源,在不增加额外的外部处理器电路基础上,采用FPGA作为主控制器,将节余的FPGA逻辑资源配置为内嵌的NiosII核。

IRIG-B码DC码编码程序在NiosII里完成,输出电路由FPGA内的硬件逻辑控制,保证了B码上升沿的精准性。IRIG-B码可用于北斗卫星导航系统(BeiDou navigation satellite system,BDS)和全球定位系统(global positioning system,GPS)的授时模块设计。该IRIG-B码信号产生器采用BDS/GPS卫星模块作为标准时钟源,从卫星模块输出的协调世界时(coordinate universal time,UTC)报文中提取时间信息,并利用其输出的秒脉冲(one pulse per second,1PPS)作为触发实现DC码的编码。在DC码的基础上,通过正弦信号发生器实现AC码的数字调制;再通过驱动电路送往输出单元。

基于FPGA内嵌NiosII处理器进行设计,达到了有效减少设备体积、降低功耗、增加设备稳定性的目的。

3 硬件电路设计

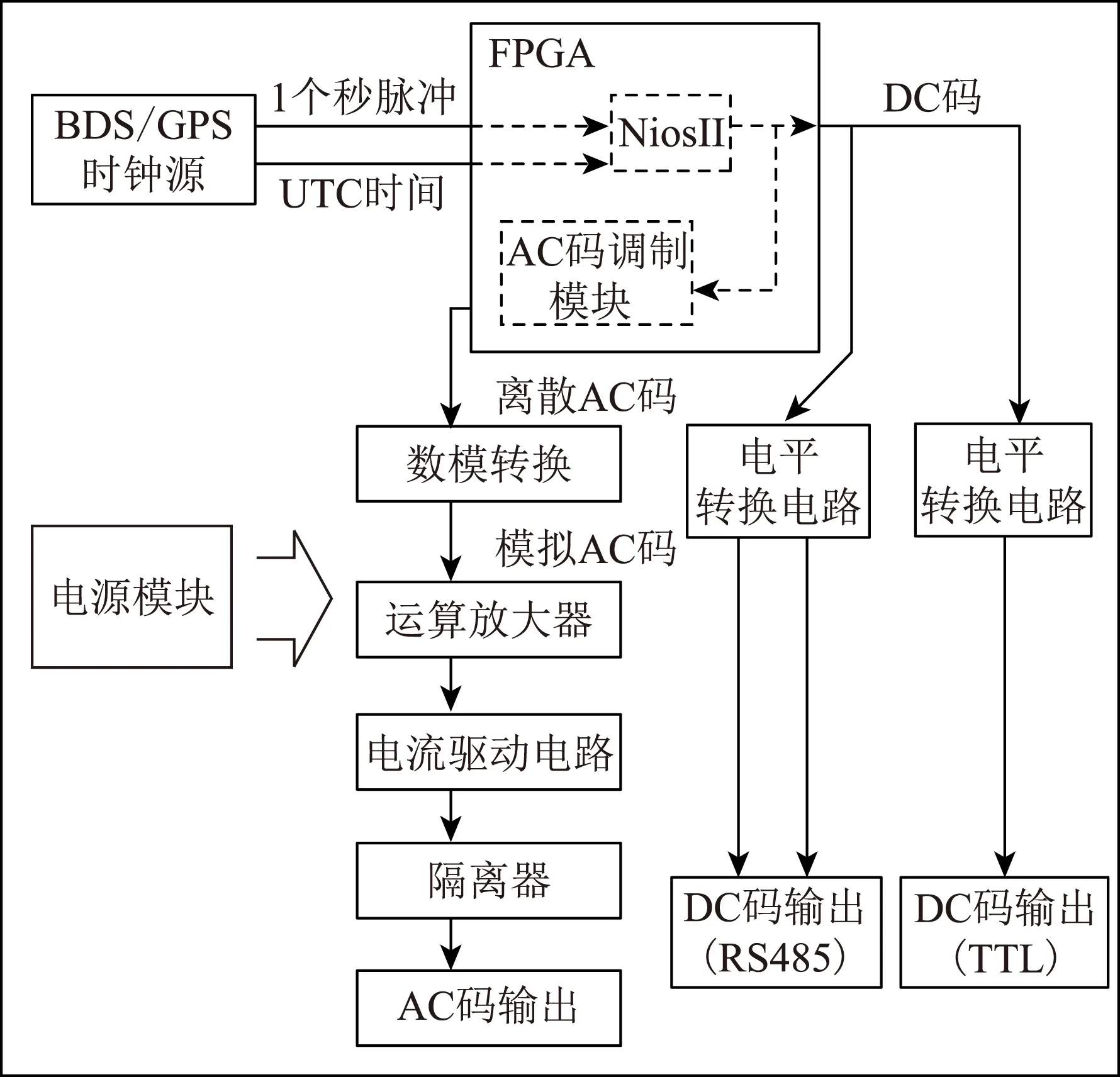

IRIG-B码信号产生器的整体硬件电路设计如图3所示,这里的FPGA在其内部配置了NiosII嵌入式处理器。

图3 硬件电路设计框架

由图可知,首先,作为标准时钟源的北斗卫星导航系统(BeiDou navigation satellite system,BDS)及全球定位系统(global positioning system,GPS)授时模块将1个秒脉冲(pulse per second,PPS)和UTC时间信息送往FPGA内部的NiosII微型处理器,这里的FPGA采用Altera公司的EP3C25E144I7芯片。接着,在NiosII处理器里进行软件设计,根据B码的标准格式,通过数字信号处理实现DC码编码;经过编码后的DC码一路被送至FPGA外围输出引脚,另一路被送入FPGA内部的AC码数字调制模块,进而实现经过数字调制的AC码,之后也送至FPGA外围输出引脚。接着,从FPGA输出引脚出来的DC码,进入电平转换电路,比如RS485电平转换电路、晶体管-晶体管逻辑电平(transistor-transistor logic,TTL)转换电路等,从而能够产生各种电平的DC码,这里采用芯片MAX1487CPA对DC码进行驱动并转换成RS485电平信号,采用芯片TPS2812D对DC码进行驱动并转换成TTL电平信号。然后,从FPGA输出引脚出来的离散AC码进入数模转换电路,从而产生模拟的AC码,这里采用的数模转换电路是芯片AD7945BR。最后,将AC码依次送入运算放大器电路(集成电路AD811)、电流驱动电路(集成电路MMBT2222)以及隔离器电路(集成电路EI-14),从而产生符合标准要求的AC码。

此外,整个硬件电路设计中还需要电源模块,以满足各个芯片对供电电压的需求。归纳起来,分别需要的电压为+12、-12、+5、+3.3、+2.5、+1.2 V,这里采用了电源转换芯片PDL02-12S12以完成+15 到±12 V的转换,集成电路LT1963EST-3.3以完成+5到+3.3 V的转换,集成电路LTC3564以完成+3.3到+2.5 V的转换以及+3.3到+1.2 V的转换。

4 软件程序设计

IRIG-B码信号产生器的软件设计主要是基于FPGA+NiosII而完成的。其中NiosII主要负责DC码编码的程序设计;FPGA主要负责NiosII软核的构建、离散AC码调制的程序设计等。

4.1NiosII程序设计简述

在NiosII里完成的程序设计主要有以下几个方面:1)对NiosII处理器进行初始化。配置一个通用输入/输出(general purpose input output, GPIO)端口作为中断引脚,映射来自外部标准时钟源的1个PPS中断;配置一个通用异步收发传输器(universal asynchronous receiver/transmitter,UART)模块,接收来自外部标准时钟源的UTC时间信息。2)每当UART接收中断到来时,启动任务进程Task1。这个任务进程主要负责解析UTC时间信息,并将得到的秒、分、时、日、月、年等时间信息保存在内部的一个结构体类型变量中。3)每当GPIO中断到来时,启动任务进程Task2。在这个任务进程里,首先根据外部1PPS这个秒脉冲,生成一个内部实时时钟;接着根据内部实时时钟的时间信息,以及B码的标准协议格式,完成DC码的编码工作;最后把经过编码的DC码写进NiosII外部的随机存取存储器(ramdom access memory,RAM)中。

4.2FPGA程序设计简述

在FPGA里完成的程序设计主要有以下几个方面:

1)设计锁相环PLL、复位电路,从而给FPGA程序里各个设计模块提供参考时钟与复位。

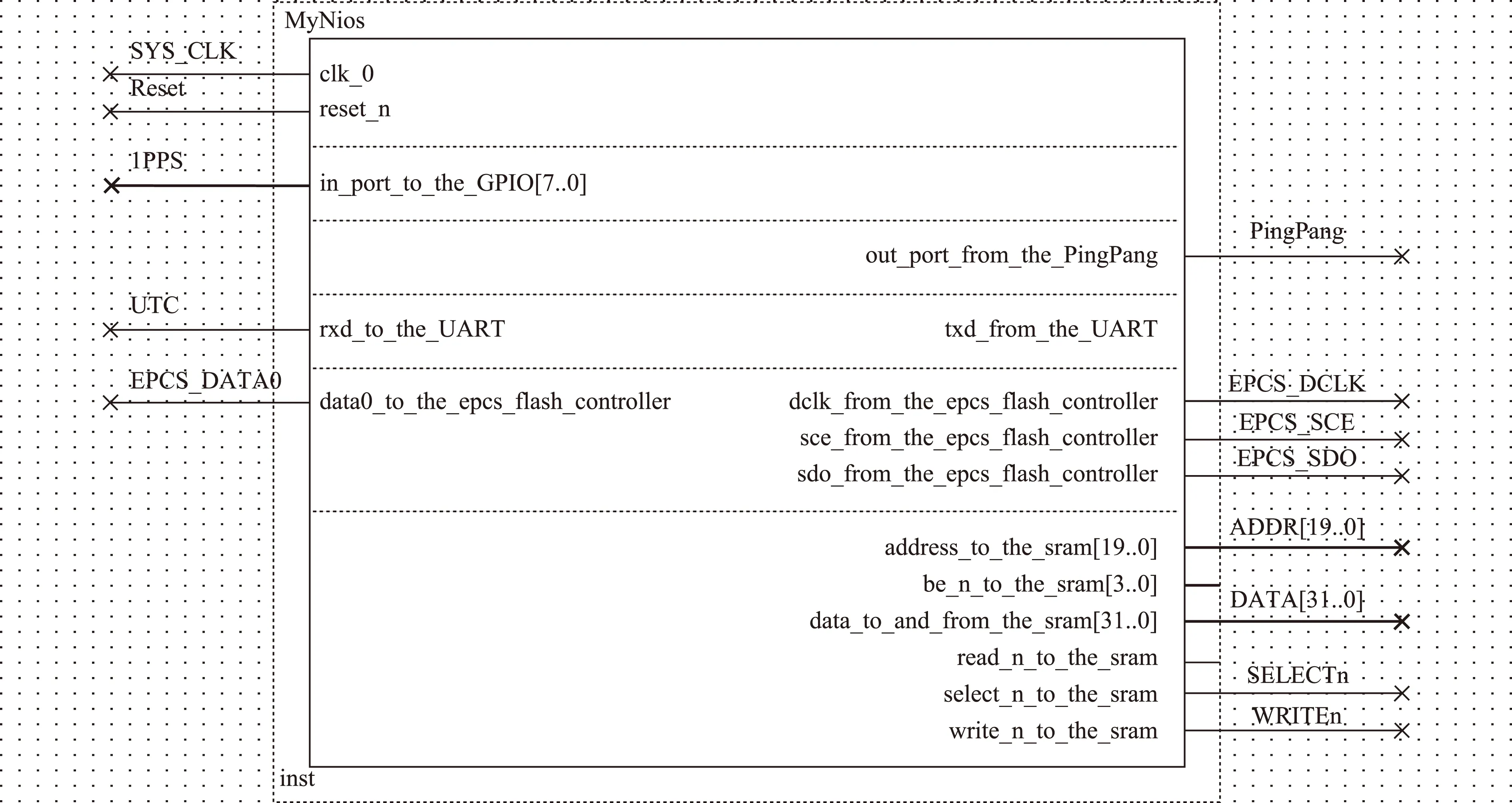

2)构建NiosII软核,包括CPU、GPIO模块、UART模块、RAM控制器模块、FLASH控制器模块等,如图4所示。

图4 NiosII软核的FPGA程序

3)定制双端口RAM模块,从NiosII输出的DC码被写进RAM模块里,在这里FPGA程序采用了乒乓操作,即写RAM1操作的同时,进行读RAM2操作,而写RAM2操作的同时,进行读RAM1操作。如此循环操作,如图5所示。

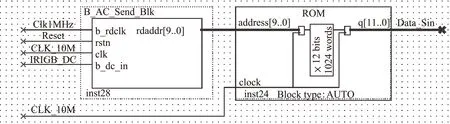

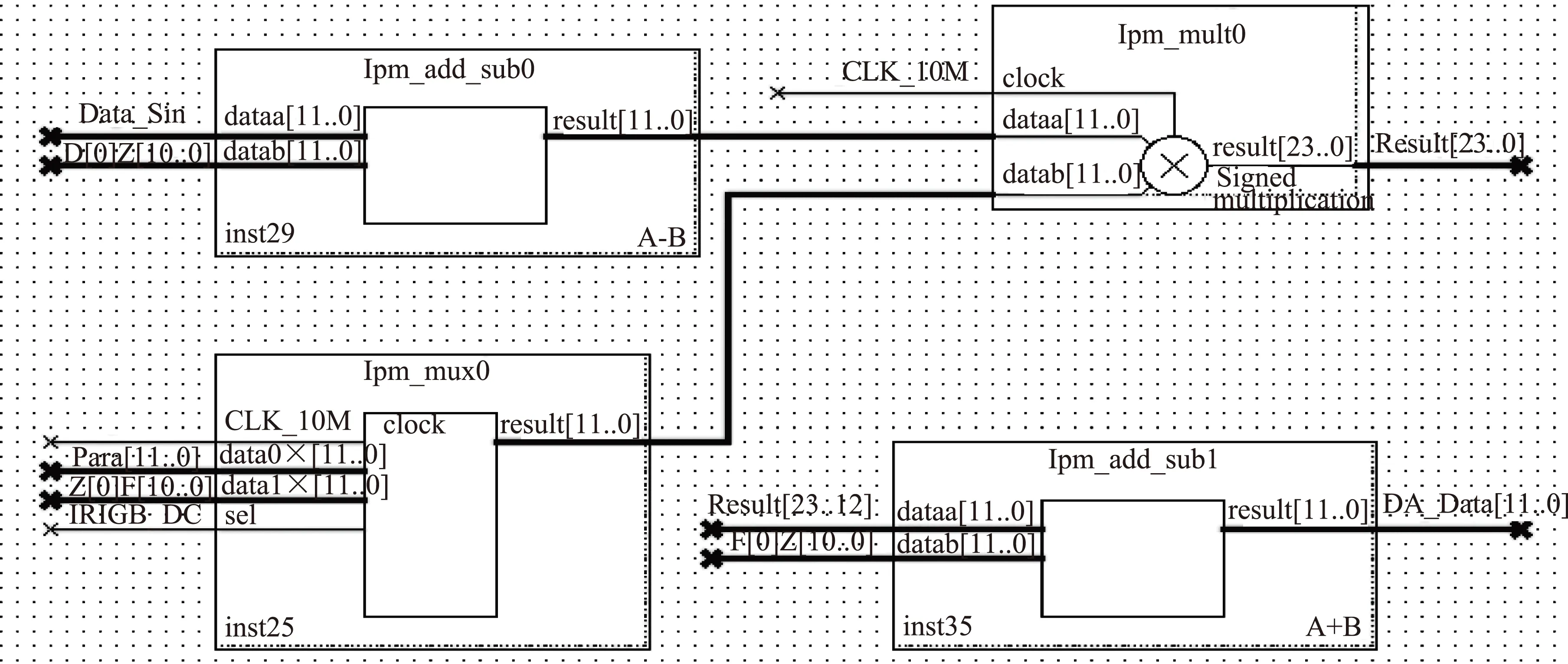

4)设计AC码数字调制模块,其主要包括正弦信号发生器模块、乘法器模块以及数据选择器模块等,如图6、7所示,这里的正弦信号发生器模块是由地址发生器与正弦信号数据只读存储器(read only memory,ROM)组成。

AC码的数字调制过程即是用DC码作为控制信号,让正弦信号数据与2种不同预设参数分别相乘,从而产生具有可变调制比的离散AC码,最后从FPGA输出引脚。

图5 RAM读写的FPGA程序

图6 正弦信号发生器的FPGA程序

图7 AC码数字调制的FPGA程序

5 测试结果与分析

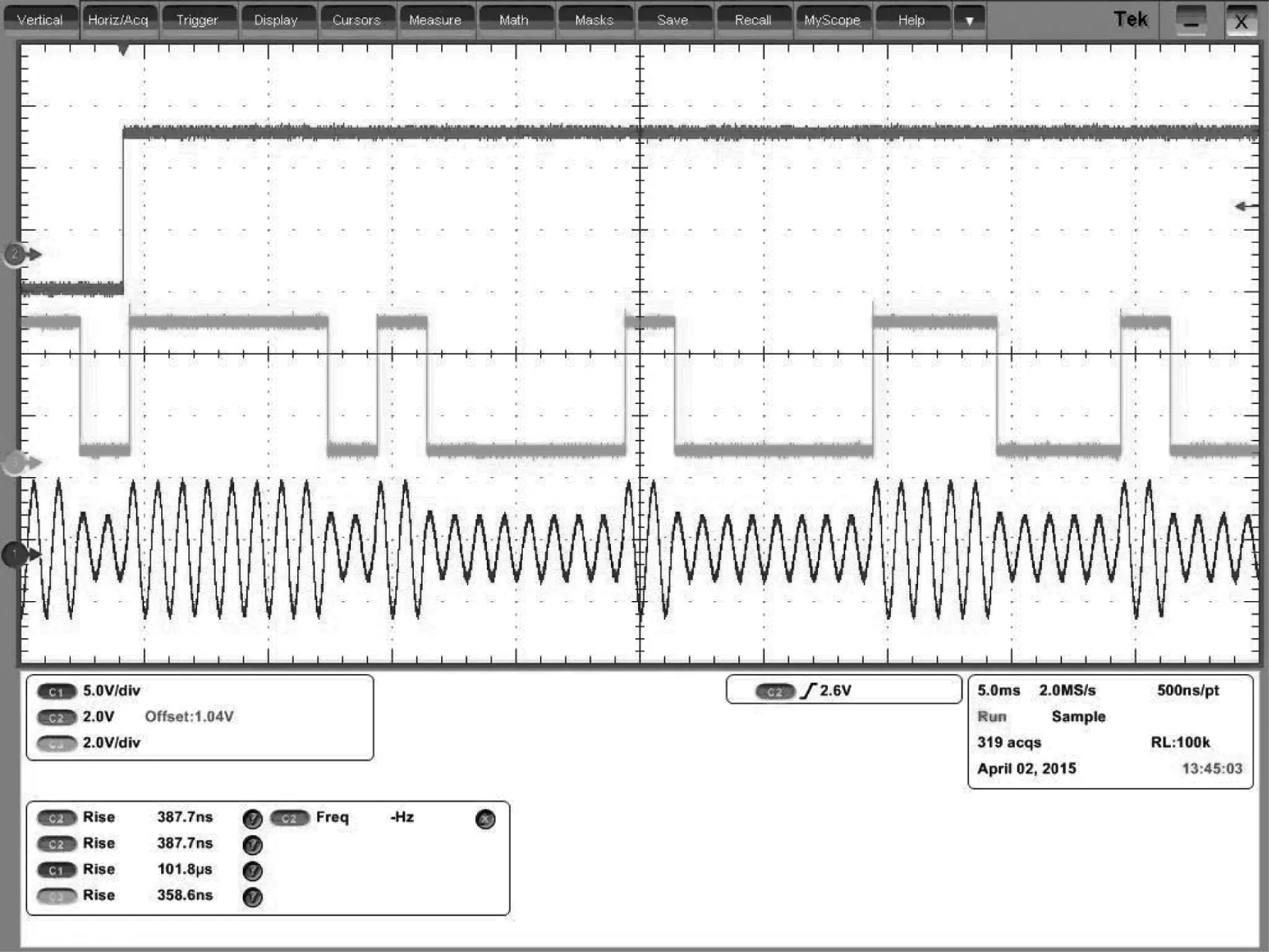

根据本文思想设计的B码信号产生器已在电力高精度时间同步装置上作为B码输出模块得到应用。通过示波器观测装置B码输出的DC码信号波形、AC码信号波形如图8所示。

图8 测试结果

观测示波器输出的波形图,对照B码的标准协议格式,可以读出时间信息为13:34:55,与标准时钟源输出的实时时间一致。实测DC码的秒准时沿时间准确度优于200 ns,AC码秒准时沿时间准确度优于10 us。本B码信号产生器作为BDS/GPS双模电力时间同步装置的一部分,已通过了电力工业系统自动化设备质量检验测试中心质量检测,设计满足电力行业标准要求[10-11]。

6 结束语

本文在介绍了IRIG-B码的基础上,提出了一种基于FPGA的IRIG-B信号产生器的设计方法,并详述了其具体实现的硬件电路设计、NIOSII软核构建及其编程过程。该方法设计简便,发生器体积小、功耗低。本设计已在工信部电子信息产业发展基金资助项目中BDS/GPS双模电力时间同步装置上得到应用,充分利用原有系统FPGA逻辑资源,有效节省了硬件成本。设备在变电站中运行稳定、授时准确,达到了预期要求。后期将在进一步提高精度、降低成本、降低功耗等方面开展研究。

[1]Timing Committee Telecommunications and Timing Group Range Commanders Council.IRIG serial time code formats (format B):IRIG standard 200-98[S].New Mexico:Secretariat Range Commanders Council U.S.Army White Sands Missile Range,1998:15-33.

[2]黄新波,郭剑锋,石杰,等.基于IRIG-B码的电容型设备在线监测同步采样技术研究[J].华东电力,2014,42(6):1180-1185.

[3]童伟.基于北斗II代/GPS的电力系统双模时间同步时钟的研制[J].电力建设,2014,35(4):80-85.

[4]佟刚,曹永刚,陈涛.基于MSP430+FPGA的IRIG-B码时统设计[J].电光与控制,2009,16(5):93-96.

[5]张建春,任记达.基于FPGA的IRIG-B码调制解调实现[J].现代导航,2012,3(6):305-308.

[6]宋鹏,田乐.基于FPGA的时间同步精度的设计与实现[J].西安工程大学学报,2014,28(1):89-93.

[7]李兰英,崔永利,李霄燕,等.NiosII嵌入式软核SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2006:187-263.

[8]吕念芝.基于FPGA的闰年自动识别IRIG_B码的设计[J].宁德师范学院学报,2015,27(3):303-305.

[9]熊立智,唐普英.基于FPGA的IRIG-B解码电路设计与实现[J].通信技术,2010,43(8):231-235.

[10]中华人民共和国国家能源局.电力系统的时间同步系统技术规范第1部分:DL/T 1100.1—2009[S].北京:中国电力出版社,2009:8-9.

[11]中华人民共和国国家质量监督检验检疫总局中国国家标准化管理委员会.电力系统的时间同步系统检测规范:GB/T 26866-2011[S].北京:中国标准版社,2011:5-6.

IRIG-B signal generator designed with FPGA

FAN Xiaodong,WANG Yu,CHEN Wei

(Anhui Sun Create Electronic Co.,Ltd.,Hefei,Anhui 230031,China)

To solve the problems of large volume and complex structure of the traditional IRIG-B encoder for electric system,a method of IRIG-B code signal generator based on FPGA was proposed in the paper.The idea of the method was described,and the design of the FPGA hardware circuit and the process of NiosII software programming were focused then.Experimental results showed that the method could effectively reduce the equipment size of the IRIG-B code signal generator and enhance the system stability.This method of the design had been applied in the project of BDS/GPS dual-modulus electronic time synchronization device sponsored by Electronic Information Industry Development Fund of the Ministry of Industry and Information Technology (MIIT) in which the equipment ran stably and the expected timing goals were achieved.

IRIG-B;FPGA;NiosII;BDS/GPS satellites module;timing

2015-11-17

范晓东(1982—),男,安徽芜湖人,硕士研究生,研究方向为个人通信与无线通信。

10.16547/j.cnki.10-1096.20160318.

P228

A

2095-4999(2016)03-0089-05

引文格式:范晓东,王宇,陈伟.用现场可编程门阵列设计IRIG-B码信号产生器[J].导航定位学报,2016,4(3):89-93.(FAN Xiaodong,WANG Yu,CHEN Wei.IRIG-B signal generator designed with FPGA[J].Journal of Navigation and Positioning,2016,4(3):89-93.)