贪婪型动态数字复接器设计与时延分析

2016-09-14石立国王竹刚熊蔚明候鸿杰

石立国,王竹刚,熊蔚明,候鸿杰

(1.中国科学院空间科学与应用研究中心 北京 100190;2.中国科学院大学 北京 100190)

贪婪型动态数字复接器设计与时延分析

石立国1,2,王竹刚2,熊蔚明2,候鸿杰1,2

(1.中国科学院空间科学与应用研究中心 北京 100190;2.中国科学院大学 北京 100190)

为了节省信道资源,可以将多路不同速率、不同猝发时隙的数字信源复合为一路数据的异步数字复接器得到了广泛应用。为了尽最大可能降低源包数据传输时延、提高信道利用率,提出了一种贪婪型异步动态数字复接器的设计方案,并给出了各路信源的优先级调度策略。使用硬件描述语言对两种复接模型进行描述。在不同物理帧和两种信源模式下,通过Modelsim对贪婪型动态复接器和虚拟信道复接器进行了仿真对比。仿真结果表明,贪婪型动态复接的平均传输时延和时延抖动都优于虚拟信道复接,并能够更有效地节省信源缓存资源。

数字复接器;虚拟信道;平均传输时延;时延抖动

在复杂的现代数字通信系统中,所需传输的数字信源往往有很多个。为了提高传输的效率,扩大传输的容量,依据时分复用原理实现的数字信号复接与分接已经广泛应用于很多系统中。数字复接器(Digital Multiplexer)与分解器(Digital Demultiplexer)将不同速率、不同类型的信号进行合并与分离,以实现通过一条信道完成多个信源信号传输的目的。根据复接器与各个信源时钟的不同关系,数字复接器可分为同步复接器[1]和异步复接器。前者对于信源的相位、速率等要求较严,应用的范围相对较窄;后者可以适用于速率、相位、发生间隔等各不相同的多个数字信源的传输,应用较为广泛[2]。许多高校对同步复接器及其缺点进行了研究,并通过码率调整的方式将异步复接变为同步复接[1,3-5],这种实现方式由于插入了许多无用脉冲,降低了信道利用率,并引入了不必要的时延抖动。

目前应用比较广泛的一种复接器被称为虚拟信道复接器[6]。文中根据数字复接器的实现方式,提出了一种新的复接方式:贪婪型动态复接器,并对贪婪型动态复接器和虚拟信道复接器进行了时延分析和对比,以明确其特点和应用场景,目的是提高通信系统的性能。

1 信源要求及物理帧模型

在实际的通信系统中,通常要完成不同速率、不同类型信号的复接。不同信号之间的差别可能很大,具体如下:

1)信号速率差别相当大。光纤信号可以达到Gbps,而音频、控制数据等仅仅只有几十Kbps,甚至更低;

2)对时延的要求不同。有些信号要求有尽可能短的时间延迟,另外还有一些信号对时延不是特别敏感;

3)信源速率可能动态变化。比如视频信号,在通信质量好的情况下,可以按照高清的模式进行传输,在通信质量差的情况下,可以考虑低画质传输,其速率差别很大,范围从几百Kbps到几Mbps不等。

文中假设有4个信源,命名为:S1~S4,其平均速率分别为40 Mbps、5 Mbps、4 Mbps和1 Mbps,对时延的需求程度从S1到S4递减。并且这4个信源设置为匀速模式和短时间猝发模式两种。从S1到S4每个信源的数据包包长分别为4 096 Bytes,2 048 Bytes,1 024 Bytes,512 Bytes。数据包的包头都为2 Bytes,其格式如表1所示。

表1 信源数据包结构Tab.1 Source packet structure

物理帧帧长可以是固定的,也可以是可变的(例如:Prox-1协议)。对于固定帧长而言,数据的解调处理比较简单,同时也可以使用固定长度的编解码方式;可变帧长的解调处理,尤其是帧同步比较复杂。文中假设了5种固定帧长的物理帧格式,帧长分别为256 Bytes、512 Bytes、1 024 Bytes、2 048 Bytes、4 096 Bytes,其中帧头4 Bytes,帧计数7 Bytes,数据域长度分别为:213 Bytes、447 Bytes、885 Bytes、1 781 Bytes、3 573 Bytes,剩余部分都是校验位。编码采用CCSDS标准的RS(255,223)。物理帧格式如表2所示。

表2 物理帧结构Tab.2 Physical frame structure

在本文中所设计的模型中,由于总信源码速率为50 Mbps,因此可以计算得出最大基带码速率为

留有一定余量,取基带码速率为62 Mbps。

2 贪婪型动态复接器设计

文中设计和分析的数字复接器是异步的。因此,在信源数据进入到复接器之前,先要进行缓存。采用图1的结构进行设计。

贪婪型动态复接的优点是使信源数据尽可能快的发送出去,尽最大可能降低时延,尽可能少的传输填充数据。对于物理帧中的数据域较短的情况,由于需要更少的标识符,带宽利用率会更优。

在第1节的信源和物理帧基础上,设计贪婪型动态复接包结构如表3所示。

图1 数字复接器结构Fig.1 Digital multiplexer structure

表3 贪婪型动态复接Tab.3 Greedy dynamic multiplexing

其中,第一列总数据域代表物理帧中的数据域,第二列标识符代表信源在复接包中几种信源分配的标志。X、Y的取值根据物理帧长取不同值。对于物理帧长为256 Bytes时,Y取值4,对于其他4种物理帧长,Y取值8;L1~L4分别代表在一帧之中,对应信源的数据字节数。

以物理帧长256 Bytes为例,在贪婪型动态复接中,信源S1~S4的总数据域大小为213 Bytes,4 Bytes的标识符分别表示总数据域中对应信源所占数据字节个数。在物理帧组帧信号到来时,判读所有信源数据缓存个数,按照从S1到S4的优先级顺序,取出共209 Bytes数据,组成一个动态的复合帧。其调度策略如下:

①当信源S1的数据缓存中数据多于209 Bytes,则对应信源S1的标识符为0xD1,对应信源S2~S4的标识符全为0x00,即L1=209,L2=L3=L4=0,此时的总数据域中,仅包含信源S1的数据;

②若信源S1的数据缓存中数据少于209 Bytes,令其值为L1,则对应信源S1的标识符为L1,并从后面优先级低的信源S2数据缓存中取出(209-L1)Bytes数据(假设此时信源S2数据缓存中数据多于209-L1 Bytes),令对应信源S2的标识符为L2=209-L1,对应信源S3、S4的标识符为L3=L4=0,此时的总数据域中,包含信源S1和S2的复合数据。

③若信源S1和S2的数据缓存中数据之和少于209 Bytes,信源S1、S2和S3数据缓存中数据之和大于等于209 Bytes,读出信源S1和S2数据缓存个数L1和L2,令L3=209-L1-L2,L4=0,此时的总数据域中,包含信源S1、S2和S3的复合数据。

④若信源S1~S3的数据缓存中数据之和少于209 Bytes,信源S1~S4数据缓存中数据之和大于等于209 Bytes,读出信源S1~S3数据缓存个数L1、L2、L3,令L4=209-L1-L2-L3,此时的总数据域中,包含信源S1~S4的复合数据。

⑤若所有信源数据缓存中数据之和少于209 Bytes,则令标识符分别为L1、L2、L3、L4,此时的总数据域中,包含信源S1~S4的数据,并对后面的空闲数据域进行填充。

对应贪婪型动态复接的数字分接器的设计也非常简单,仅需要通过对应信源S1~S4的标识符判读,即可方便的分离总数据域中对应的信源数据。

3 虚拟信道复接器

虚拟信道复接方式是目前应用较多的方式之一,即一个信道分为多个虚拟信道,多个虚拟信道根据时分复用的原则,按照一定优先级的调度规则,分时独占信道。这种复接方式的调度算法对信道利用率、数据包的延时及所需的数据缓存大小均有非常大的影响。根据虚拟信道复接的数据源的调度算法,又可分为以下3种方式:全同步复用、全异步复用和同步、异步混合复用[7]。

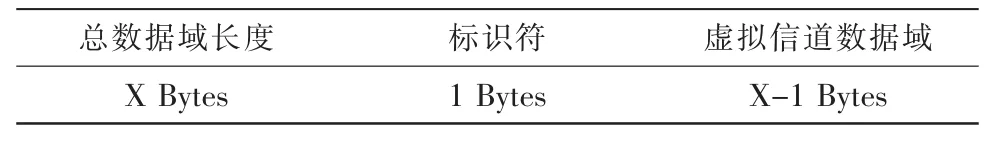

在相同的信源、物理帧结构下,研究不同复接方式的性能才有意义。文中在第1节的信源和物理帧基础上,为了和贪婪型动态复接器进行对比,设计的虚拟信道复接包结构如表4所示。

表4 虚拟信道复接Tab.4 Vitual channel multiplexing

其中,X代表意义同表3。按照信源码速率的大小,将信源S1~S4的优先级按照码速率从低到高的顺序进行优先级调度。物理帧组帧信号到来时,当信源S1缓存数据达到X-1 Bytes以上,则不考虑信源S2~S4,由信源S1占用物理信道;当信源S1缓存数据小于X-1 Bytes时,则对信源S2缓存进行判读,若其缓存数据大于X-1 Bytes,则由信源S2占用物理信道。依次类推,直到最低优先级的虚拟信道。

这种设计方法对信源的码速率、是否猝发等的要求不高,是目前数字复接器应用较多的方法之一。缺点是信源缓存中的数据若长时间不足X-1 Bytes,则会一直残留在缓存中[8]。

4 仿真分析

4路数字信源采用2种模式:匀速模式和猝发模式。匀速模式时,信源 S1~S4的码速率依次为:40 Mbps、5 Mbps、4 Mbps和1 Mbps;猝发模式时,发送时间以0.1 ms为单位周期,在单位周期内,每个信源以较高的速率随机猝发一次,信源S1~S4猝发码速率依次为:320 Mbps、40 Mbps、32 Mbps和8 Mbps,其平均速率同匀速模式。

物理帧设置的主要参数有基带速率和帧结构,详细设置参见1.1节。数字复接器选择了两种:虚拟信道复接和贪婪型动态复接。采用VHDL语言对仿真模型进行描述,并采集仿真数据。本设计旨在模拟数字复接器的时延性能,因此没有将载波同步、位同步、加解扰和编解码等模块带来的时延考虑在内。

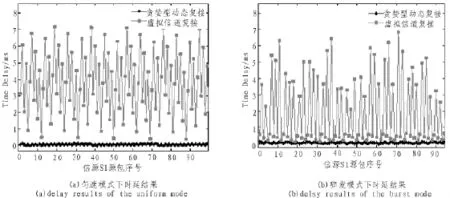

基于上述的仿真场景,进行了二十次仿真,即在两种信源模式和五种物理帧长条件下,分别对两种复接方式进行了仿真。图2给出了信源S1在物理帧长为1 024 Bytes时,匀速模式和猝发模式下,两种复接方式下每个数据源包的延时对比。

从图2中可以看到,在两种模式下,贪婪型动态复接方式的绝大多数数据源包的时延都小于虚拟信道复接方式。

图2 信源S1时延结果Fig.2 Delay results of source S1

平均传输时延是数据源包从终端产生到成功的传输到接入点的平均时间间隔,其值的大小,依赖于源包的长度,包长越大,时延越大。可以看出,贪婪型动态复接的平均时延优于虚拟信道复接。对于优先级较高的信源S1,甚至相差2个数量级。

变化的时延被称为时延抖动(Jitter),抖动大多起源于传输中的队列和缓存,尤其是在低速链路中,时延抖动非常明显。抖动的产生是随机的,而且无法避免。通常将大包拆小,来减少大包对时延的影响。

在某些特定的应用环境中,要求数据包的传输时延相对稳定,也就是相对较小的源包传输时延抖动。从图2中可以看出,贪婪型动态复接信源S1的时延稳定在一个较小的范围之内,最大传输时延也非常小。结果表明,贪婪型动态复接优于虚拟信道复接。

对于虚拟信道复接,物理帧越长,意味着信源数据驻留在缓存中的时间越长,所需要的缓存越大,传输时延越大;对于贪婪型动态复接,由于只要缓存中有多少数据,都会尽可能快的发送出去。所以,物理帧长的变化对贪婪型动态复接的影响较小。

5 结 论

文中所提出的贪婪型动态复接器已成功应用于某通信机,它具有优秀的传输时延性能。通过与虚拟信道复接器的时延性能对比,得出以下结论:

1)贪婪型动态复接的平均传输时延、时延抖动和最大传输时延,都优于虚拟信道复接。

2)物理帧的长度会影响贪婪型动态复接器虚拟信道复接器的时延性能,物理帧越长,平均传输时延、时延抖动和最大传输时延越大。其中虚拟信道复接器更加敏感。

3)由于贪婪型动态复接器尽可能快的将数据缓存中的数据发送出去,故所需的数据缓存少于虚拟信道复接。

[1]徐孟祥.基于FPGA的高速误码仪研制[D].长沙:国防科技大学,2005.

[2]LIU Yue-feng,ZHAO Guang-quan,PENG Xi-yuan.Design and implementation of simulator for AOS high-speed payload multiplexer[C]//.Proceedings of IEEE ICEMI’2013,2013: 285-290.

[3]唐辉艳.基于FPGA的实时仿真系统的设计与实现[D].北京:北京邮电大学,2011.

[4]高广明.正/零/负调整准同步/同步复接技术[J].通信学报,1981(4):60-65.

[5]秦晟昱.基于FPGA的多路复接器设计与实现[D].长沙:西安电子科技大学,2014.

[6]YANG Yi-kang,LI Xue,LIU Lei.640 Mbps High-Rate Frame Multiplexer and its multi-channels control rule for CCSDS Principal Network[C]//.Proceedings of the 8th World Congress on Intelligent Control and Automation,2010:4442-4445.

[7]陈观兴.高速可重构复接器的设计和实现[D].北京:中国科学院大学,2009.

[8]张燕超.基于可编程片上系统的复接器设计[D].北京:中国科学院大学,2012.

Design of greedy dynamic digital multiplexer and its analysis of time delay

SHI Li-guo1,2,WANG Zhu-gang2,XIONG Wei-ming2,HOU Hong-jie1,2

(1.Center for Space Science and Applied Research of Chinese Academy of Sciences,Beijing 100190,China;2.University of Chinese Academy of Sciences,Beijing 100190,China)

In order to save channel resources,asynchronous digital multiplexer,which can multiplex different rate,different burst time slot digital source,has been widely applied.Aims to reduce the maximum extent possible source packet data transmission delay,improve channel utilization,design scheme of a greedy asynchronous dynamic digital multiplexer is proposed.The priority scheduling strategy of sources is given too.Two kinds of multiplex model are described by hardware description language.Simulations for greedy dynamic multiplexer and virtual channel multiplexer,under the condition of different physical frame length and two source model,have been carried out by Modelsim.The simulation results show that,for the average transmission delay and delay jitter,the greedy dynamic multiplexing is superior to the virtual channel multiplexing,and is more effective in saving resource of source cache.

digital multiplexer;virtual channel;average transmission delay;delay jitter

TN914.3

A

1674-6236(2016)02-0142-04

2015-06-22稿件编号:201506202

国家863计划资助项目(Y28021A220)

石立国(1984—),男,山东临清人,博士研究生。研究方向:信号与信息处理、信号检测与估计。