基于5G无线通信的稀疏码多址接入系统的FPGA实现

2016-09-12宋春雪张学晨

宋春雪,文 萍,张学晨

(西安电子科技大学 通信工程学院,陕西 西安 710018)

基于5G无线通信的稀疏码多址接入系统的FPGA实现

宋春雪,文萍,张学晨

(西安电子科技大学 通信工程学院,陕西 西安 710018)

在理解无线通信多址接入的基础之上,提出了一种低复杂度的基于5G无线通信的稀疏码多址接入系统的FPGA实现方案,利用可综合的 Verilog语言在 QuartusII及 ModelSim平台下完成了电路的设计综合仿真及 FPGA验证,结果证明该设计实现功能完备,可以实际应用。

5G;SCMA;max-log-MPA;FPGA

中文引用格式:宋春雪,文萍,张学晨.基于 5G无线通信的稀疏码多址接入系统的 FPGA实现[J].电子技术应用,2016,42 (7):8-12.

英文引用格式:Song Chunxue,Wen Ping,Zhang Xuechen.FPGA implementation of the sparse code multiple access system based on 5G wireless communication[J].Application of Electronic Technique,2016,42(7):8-12.

0 引言

稀疏码多址接入(SCMA)是一种多址接入技术,也就是基站如何同时服务和区分多个用户的一种方式。现在的 2G、3G、4G无线通信系统中的多址接入方式是正交的,用户之间也是正交的,如TDMA、FDMA,这种正交多址接入方式的优点是整个系统相对简单,接收端可以不做多用户均衡,但不足是容纳的用户数量取决于正交的资源数量。因此,正交接入方式不能很好地适用未来5G大容量、海量连接低延时接入等需求。解决这个问题的一种简单想法是OFDM与CDMA结合,即在每个时频资源上以码分的方式叠加更多用户。由于每个资源块上叠加了N个用户,N是码字的数量,这导致译码端复杂度非常高。稀疏码多址接入(SCMA)就是应5G需求设计产生的一种非正交多址技术[1]。SCMA系统中稀疏扩频的概念,将用户的数据在频域上扩散在有限的子载波上,每个资源块上等效的叠加用户数会大大减少,这就为接收端实现低复杂度提供可能性。

在SCMA系统中,信息比特首先经过信道编码,编码后的比特经过SCMA调制码本映射成SCMA码字,码字以稀疏的方式扩频在多个资源块上,因此,其最大特点是非正交叠加的码字个数可以成倍大于使用的资源块个数。相比4G的OFDMA技术,它可以实现在同等资源数量条件下,同时服务更多用户,从而有效提升系统整体容量。本文中模拟6个数据流扩散在4个资源块的情况,也就是150%的过载。

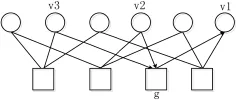

在发送端,每个用户有自己独立的码本,SCMA码本的设计过程可以看成稀疏扩频和多维调制的联合优化[2]。用户根据输入的比特串来选择码本中不同的码字,将编码比特直接映射为复数域多维码字,然后不同用户的码字在相同的资源块上以稀疏的扩频方式非正交叠加。本文直接使用文献[2]中的码本来编码,即6个用户分布在4个资源块上,tanner图如图1。

接收端利用扩频的稀疏性进行低复杂度的多用户联合检测,并结合信道译码完成多用户的比特串恢复[3]。

本文简化的上行链路SCMA系统总体设计框图如图2所示。

图1 码本tanner图

图2 简化上行链路SCMA系统设计框图

1 SCMA译码器的设计原理

SCMA系统的性能主要取决于SCMA码本设计和译码器设计。因此好的译码器十分重要。最大联合后验概率(MAP)检测是最优的多用户联合检测,但由于巨大的存储量,较高的复杂度往往不能在实际中使用。由于SCMA中低密度扩频的结构,可以采用近似于最大似然比(ML)检测性能的低复杂度的消息传递算法(message passing algorithm)[4]。

消息传递算法的基本原理就是将一个计算困难的问题分解成许多容易计算的子问题。译码器的最终目的在于计算每个比特的后验概率,因此在迭代过程中消息传递算法的基本运算就是基于先验概率和图模型结构对外概率和后验概率的估算[5]。SCMA译码器设计流程图如图3所示。

图3 SCMA译码器总体设计框图

译码器包含输入缓冲、残余信号f计算、功能节点FN更新、变量节点 VN更新、输出似然比 LLR等模块,控制部分iter_ctrl负责协调整个译码器的工作。译码器的工作流程是:当接收到带有高斯噪声的信号r后,首先通过fn(.)函数计算条件概率进行初始化,然后功能节点FN与变量节点VN沿着相连的边进行信息迭代更新,满足最大迭代次数后,变量节点输出信息比特的似然比作为turbo译码的输入,SCMA译码完成。整个过程主要由以下三步完成。

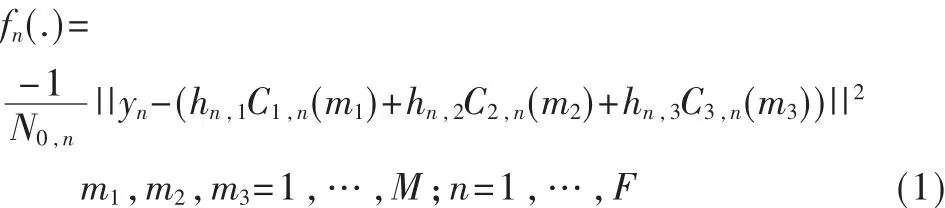

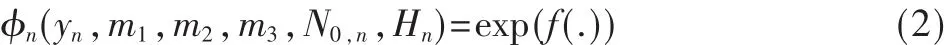

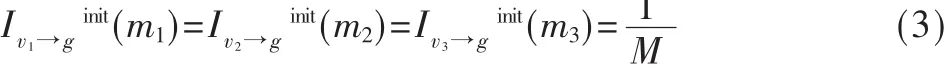

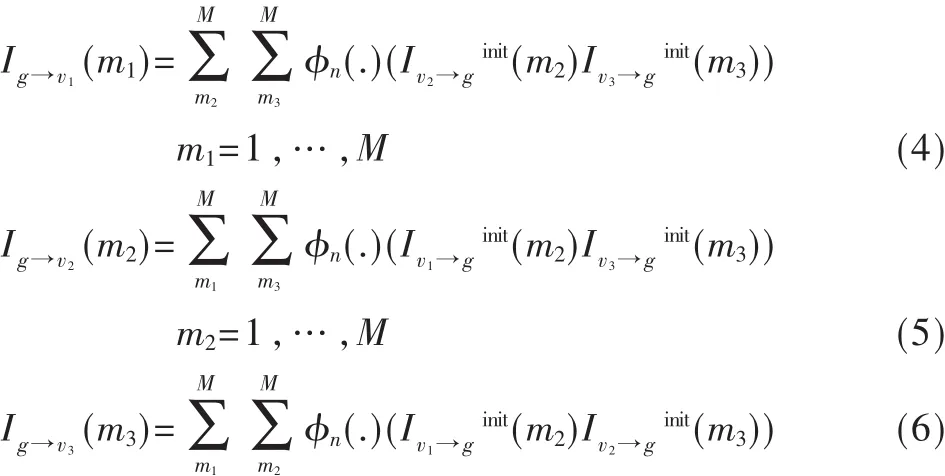

1.1初始化条件概率

给出用户k在资源n的信道增益h_n=1,变量节点k在资源节点 n上发送码字 m_k的符号 C(k,n)(mk),噪声功率 N0,n,可以用 fn(.)函数计算包含各种可能性的残余信号。 令 fn(.)=fn(yn,m1,m2,m3,N0,n,Hn),则:

在高斯噪声下,φn是条件概率:

认为先验概率相等,即发送每个码字的概率相等,则:

1.2迭代消息沿边缘传递更新

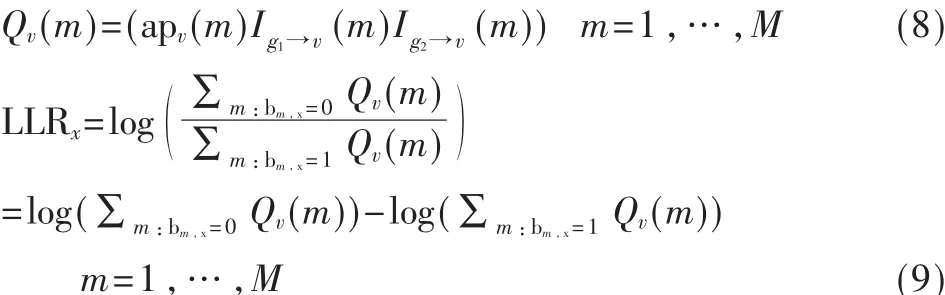

功能节点FN通过其相邻的变量节点VN传递的外信息更新,如图4所示。

图4 FN更新消息传递图

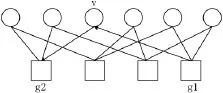

VN通过其相邻的FN传递的信息来更新,当d_v= 2,可以看作在 VN上信息的交换,如图 5所示。

图5 VN更新消息传递图

normalize使每个VN发送各个码字概率和为1。

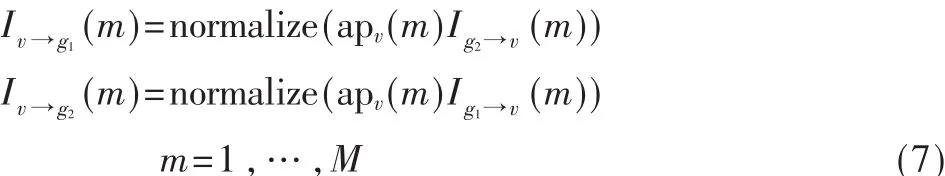

1.3一定的迭代次数后变量v处LLR输出

这样可以得到每个比特的对数似然比LLR,用于turbo译码的输入。

2 低复杂度MPA译码器原理与仿真

2.1寻找MPA译码的最佳迭代次数

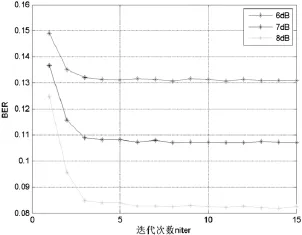

为了实现迭代次数与译码性能的平衡,对SCMA编译码模块单独进行MATLAB仿真,并在多个信噪比(Eb/ N0)下测试迭代次数对误码率的影响以求得到最优迭代次数。图6是Eb/N0=6 dB,7 dB,8 dB时,nframe=400帧,每帧1 000 bit的仿真图。

图6 迭代次数对误码率的影响

从图6可以看出,各个信噪比不变时,曲线走向大致相同;随着迭代次数的增加,误码率下降,但3次之后,误码率下降不明显,而且迭代次数的增加会消耗更多的系统资源。综合考虑,令迭代次数niter=5。

2.2max-log-MPA

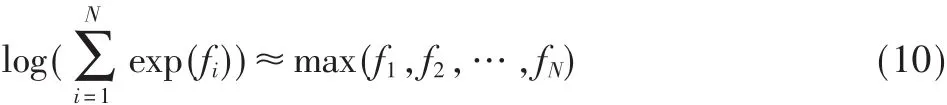

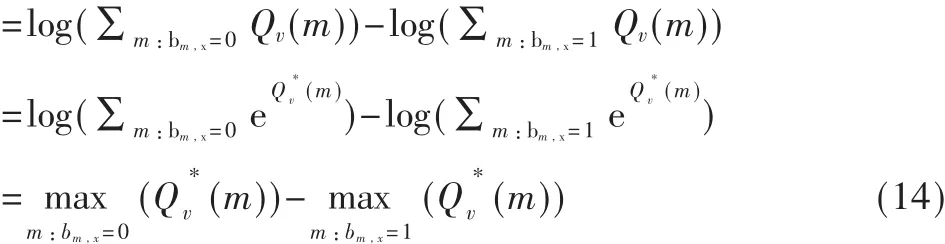

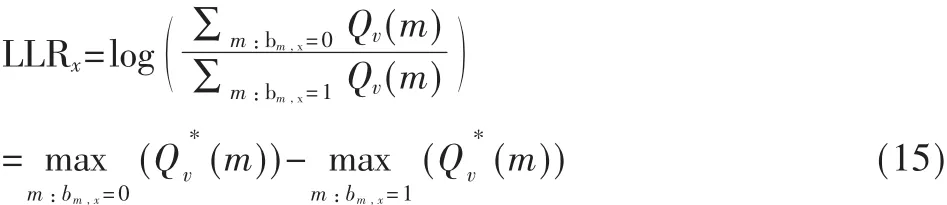

MPA算法虽然能以性能接近最优的方法进行译码,但是其中包含了太多的指数运算,在硬件实现上复杂度高,这会使其译码性能大大折扣。采用 Jacobi算法将考察变量都转换到对数域,去掉指数运算,即 max-log-MPA的SCMA译码:

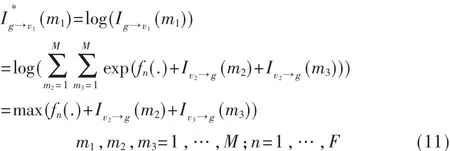

应用上面的公式,FN更新变为:

VN更新变为:

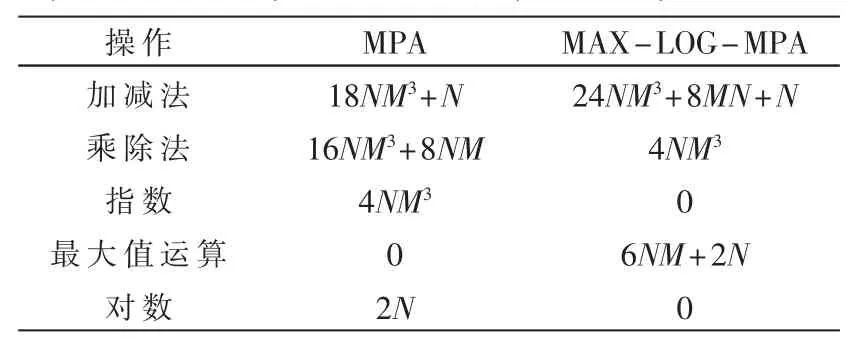

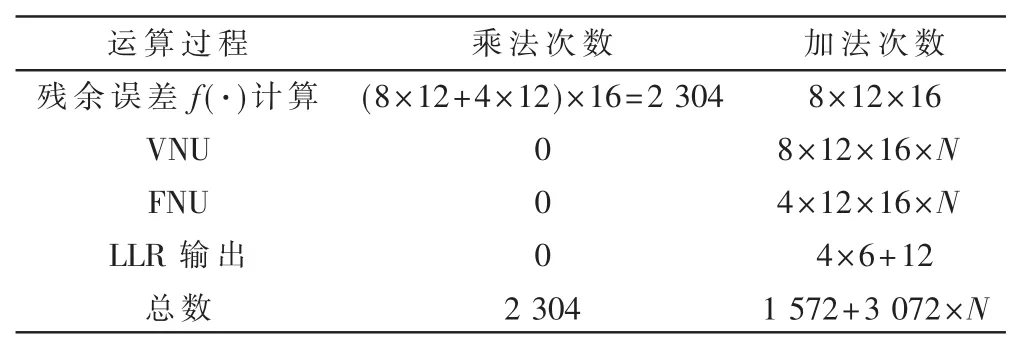

使用这种被称为MAX-LOG-MPA的译码算法虽然会有精度损失,但其复杂度大大降低,这使得在硬件上实现译码算法变得简单可行。表1显示出在本文中两种运算方法的N比特译码大致运算量,M为一个码本中码字的个数,可以看出MAX-LOG-MPA译码算法很大程度上降低了运算的复杂度,使得在硬件上实现变得可行、快捷。

表1 两种算法N比特译码运算量比较

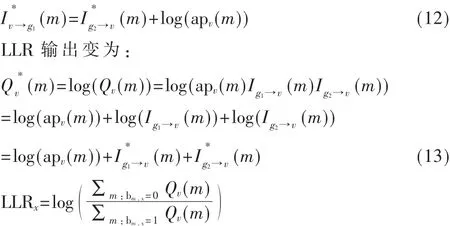

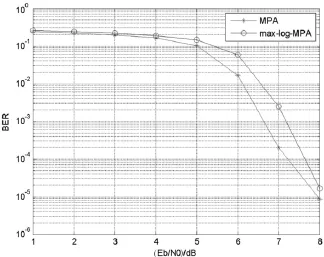

根据以上的化简公式,实现简化的SCMA系统,进行max-log-MPA仿真,并与复杂度较高的MPA译码相比较,MATLAB仿真条件为:每个用户发送帧数为nframe=40帧,每帧1 000 bit,SCMA的译码迭代次数为 5次,turbo译码迭代5次,码率 1/2,观察误码率与误帧率随着Eb/N0的变化,仿真结果如图7所示。

图7 MPA与max-log-MPA的BER v.s Eb/N0性能瀑布曲线对比

从图 7可以看出,相同条件下,max-log-MPA的性能比MPA大约差0.5 dB,但max-log-MPA硬件实现的复杂度大大降低,更容易在硬件上实现。

3 低复杂度的SCMA系统的FPGA设计与验证

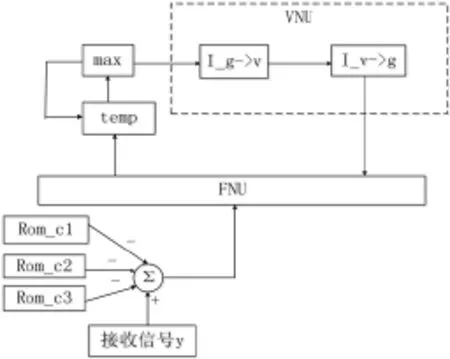

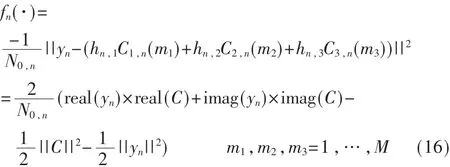

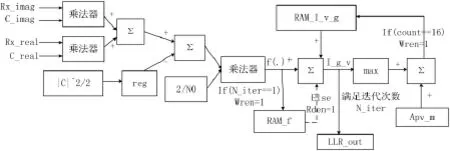

SCMA系统的性能主要取决于译码器的设计。为实现低复杂度SCMA系统译码器的设计,本文选择maxlog-MPA算法译码。max-log-MPA最重要的一部分就是功能节点(FNU)与变量节点(VNU)的信息迭代更新,FPGA设计如图8。

一个FN节点连接3个VN节点,每做1次功能节点更新(FNU)运算,需要输入3个用户的码本以及接收信号用来计算残留信号f,残留信号f与相连的变量节点传来的外信息Iv→g求和,来进行功能节点更新(FNU),在max-log-MPA下,找到输出的最大值作为一次FNU结束,输出的 Ig→v作为VNU的一个输入。变量节点更新(VNU)模块进行信息交换输出 Iv→g完成一次 VN节点更新,输出的值作为下一次迭代的输入。

图8 功能节点与变量节点一次信息更新的FPGA设计

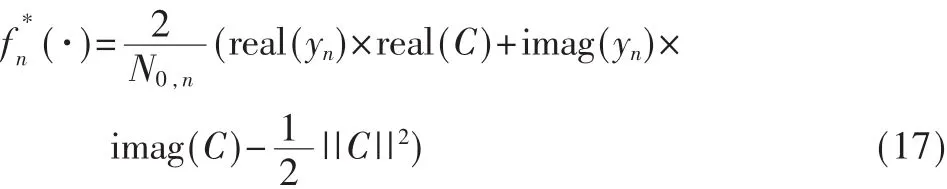

使用max-log-MAP译码算法,经过一定迭代次数后,由前面的推导:LLR似然比输出为:

由于输出似然比为最大值相减,那么Q中相同的值可以不用计算,这样就减少了计算量。即对一个数据译码时,接收信号|yn|2不变,先验概率 apv(m)不变,则计算残余误差时可以将这些省略,不会影响结果。

假设信道增益h=1,令C=C1,n(m1)+C2,n(m2)+C3,n(m3),则:

另外,由于每次迭代使用相同的f,第一次迭代时计算f(m1,m2,m3)的同时将其存放到RAM中,供以后的迭代使用,减小了运算量。

按照以上的思想,低复杂度SCMA译码器硬件实现结构如图9。

图9 SCMA译码器硬件实现结构

图10 低复杂度SCMA译码器资源使用情况

表2 每次SCMA译码的运算量

按照以上的结构完成系统设计,选用Terasic DE5-Net 的Altera Stratix V GX FPGA(5SGXEA7N2F45C2)器件综合时,SCMA译码器的资源使用情况如图10;表2显示了在设计中 1次 SCMA译码(输出 2 bit)所需要的乘法和加法运算次数,N为迭代次数。

图11 SCMA系统发送端仿真波形

图12SCMA系统接收端仿真波形

图11、图12分别是SCMA系统发送端发送码字,接收端迭代译码仿真波形。发送端:用户根据自己的码本来选择输出码字,6个用户非正交叠加输出发送信号tx 在4个信道上。在接收端:利用接收信号rx计算残余信号f,从而进行功能节点FN与变量节点VN的迭代更新,达到一定迭代次数后输出各个比特的似然比。

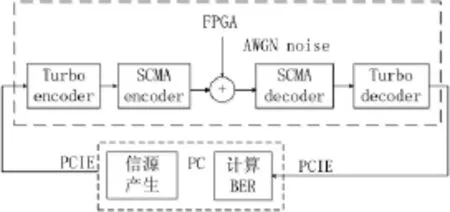

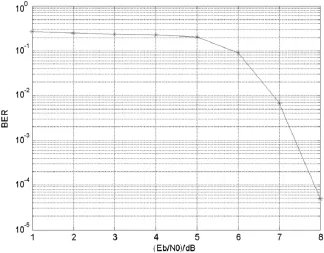

图13给出SCMA系统测试平台设计图,在PC上随机产生信源,经PCIE下传给FPGA上完成算法编码链路形成传输符号信息,对编码后数据加入高斯白噪声,然后经过SCMA算法译码链路,并回传PC解码结果并在PC上显示误码率BER。图14给出SCMA系统FPGA上测试结果。

图13 测试平台示意图

4 结果分析

本文在 max-log-MPA算法基础上进行简化计算,优化电路结构来降低运算复杂度,对SCMA系统的各功能模块进行了设计并在相关的软硬件平台下实现仿真验证。从仿真验证结果看,在FPGA上该系统实现功能完备,满足设计要求,系统性能在实际应用中是可以接受的。

图14 FPGA上ber vs.Eb/N0性能曲线

[1]NIKOPOUR H,BALIGH H.Sparse code multiple access[C]. In IEEE 24th PIMRC,2013.

[2]TAHERZADEH M,NIKOPOUR H,Bayesteh A,et al.SCMA Codebook design[C].IEEE VTC-fall,2014.

[3]AU K,Zhang Liqing,NIKOPOUR H,et al.Uplink contention based SCMA for 5G radio access[C].IEEE Globecom 5G workshop 2014.

[4]HOSHYAR R,WATHAN F P,TAFAZOLLI R.Novel lowdensity signature for synchronous CDMA systems over AWGN channel[J].IEEE Transactions on Signal Processing,2008,56(4).

[5]WU Y,ZHANG S,CHEN Y.Iterative multiuser receiver in sparse code multiple access systems[C].IEEE ICC 2015.

FPGA implementation of the sparse code multiple access system based on 5G wireless communication

Song Chunxue,Wen Ping,Zhang Xuechen

(College of Communication Engineering,XIDIAN University,Xi′an 710018,China)

Based on the understanding of the multiple access in the wireless communication,an implementation scheme of the sparse code multiple access system with a low complexity based on 5G wireless communication is put forward.By using synthesizable Verilog language in the Quartus II and ModelSim platform,the simulation of SCMA system and FPGA verification are realized. The results prove that the design can achieve perfect function,and it can be applied in practice.

5G;SCMA;max-log-MPA;FPGA

TN911

A

10.16157/j.issn.0258-7998.2016.07.002

宋春雪(1992-),女,在读硕士,主要研究方向:无线通信。

文萍(1990-),女,在读硕士,主要研究方向:无线通信。

张学晨(1992-),男,在读硕士,主要研究方向:无线自组网协议研究。

2016-03-21)