基于4DSP+FPGA架构数据处理板设计

2016-09-12董选明

董选明

(中国电子科技集团公司第三十八研究所,安徽 合肥 230088)

基于4DSP+FPGA架构数据处理板设计

董选明

(中国电子科技集团公司第三十八研究所,安徽 合肥 230088)

为了满足超高性能数据处理以及低功耗、简单可编程性的应用,设计了一款基于TI TMS320C6678芯片和Xilinx公司XC5VSX95T芯片的4DSP+FPGA架构的数据处理板,同时设计了高带宽的数据输入输出接口以及相关的时钟、电源和复位电路,并通过具体的硬件电路实现。该数据处理板可广泛应用于航空设备、车载设备、恶劣条件下工作的特种设备,将有效提高设备的数据处理性能。

数字信号处理器;现场可编程门阵列;串行高速输入输出接口;复杂可编程逻辑器件

中文引用格式:董选明.基于4DSP+FPGA架构数据处理板设计[J].电子技术应用,2016,42(7):29-33,37.

英文引用格式:Dong Xuanming.A digital processing board design based on the architecture of 4DSP and FPGA[J].Application of Electronic Technique,2016,42(7):29-33,37.

0 引言

随着数字信号处理器(Digital Signal Processor,DSP)和现场可编程门阵列器件(Field-Programmable Gate Array,FPGA)的发展,DSP+FPGA架构在数据及信号处理系统中的应用愈来愈广泛。传统的DSP芯片一般采用冯-诺依曼(Von Neumann)结构或某种类型扩展,此种结构本质上是串行的,当遇到需要处理的数据量大且处理速度高,但对运算结构相对较简单的底层信号处理算法来说显不出优点,适合采用FPGA硬件实现。因此,采用DSP+FPGA架构的系统可以将二者优点结合起来,兼顾速度和灵活性,既满足底层信号处理要求,又满足高层信号处理要求。

德州仪器(TI)推出 TMS320C66x系列最新数字信号处理器TMS320C6678与 TMS320TCI6609,是目前具有最高定/浮点运算能力的一代数字信号处理器,为开发人员带来业界性能最高、功耗最低的DSP。TI TMS320C6678多核DSP非常适合需要超高性能、低功耗以及简单可编程性场合的应用。TI不但为 HPC(High Performance Computing)提供免费优化库,无需花费时间优化代码,即可便捷地实现最高性能,而且还支持C语言与OpenMP等标准编程语言,因此开发人员可便捷地移植应用,启动 C66x多核 DSP的开发[1],充分发挥低功耗与高性能优势。为了满足超高数据处理性能、低功耗以及简单可编程性场合的应用,设计了一款基于 TI8核高性能 DSP芯片TMS320C6678和Xilinx公司FPGA芯片XC5VSX95T的数据处理电路模块,在6 U尺寸的模块上设计了4片高性能 DSP,定点运算处理能力可达 1 280 GMAC,浮点运算处理能力可达640 GFLOP,并设计了大容量DDR3内存(每片DSP内存为1 GB,共4 GB)和2 GB的固态存储,使得其可实现高性能、高数据吞吐量的定点/浮点运算。

模块设计了大吞吐量的串行RapidIO(Serial Rapid IO,SRIO)和千兆以太网,对外与其他模块进行数据通信,数据带宽达60 Gb/s,使得大数据量的输入、大数据量处理和输出成为现实。

1 电路总体设计

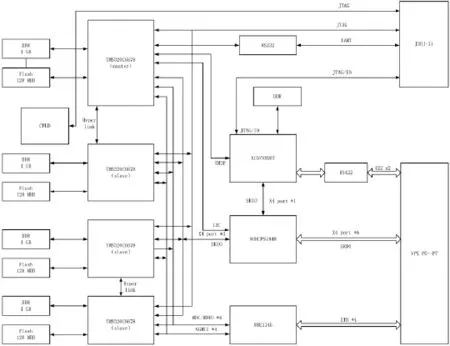

数据处理模块的电路总体设计基于 4×DSP+FPGA架构,电路总体设计框图如图1所示。

图1 数据处理模块电路总体框图

从功能上看,数据处理模块可分为DSP小系统、FPGA模块、RapidIO数据交换模块[2]、以太网模块、AD转换模块、各电平转换模块及其他电源、时钟和控制逻辑等辅助电路,加上 DSP、FPGA等必要的驱动程序和板内的控制逻辑,形成一个完整的、一体化的数字系统硬件平台。

1.1DSP小系统

DSP小系统主要包含:DSP芯片组、DDR3内存、Flash数据存储、RS232接口、SRIO接口、SPI(Setial Peripheral Interface)接口。

如图1所示,第一个DSP小系统作为主系统,其他3个DSP系统作为从系统。4片DSP之间的通讯如下:在启动过程中,从 DSP给主 DSP送 1个 GPIO(General Purpose Input/Output)信号,通过电平方式表示已经启动起来。系统启动后,从DSP的信息通过SRIO发送给主DSP。J30J-31为调试接口,对外提供DSP的JTAG(Joint Test Action Group)口(板内成菊花链[3])、串口、4个控制LED灯的GPIO口以及 CPLD、FPGA的JTAG加载口。4 个 DSP的 JTAG形成菊花链[4],连到调试接口 J30J-31上。同时,4个DSP的串口都连到调试接口上方便调试,该模块设计只用主DSP的串口。两个DSP之间,用超链接(Hyperlink)进行通讯[1]。

1.1.1DSP

电路设计采用 4片 TI公司的 TMS320C6678芯片,配合外围时钟、复位、DDR3、Flash等,为整个模块提供数字处理平台。TMS320C6678芯片为高性能八核数字信号处理器,外频采用 100 MHz,内核主频为 1 GHz,采用扩展温度型号,工作温度-40℃~+100℃。该芯片内部集成8个C66x CorePac DSPs的核,每个核工作在 1 GHz。在 C66x器件上,通过扩展 SIMD(Single Instruction Multiple Data)指令的宽度,提高了向量处理能力,可以处理128 bit的向量指令[1]。例如,QMPY32指令可以执行两个 32 bit数据向量的元素对元素相乘。

C66xDSP对浮点操作也支持SIMD。增强的向量处理能力加上原有的指令并行等级,DSP程序员通过应用 TI的 C/C++优化编译器可以开发出更高级的并行代码。每个核具有独立的32 K数据一级 cache和 32 K指令一级cache,共享 512 K二级 cache。C66xDSP存储单元接口支持DDR3 EMIF64内存,控制单元片内共享4 096 K SRAM存储空间,支持高速串行接口,包括 1路 SRIO接口、两路 PCIe接口、两路 SGMII(Serial Gigabit Media Independent Interface)以太网接口等。C66xDSP支持其他低速接口如UART(Universal Asynchronous Receiver/Transmitter)串口,24位寻址宽度的MIF16并行总线、SPI、I2C、GPIOs等。

1.1.2DDR3内存

每片 DSP设计采用 4片 MT41J128M16HA并联,提供64 bit数据位宽,共1 GB容量。MT41J128M16HA是Micro公司生产的 DDR3 SDRAM,规格为 16 Meg×16× 8 Banks,单片16位宽度,256 MB容量。

1.1.3Flash数据存储

Flash数据存储采用 Spansion公司 S29GL01G Flash芯片,16位宽度128 MB字节空间。一部分空间放置BOOT,主要用作存放操作系统的代码以及用户代码、用户配置和用户数据。通过CPLD控制存储系统的启动程序、系统程序和用户程序。DSP只能提供 24位地址线,Flash所需的高两位地址线通过CPLD来扩展。CPLD采用Lattice公司的LCMXO2280C芯片,在DSP和其他芯片通讯间实现电平转换功能。

1.1.4RS232接口

采用2片MAX3232作为RS232接口电平转换芯片,共提供4路RS232接口。DSP和链接器之间连接MAX3232芯片,完成TTL/CMOS电平的UART信号转换成标准的RS232信号输出和标准的 RS232信号转换成TTL/COMS电平输入。

1.1.5SRIO和SPI接口

SRIO接口通过 80HCPS1848芯片进行数据交换,实现与FPGA、3个从DSP及客户板通讯。SPI接口实现对AD9516的配置,给ADC提供可变的参考时钟。

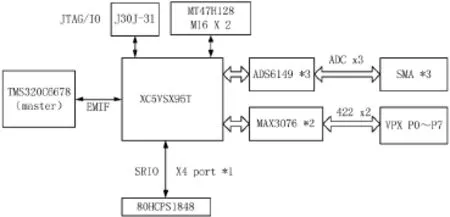

1.2FPGA模块

FPGA模块主要用做高速 ADC的算法处理,包含DDR2、SRIO、高速 ADC、RS422接口、JTAG/IO等接口部分。FPGA模块如图2所示。

图2 FPGA模块

1.2.1FPGA

FPGA模块设计采用Xilinx公司FPGA芯片XC5VSX95T。XC5VSX95T是 Xilinx公司的 Virtex-5 SXT系列FPGA器件,带有高级串行连接的信号处理逻辑,相对其他系列拥有更丰富的DSP资源。芯片XC5VSX95T有逻辑模块 160×54,最大 RAM模块 1 120 Kb,DSP48E 640个,CMT时钟管理 6个 RocketIO,GTP 16个,总 IObank 20个,最大使用 IO数 680个[5]。本电路采用 1.2~3.3 V I/O操作电压,14 720 slices,19个 bank,640个用户 IO,1PCIe,4 MAC,16个GTP,配合外围时钟、复位、FPGA启动加载电路等,为整个模块提供逻辑算法。

1.2.2数据缓存电路

数据缓存电路由2片Micron公司的MT47H128M16-SDRAM芯片构成,单片容量 2 Gb(16 M×16 bit×8 bank),共512 MB DDR2。该内存芯片14 bit行地址,10 bit列地址,1.8 V供电,最高频率 800 MHz,支持突发读写或者突发读单写,支持自刷新,64 ms内刷新 8 192次[6],挂在FPGA上为系统提供数据缓存、协助系统完成多路控制等功能。

1.2.3RS422接口

采用2片MAX3076完成RS422电平转换,提供2路RS422通信接口,支持单通道全双工,16 Mb/s,3.3 V工作电压,带15 kV ESD(Electro-Static Discharge)保护。

1.2.4JTAG接口

JATG信号直接由 FPGA引出到连接器 J30J-31,作为调试及客户指示灯接口。

1.3RapidIO模块

RapidIO模块为4个DSP及FPGA提供数据交换,同时,对外提供6个x4端口,使整个系统能够通过SRIO数据交换实现通讯。RapidIO模块电平转换功能如图 3所示。

选用IDT公司的RapidIO数据交换芯片80HCPS18-48CRMI完成数据电平转换。该芯片是一款高性能RapidIO交换芯片,符合串行 RapidIO2.1协议要求[2],拥有 48路 SRIO端口,可配置为 12×4、18×2、18×1的端口工作方式,传输速率可为 1.25 Gbaud、2.5 Gbaud、3.125 Gbaud、5.0 Gbaud或 6.25 Gbaud;芯片内部交换带宽达到240 Gb/s,提供无阻塞的全双工交换能力,可配置为短潜伏期(latency)的直通转发(Cut-Through)或存储转发(Store-and-Forward)数据流,最大可支持40个同时多点传送(multicast)和发送传递信号(broadcast),同时具有全局路由或本地端口路由。该芯片内核电压 1.0 V,IO电压 3.3 V,串/并化器电压 1.2 V[7]。

图3 RapidIO模块电平转换功能框图

1.4以太网模块

图1中每个DSP均可通过以太网同计算机通信,完成输入输出测试功能。以太网模块如图4所示。

图4 以太网实现框图

电路设计用MAVELL公司的PHY芯片88e1145。该芯片是一款4端口千兆以太网收发器[8],支持GMII、TBI、RGMII、RTBI以及SGMII接口,有4个RGMII时钟模式,1.25 GHz串/并化器应用于1000BASE-X光纤接口。每个收发器支持CAT5双绞线100BASE-TX、1000BASE-T全双工或半双工以太网、CAT3/4/5电缆10BASE-T全双工或半双工以太网,支持IEEE 100BASE-FX光纤网络。同时,每个端口支持 PECL(The PHP Extension Community Library)接口应用于 100BASE-FX,FEFI(Far-End Fault Indication)远距离错误指示,集成数字自适应均衡器、回声消除器和串扰消除器,自动 MDI/MDIX切换,用户配置port-by-port独立MAC接口,支持IEEE 802.3U自动协商,软件可编程LED模式,两线串行接口和MDC/ MDIO,CRC校验和包计数器,包生成器,自动校正 MAC接口输出。

1.5电源方案实现

根据数据处理板内电压种类和各芯片上电顺序需求分析以及提供的电源情况,电源设计方案如图5所示。

板上功耗最大的为 80HCPS1848芯片,其所需的电源有1 V、1.2 V、3.3 V。1 V由LTM4620和TPS74801DRCT提供,1.2 V由LTM4620提供,3.3 V由3.5 V经LTM4620提供。LTM4620输入电压范围为4.5 V~16 V,输出范围0.6 V~5.3 V,可实现单端 26 A、双端 13 A电流输出。TPS74801DRCT输出电压可调,电流1.5 A。

DSP所需电源有 1 V、1.5 V、1.8 V。1 V直接由UCD9222+UCD7242提供。1.5 V和 1.8 V由 5 V经LTM4620提供。 DSP有上电时序要求,UCD9222+ UCD7242通过软件控制4片DSP的上电时序,每个延时2 ms启动,内核电压上电完成后,再上 1.8 V和 1.5 V,1.8 V和1.5 V通过LTM4620芯片的track脚的容值不同来调整,同时,也将RUN脚拉到CPLD,由前级power good来推动后级的使能。

图5 电源树

对电源要求较高的ADC、PLL供电,均用LDR(Low Dropout Regulator)提供。

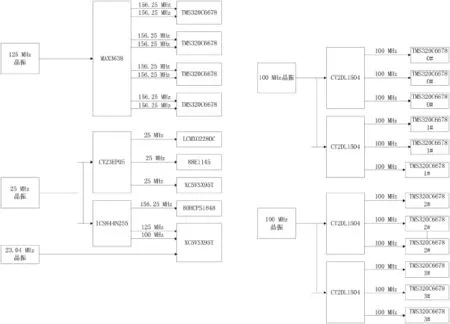

1.6时钟方案实现

图6为时钟方案图,DSP所需的时钟有 100 MHz、156.25 MHz。 156.25 MHz时 钟 由 125M 晶 振 通 过MAX3638提供,而3个100 MHz时钟则由外部100 MHz晶振通过CY2DL1504ZXIT提供。CPLD、PHY、FPGA配置所需25 MHz时钟,由外部晶振经过驱动器CY23EP05提供。RapidIO数据交换芯片所需的 156.25 MHz时钟由 25 MHz外部时钟通过 CDCM61004得到。FPGA芯片所需的时钟有23.04 MHz、100 MHz和 125 MHz,23.04 MHz由外部时钟提供,100 MHz和 125 MHz时钟由25 MHz外部时钟通过ICS844N255AkILft提供。

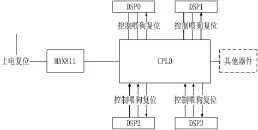

1.7复位电路

为了使电路可靠工作,复位电路特别重要,本电路板设计了上电复位、看门狗复位和芯片单独复位3种复位模式,图7为复位电路框图。上电复位是整板硬复位,使用专用复位芯片 MAX811、控制逻辑配合实现;第二种看门狗复位,由DSP给CPLD喂狗[9],CPLD内部做计时器,一旦异常,产生复位脉冲,给板内所有器件复位(包括DSP)。这种复位方式可通过脉宽控制进行调整:由DSP给CPLD喂狗,CPLD计时,一旦异常,由CPLD给复位芯片送出复位脉冲,复位芯片产生复位信号送给CPLD,CPLD将复位信号分发给整板,对所有器件进行复位;第三种通过DSP 给CPLD写寄存器,由CPLD独立复位各个芯片。

MAX811芯片内部自带上电复位时间控制,芯片产生的复位信号送入控制逻辑CPLD,由CPLD控制复位板上所有芯片,其最小 140 ms的复位时间可保证可靠地复位整个系统。手动复位由板上提供的按钮以及MAX811内建的施密特整形电路及延时输出电路,外加CPLD共同实现。看门狗复位,由CPLD内建看门狗控制逻辑,配合MAX811共同完成看门狗功能。芯片单独复位则是通过板内控制单元(CPU)通过写CPLD提供的复位控制寄存器的方式,实现各芯片单独复位。

2 结束语

基于4×DSP(8核DSP TMS320C6678)+FPGA架构设计的数据处理模块具有高速信号处理能力和高带宽的数据输入输出接口,处于国内领先地位,可用于高性能数据处理、信号处理、图像处理等场合。在设计中采用了宽温、低功耗的 DSP,使其具有高可靠性、低功耗、高密度、耐振动性以及宽温度工作范围的特性,可广泛用于航空设备、车载设备、恶劣条件下工作的特种设备,大大提高设备的稳定性和数据处理性能。

图6 时钟方案图

图7 复位电路框图

[1]Texas Instruments Data Manual.TMS320C6678 multicore fixed and floating-point digital signal processor[EB/OL]. [2015-12-15].http://www.ti.com.

[2]RapidIOTM.Interconnect Specification[EB/OL].[2015-12-18]. http://www.rapidio.org.

[3]美国国家标准学会(ANSI).ANSI_VITA 46.0-2007_American National Standard for VPX Baseline Standard[EB/OL]. [2015-12-18].http://www.vita.com.

[4]JTAG.国际标准测试协议[EB/OL].[2015-12-20].http:// www.jtag.com.

[5]Xilinx.Virtex-5 Family Overview[EB/OL].[2015-12-13]. http://www.xilinx.com.

[6]MachXO.Family Handbook(Lattice semiconductor corporation [EB/OL].[2015-11-19].http://www.datasheetarchive.com.

[7]Idt.80HCPS1848 Product Specification[EB/OL].[2015-12-19].http://www.idt.com.

[8]Marvell.Alaska®Quad Gigabit Ethernet Transceiver 88E1141/88E1145[EB/OL].[2015-12-13].http://www. marvell.com.

[9]张雪芹,杨立军,胡炫.TMS320F2812系统中的软件复位方法[J].单片机与嵌入式系统应用,2009(2):70-71.

A digital processing board design based on the architecture of 4DSP and FPGA

Dong Xuanming

(Institute of China Electronics Technology Group Co.,LTD.38,Hefei 230088,China)

In order to satisfy the application of high performance data processing,low power consumption and simple programmability,a 4Digital Signal Processor(4DSP)+Field-Programmable Gate Array(FPGA)architecture digital processing board was designed based on the chip TI TMS320C6678 and XilinxXC5VSX95T,with high bandwidth data input/output interface.This digital processing board implemented by specific hardware circuit will be widely used in aviation equipment,vehicle equipment and other special equipment worked in hard condition,which will effectively improve the data processing performance of the equipment.

DSP;FPGA;SRIO;CPLD

TN4

A

10.16157/j.issn.0258-7998.2016.07.007

2016-01-23)

董选明(1967-),男,本科,高级工程师,主要研究方向:数字模块和嵌入式计算机。