IEEE 1149.6标准在装备测试性设计中的应用研究

2016-09-06曾照洋刘萌萌中国航空综合技术研究所北京100028

苏 峰,曾照洋,刘萌萌(中国航空综合技术研究所,北京 100028)

IEEE 1149.6标准在装备测试性设计中的应用研究

苏峰,曾照洋,刘萌萌

(中国航空综合技术研究所,北京100028)

边界扫描技术是一种应用于集成电路的测试性结构设计方法,主要用来解决复杂电路的测试问题,而装备中交流耦合、差分信号普在高速数字互联网络普遍应用,对传统上基于直流的故障检测边界扫描技术提出了挑战。本文研究了IEE1149.6的基本原理及其在装备测试性设计中的应用,它完全兼容原有的IEEE1149.1标准,可以很好地对高速数字网络进行测试。

边界扫描;IEEE1149.6;测试性;机内测试

0 引言

测试性设计是为了提高产品自诊断和外部诊断能力,能方便有效地确定产品状态和隔离故障[1]。随着新一代武器装备的日益复杂化,对装备本身的故障诊断能力也提出更高的要求。IEEE 1149.1标准的提出为采用低速高复杂性数字集成电路和高密度表面封装等工艺技术的印制电路板的故障诊断问题提供了良好的解决方案,但是随着新装备电子设备集成化程度的提高,千兆位串行数据通信协议的使用高速增长,在该领域交流耦合差分信号的工程应用逐渐成为主流,特别是同步光纤网络通信,以太网以及带宽和同步光学技术等领域都广泛使用交流耦合技术,IEEE 1149.1越来越难以满足来自于测试、调试和功能等多方面的挑战。为了实现对上述网络的自动化测试,2001年5月,IEEE成立了1149.6工作组,并于2003年3月推出了IEEE 1149.6标准。该标准兼容了IEEE 1149.1标准,沿用已存在的边界扫描测试技术,具有高可靠性、高故障覆盖率和噪声抑制能力强等特点。我国装备在交流耦合差分传输信号测试性设计方面仍然缺乏研究与技术的推广,本文就分析了IEEE 1149.6在装备测试性设计中的适用性并提出了IEEE 1149.6的实现途径,可以对装备中电子设备交流耦合差分信号的测试性设计提供指导。

1 IEEE1149.6简介

1.1标准概述

IEEE 1149.6标准在IEEE 1149.1标准的基础上拓展了测试交流耦合或差分耦合互连所需的硬件,它可以兼容IEEE 1149.1标准,仍然沿用IEEE 1149.1标准结构进行测试,它们的基本原理相同,不同的是IEEE 1149.6针对交流耦合、差分互连被测信号制订了专门的测试结构及测试指令。

与IEEE 1149.1类似,IEEE 1149.6标准所需的基本结构包含以下几个部分[2]:

(1)TAP(测试存取通道):TAP是访问元器件内嵌入式测试支持功能的通用端口,能够提供PCB或IC测试所需要的数据。IEEE 1149.1标准定义的测试逻辑至少包括TCK(测试时钟信号)、TMS(测试方式选择信号)和TDI(串行测试数据输入信号)3个输入信号的连接和一个TDO(串行测试数据输出信号)连接。若TAP控制器不能上电复位,就要加上输入信号TRST(测试系统复位信号)的连接。TAP的所有的输入和输出必须是专用的。

(2)TAP控制器:TAP控制器实现JTAG规范的核心控制器,基本功能是产生时钟信号和控制信号,这些信号是指令寄存器和数据寄存器正常工作所要求的。它可以实现指令寄存器指令信号的装入功能、数据从TDI到移位寄存器及从TDO到移位寄存器的控制功能、数据的捕获/更新/移位操作功能。

(3)指令寄存器:主要提供在扫描路径访问数据寄存器所需要的控制和地址信号。

(4)数据寄存器:包括器件标志寄存器、旁路寄存器和边界扫描寄存器等,数据寄存器提供了边界扫描测试路径上的数据传输通道,整个工作过程中,及旁路寄存器BYPASS和扫描寄存器是必须参与的寄存器,其它的数据寄存器则可以根据需求选择。器件标志寄存器IDCODE就是一个典型的数据寄存器,IDCODE数据只能读出,它们是芯片生产厂商用来表示这种型号芯片的信息。

1.2交流耦合差分信号测试驱动器与测试接收器

在硬件上,IEEE 1149.6的驱动端在1149.1边界扫描单元的基础上添加了输出测试驱动器(OTSG),根据不同的测试指令,OTSG能够产生不同的测试信号。同时,IEEE 1149.6标准在相应的引脚上安置可观测单元(即输入测试接收器),进而允许测试系统从一对差分引脚中的负引脚上捕获数据。其次,IEEE 1149.6还增加了直流/交流选择单元,能够快速切换直流和交流测试方式。给AC/DC选择单元的相关寄存器写入配置数据就可以控制选择不同的测试方式。

1.3用于支持交流耦合差分信号测试的交流(AC)测试指令

IEEE 1149.6在IEEE 1149.1标准的基础上增加了新增指令EXTEST_PULSE和EXTEST_TRAIN,该指令不仅可对直流管脚进行符合IEEE 1149.1标准的EXTEST测试,更重要的是它实现了一种新的交流管脚测试方式。

2 IEEE1149.6适用性分析

IEEE 1149.6标准适用于单端直流信号、单端交流信号、直流差分信号、交流差分信号,支持有源终端、负载终端、有参考终端、无参考终端的测试,能够检测多种短路及开路故障。IEEE 1149.6将测试的管脚分为直流和交流两种类型:直流管脚指利用IEEE 1149.1就可以进行测试的类型;交流管脚则需要通过IEEE 1149.6才可进行测试。

2.1IEEE 1149.6适用的信号类型

该标准可用于检测单端直流信号、单端交流信号、直流差分信号和交流差分信号故障,能够支持有源终端、负载终端和有参考终端、无参考终端等的测试。1149.6将测试的管脚分为直流和交流两种类型,其中直流管脚指利用1149.1就可以进行测试;而交流管脚则需要通过1149.6才可进行测试[3]。

(1)单端直流信号:通过一个通道进行传输,通常用作设定静态参考电压。

(2)单端交流信号:如图1(b)为单端交流耦合连接示意图(电压源和终端电阻器也可以置于IC内部)。如图6所示,TX端为驱动器,RX端为接收器,在TX与RX之间只有一个信号通道,该通路上串联了一个电容,这种结构的通道即为单端交流耦合通道。

(3)直流差分信号:如图1(c)所示为基本的直流耦合差分通道结构,在TX和RX间的两个通路即为差分通路:在工作时,驱动信号在两个通道上表现为两个相位相反的独立信号,这种信号传输方式可有效降低信号传输通道中的共模噪声,RX将两个通道上的信号相减形成单信号流。

(4)交流差分信号:图1(d)为交流耦合差分通道结构示意图,图中的偏压网络与耦合电容可以在接收器电平与直流耦合不兼容时形成电平偏移器,保证系统的正常工作。

2.2IEEE 1149.6可检测的故障范围

1149.6与1149.1的目的相似,它们都是为检测电路板中所存在的缺陷或故障而制定。这些缺陷包括器件性能失效和器件的开路、短路等。1149.6主要针对差分和AC耦合通道的上述缺陷,包括TX、RX正负端的短路、断路,搭接,耦合电容的短路等。

如图2所示的交直流耦合电路,IEEE 1149.6主要检测的故障包括接收器引脚短路、驱动器引脚开路、耦合电容与接收器端开路以及驱动器引脚短路、接收器引脚短路、驱动器/接收器A与B引脚短路、驱动器A正或负与接收器B负或正引脚短路、驱动器正或负引脚与接收器负或正引脚短路、耦合电容两端短路等故障。

2.3IEEE 1149.6在装备测试性设计中的适用性分析

(1)装备中总线类信号常用的检测手段及其不足。目前装备中针对高速差分耦合信号(如PCI-E、SGMII、SATA总线)的检测方式仍然与普通的单端信号(如PCI、GMII、ATA信号)的检测方式没有大的区别,一般均采用了数据校验或握手机制检测的BIT设计方式。一般总线类信号的故障会发生在三个层次上,即物理层、电气层、数据层。物理层的故障一般包括信号通路上的器件的开路、短路故障等;电气层上的故障一般包括信号电压错误、阻抗匹配电阻参数漂移等;数据层的故障一般包括数据信号时序错误、输出电平错误等。这些器件层的故障传递至功能电路级的故障表征一般为总线信号无输出、总线信号输出错误、总线信号传输不稳定。在功能电路级上,单端直流信号大部分故障发生后均能直接导致传输数据的错误,通过数据校验方式或握手机制可以检测到故障是否发生,但是交流耦合差分信号的故障具有一定的隐蔽性,如差分信号一端开路或短路、耦合电容的短路等,这些器件级故障并不能够直接导致数据的错误,而是会影响数据传输的稳定性,这种不稳定的故障类型在复杂环境下(如高低温、高强度电磁干扰等)有可能会变的非常致命。

(2)支持IEEE 1149.6的芯片及工具。IEEE 1149.6标准的提出,交流耦合差分信号提供了成熟的BIT设计思路。在2003年该标准提出之后,很多公司都推出了支持IEEE 1149.6标准的芯片和相关技术工具,IEEE 1149.6逐步得到了广泛的应用推广。

目前市面上已存在较多支持IEEE1149.6标准的芯片,如TI公司开发了一系列的芯片SCAN15MB200、SCAN15MB200EVK、SCAN90004EVK、SCAN90CP02等。Altera公司在自己的芯片上也集成了支持IEEE 1149.6边界扫描的功能单元,如Arria ⅡGX芯片上的高速串行接口(HSS)收发器单元就完全支持1149.6的交流测试模式。另如NSC公司推出1.5Gbps的2x2低电压差分信号传输(LVDS)模拟交点开关SCAN90CP02,具备符合IEEE 1149.6标准的测试能力,可以配合TAP控制器完成符合IEEE 1149.6的测试。

Goepel的最新版(Ver.4.3)CASCON软件工具能支持IEEE 1149.6标准,它的目标是测试带有高速交流耦合和差分连接的数字电路,该软件工具可以支持测试很多电路元器件,如高速串行/解串IC和差分发射器与接收器。同时该公司为扩展超越传统IEEE 1149.1标准规定的边界扫描测试能力而开发的ScanFlex平台,不仅可用于AC边界扫描的IEEE 1149.6,还可支持用于片上编程的IEEE1532、用于模拟边界扫描的IEEE 1149.4,模块化的ScanFlex可在多达8个独立测试存取端口(TAP)中支持80MHz频率的串行扫描模式。ScanFlex系统包括一个边界扫描控制器、多个TAP收发模块和支持附加测试设备的可选I/O模块,其配置是两个独立可编程TAP,可支持32个动态数字I/O信号、2个模拟I/O信号、3个静态数字I/O信号和3条触发线[4]。另如Altera该公司发布的Medalist i3070系列5在线测试平台能够满足极小面积印制电路板的IEEE 1149.6边界扫描标准测试和有限测试应用。

(3)采用IEEE 1149.6标准技术的条件。IEEE 1149.6边界扫描测试系统与IEEE 1149.1结构基本一样,同样需要在被测电路板上设计能够支持IEEE 1149.6的电路,同时很多支持IEEE 1149.1标准的芯片也可以用于构建IEEE 1149.6标准边界扫描系统。为支持IEEE 1149.6边界扫描测试,设计的电路应尽量选取具有边界扫描单元的器件来构成扫描链路,以降低测试的成本及难度。若边界扫描器件不存在,则可以采用二次集成设计的方式自建符合IEEE 1149.6标准的边界扫描链路,这种方式实现难度较高,但设计出的测试系统可以覆盖更多不具备边界扫描单元器件,同样具有一定的实用价值。

目前装备中采用的新型芯片很多可以支持IEEE 1149.6标准,但是这些新片并没有建成边界扫描链路,不能够实现大规模的自动化测试,同时在装备中还存在大量年代较早的芯片,这新芯片出现之前IEEE 1149.6标准还未推出,这就使得在已研制的装备难以采用符合IEEE 1149.6标准的BIT测试电路。在新研的电子装备上,采用符合1149标准的芯片并构建起边界扫描链路的硬件成本并不高,具有较高的实用价值。

3 IEEE1149.6的实现途径

应用IEEE 1149.6标准的边界扫描测试系统的整体架构与IEEE1149.1基本一样。其测试系统的架构如IEEE1149.1研究报告的附录B所述。最主要的区别在于边界扫描控制器实现边界扫描测试逻辑时,能够实现交流测试指令EXTEST_TRAIN和EXTEST_PULSE的功能,使TAP进入RUN-TEST/IDLE状态,并控制在该状态的时间,以满足交流测试信号的脉宽TTest的要求。另外边界扫描测试软件需能够分析电路中差分、交流耦合网络的连接情况,并据此生成交流测试和直流测试的激励向量,分析故障情况。

3.1具有IEEE 1149.6边界扫描单元的电路测试性设计方法

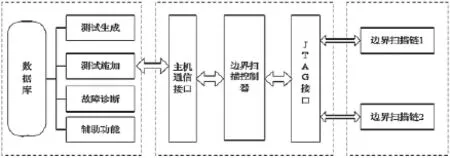

根据边界扫描测试系统功能和性能需求,边界扫描测试系统由主控计算机、边界扫描测试控制器和被测电路板组成。系统总体结构如图3边界扫描测试系统总体结构所示。

图3 边界扫描测试系统总体结构

PC机运行边界扫描测试软件,主要完成三个方面的工作:测试任务、人机交互和数据管理。

边界扫描测试控制器的任务是与计算机通讯,获取测试向量,从而选择相应的扫描链路,并驱动边界扫描测试总线,将测试向量加载到被测链路上进行测试;测试结束后,通知主控计算机读取测试响应数据。

被测电路板是完成可测试性设计的电路板。设计电路板时考虑可测性要求,使开发的电路板既能实现自身的功能,也可以使用边界扫描测试系统进行测试。

首先对电路板进行可测性设计,并获得相应的网络表文件和BSDL文件。然后建立一个测试电路板的工程,并添加对应的BSDL文件和网络表文件,对BSDL文件和网络表文件进行分析和信息提取,并将有用的信息放入数据库中。接着生成完备性测试向量并进行扫描链完备性测试,完备性测试无故障后再选择其他测试类型并进行测试。测试类型包括互连测试、簇测试和其他功能测试等。

3.2不含IEEE 1149.6边界扫描单元的电路测试性设计方法

若当前设计电路芯片不含具有边界扫描单元的芯片(简称BS器件),可以用同功能的BS器件置换原非BS器件,但如果同功能的BS器件不存在或设计代价较大,导致边界扫描器件置换难以进行时,则可以采用以下方法:

3.2.1二次集成设计

(1)将非BS器件按照功能聚类合并,构成相应的逻辑功能簇;

(2)按其确定的功能内核形成VHDL语言设计文本,在一定的设计工具平台(如MENTOR公司的BSDA系统)上对原内核进行边界扫描结构插入;

(3)经仿真形成新的VHDL描述的逻辑块设计文本;(4)在底层进行物理实现。

3.2.2自建扫描结构置入法

通过在非BS逻辑中插入边界扫描结构的BIST(built in self test)内核,附加额外边界扫描结构。

(1)利用VHDL语言对边界扫描结构的BIST内核进行描述;(2)应用可编程逻辑器件设计具有边界扫描能力的模块。

该模块应能完成IEEE1149.6标准所定义的所有功能,主要包括TAP控制器、指令寄存器、指令译码器、旁路寄存器、多路开关及大量边界扫描单元。

设计成功后,不仅能够实现非BS逻辑与外部电路的互连测试,而且其BIST能更好地支持非BS逻辑的功能测试。但这种方法设计较复杂,要求对IEEE1149.1标准的完全掌握,同时还要求所设计的结构能够支持通用指令,实际实现起来有一定难度。

3.2.3扫描器件置入法

是指将支持BS测试的BS芯片直接置入功能电路中,利用扫描器件本身自带的边界扫描单元实现对非边界扫描电路的可控又可测。

扫描器件置入法不需要自行设计符合IEEE1149.1的扫描结构,只需依靠扫描器件本身的边界扫描结构实现电路内部点的可测试性。实现较为容易,但可能会给电路带来部分冗余功能。应用时需权衡考虑功能设计与测试性设计,尽量实现硬件的复用。

根据扫描器件的置入方式的不同可分为两种类型:

(1)将所需观测点直接与扫描器件的管脚相连,利用其缓冲/驱动的基本功能和BS链,实现内部点的可控与可测;

若非边界扫描器件已连接到BS器件的IO上,其被BS单元包围,则可以将非边界扫描器件分组,通过电路板上存在的边界扫描器件来实现对非边界扫描器件的测试;

若非边界扫描器件功能上没有和任何BS器件相连,需要在设计中附加一些边界扫描器件,通过BS器件IO上的BS单元,才能进行测试。附加BS器件后,其仅在原电路的外围增加可控和可测点,设计较为简单。

(2)将扫描器件作为功能电路的一部分,嵌入到功能电路中,完成功能电路的部分功能,同时也达到了可控与可测的目的。当电路处于工作状态时,边界扫描器件正常工作。当电路处于测试状态时,置入的BS器件与其它BS器件一起组成串行扫描链路。

4 总结

IEEE 1149.1标准可以很好地解决器件直流引脚的测试问题,但是对于电路中普遍应用的交流引脚却是无能为力,而IEEE 1149.6标准的提出很好地弥补了IEEE1149.1这一短板,并能够做到与IEEE 1149.1很好地兼容,可以检测到交流耦合、差分信号传输路径上的器件开路、短路等多种类型故障。

目前国外对于IEEE 1149.6标准研究较多,技术相对成熟,在该标准提出之后,很多器件厂商都设计了符合该标准的芯片,同时也涌现出较多测试工具,而国内对于该标准的研究与应用步伐相对落后。由于IEEE 1149.6所能覆盖的故障类型(如差分管脚中正极管脚的开路、交流耦合结构中耦合电容的短路等)很多具有一定的隐蔽性,如不能及时做出诊断,势必会引起一系列安全隐患,所以有必要进一步研究IEEE 1149.6标准在装备测试中的应用。

在装备电子设备中用到的很多芯片本身就具有IEEE 1149.6边界扫描单元,在实际应用时只需将这些芯片互联起来构成边界扫描链路,通过芯片本身的JTAG口即可控制与读取被测芯片的引脚状态,以此来判断连接是否正常。对于不具备边界扫描单元的芯片,也可以自建边界扫描结构形成边界扫描链路,来完成相应的测试。

总之,应用IEEE 1149.6标准可以对装备中符合该标准的电路板和系统中的差分电路及AC耦合电路进行快速、准确的故障诊断,对于装备故障检测率及故障覆盖率的提升具有很大意义。

[1]田仲,石君友,系统测试性设计与分析与验证[M].第一版.北京:北京航空航天大学出版社,2003.

[2]吕彩霞.JTAG的设计与研究[D].北京:北京交通大学,2006.

[3]赵志宏,陈冬,李小珉.IEEE 1149.6可检测端口与故障判定[J].计算机测量与控制,2006,14(03):301-304.

[4]赵志宏,陈冬,李小珉.IEEE1149.6可检测端口与故障判定[J].计算机测量与控制,2006,14(03):301-304.

[5]雷加,刘华林.高级数字网络的边界扫描测试[J].电子测量与仪器学报,2004,18(z1):21-25.

[6]王石记,徐鹏程,杜影.适用于高级数字网络测试的边界扫描芯片特性研究[J].计算机测量与控制,2010,18(10):2234-2235,2284.

项目:总装备部技术基础合同项目:军用电子设备边界扫描测试系列标准研究,项目编号:HK30120132BZ77。

10.16640/j.cnki.37-1222/t.2016.10.254