基于51单片机软核的数字频率计设计

2016-08-31汤书森李欣吴琅尹岑

汤书森,李欣,吴琅,尹岑

(兰州大学信息科学与工程学院,兰州 730000)

基于51单片机软核的数字频率计设计

汤书森,李欣,吴琅,尹岑

(兰州大学信息科学与工程学院,兰州 730000)

以FPGA和51单片机软核为核心,设计了一个数字频率计,实现了频率、周期、时间间隔和占空比的测量。系统主要包含3个部分:整形放大电路、FPGA门控处理电路和显示电路,整形放大电路采用TI高速比较器TLV3051来实现整形放大,用FPGA搭建数字电路来测量各参数,通过LCD来显示所测参数的值。

FPGA;数字频率计;51单片机软核

1 方案论证与比较

1.1宽带整形放大电路方案比较与选择

方案1:整形放大电路先将信号放大成FPGA可检测的电压,然后通过整形把正弦波变成方波。由于要放大的信号为1 Hz~100 MHz,而信号的峰峰值为20 mV~1 V,所以必须将信号通过宽带放大器将小信号放大,然后通过整形电路将信号整形成FPGA可测量的方波。对于不同幅度的电压,放大的倍数不同,考虑到该硬件电路在短时间内较难完成,且成本较高,故不选用。

方案2:采用TI的TLV3051高速比较器,由于该芯片的响应时间为4.5 ns的rail to rail输出,整形后可直接作为FPGA的测试信号,故将它搭建为高频信号的整形电路,但由于高频比较器响应时间很短,对高频噪声很敏感,而低频信号上一般叠加有一定的高频信号,这就导致输出信号沿容易产生抖动,故测量低频信号时可采用LM393低频比较器对低频信号整形。该方案可以实现有效值10 mV~1 V以及10 Hz~100 MHz的信号放大整形。

综合比较,方案2更加简单易行,故采用此方案。

1.2参数测量模块的比较和选择

(1) 频率、周期测量

方案1:系统测频、测周期部分采用中小规模数字集成电路。中小规模集成电路应用技术成熟,能可靠地完成频率计的基本功能,但由于系统功能要求较高,所以电路过于复杂,而且多量程转换开关使用不便。

方案2:采用测频集成芯片。它只需要外接几个元器件,就可以构成一台体积小、成本低的多功能计数器,但由于其测量频率范围有限(0~10 MHz),不能很好地满足题目要求。

方案3:采用FPGA作为控制核心,门控信号在FPGA内部产生。FPGA是现场可编程芯片,极大地提高了设计的灵活性,测试使用的FPGA开发板含有20 MHz的外部晶振,可倍频至2 GHz。综合考虑,最终选定方案3。

(2) 时间间隔测量

方案1:通过测量两路信号的相位差,结合所测同频信号周期得出两路信号的时间间隔。该方案的关键部分在于硬件电路(包括整形、鉴相和A/D转换电路),低通滤波器的设计比较复杂,误差较大。

方案2:对两路测试信号进行异或操作,再在FPGA内对异或后的信号脉冲t的宽度进行计数。这种方案操作简单,可以同时保证低频和高频部分的精度。综上所述,选择方案2。

(3) 占空比测量

方案1:信号连接单片机定时器的捕获端口(上升触发)测量方波的周期T,双边沿触发测量高电平持续时间,两者比值即为占空比。该方式由于单片机自身时钟的限制,所测频率很难提高。

方案2:对占空比的测量可以通过测量正反两个脉宽的计数值来获得。对正脉宽计数值是N1,负脉宽计数值为N2,所以占空比为N1/(N1+N2)×100%。由于FPGA的时钟频率很高,可以有很高的精度和频率,所以选择方案2实现。

1.3显示模块的比较和选择

方案1:采用LCD12864液晶显示模块,优点是带有文字库,可以显示图像效果和8×4个汉字,价格比LCD1602稍贵。

方案2:采用LCD1602液晶显示模块,缺点是只能显示字母、数字和符号,不能显示文字,但是价格便宜、功耗更低,故选择方案2。

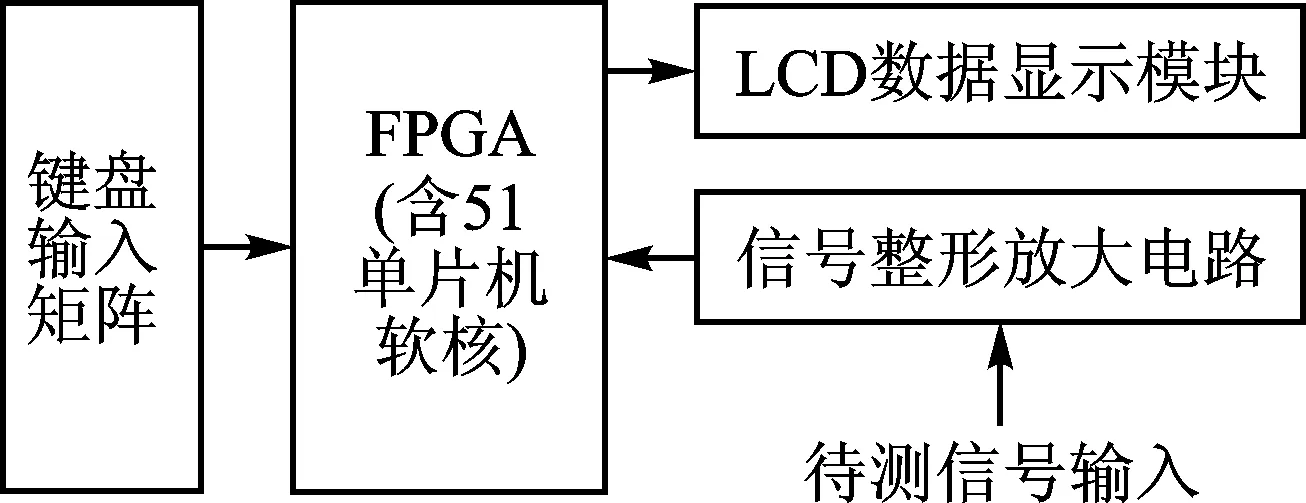

1.4整体实现方案

考虑到FPGA(含51软核)的编程的灵活性和使用51单片机的方便,实现方案(采用的开发板型号为KX_7C5E+),整体实现方案如图1所示。

图1 整体实现方案

键盘电路完成初始化、频率、占空比等测量的输入选择,然后通过FPGA完成处理,结果在LCD上显示。

1.5提高仪器灵敏度的措施

考虑到干扰和电路带来的问题,采用如下措施提高仪器的灵敏度:

① 采用同轴电缆;

② 采用高精度比较器;

③ 提高FPGA的时钟信号。

2 硬件电路设计

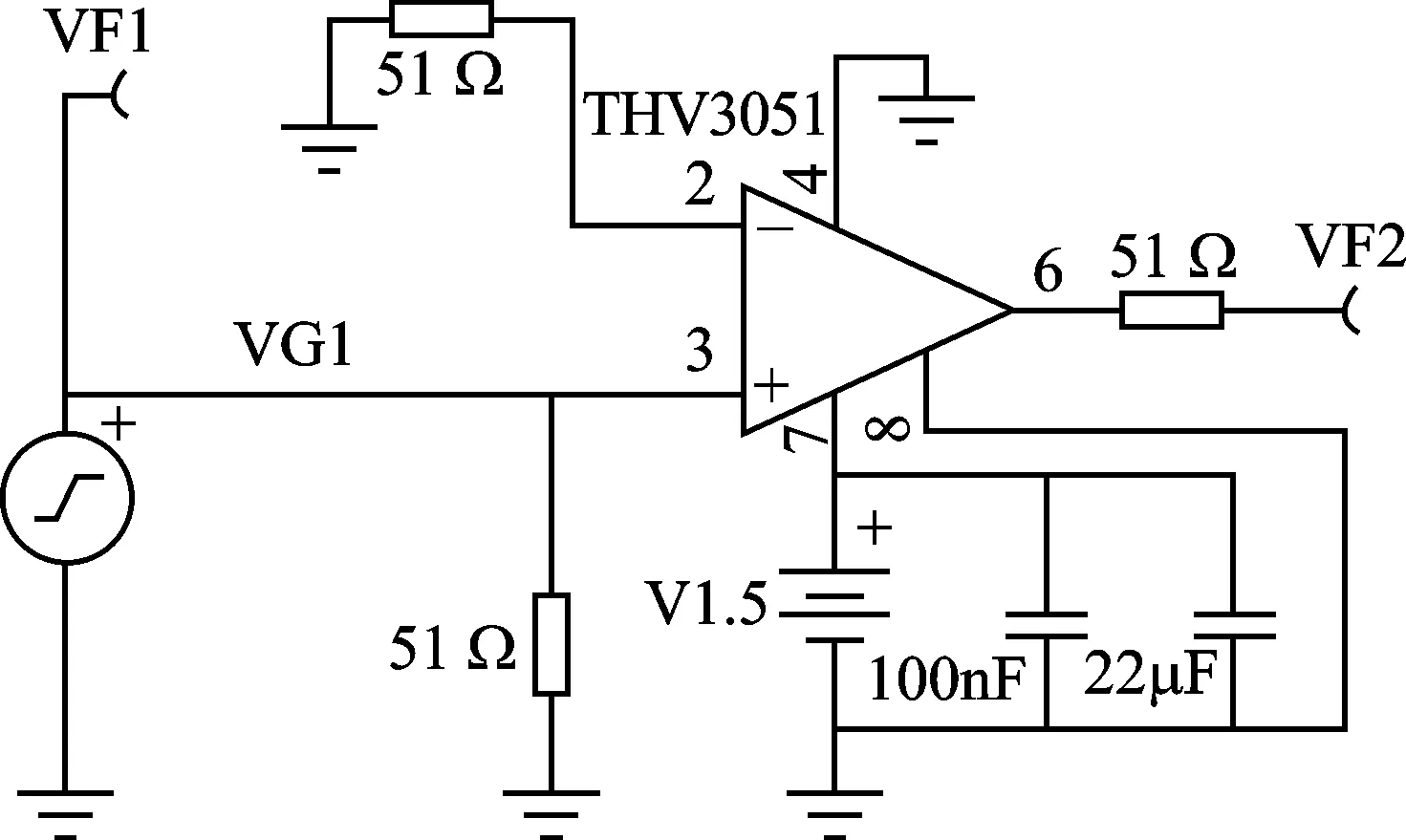

2.1比较放大电路

比较放大电路如图2所示,本电路的功能是对50 mV~1 V的高频交流小信号进行整形和放大。输入信号经过电压比较器正端和接GND的负端比较,由于THV3051是轨到轨推挽输出,当信号电压大于0时,输出正电源电压,当输入信号小于0时输出0。

图2 比较放大电路

2.2低频电压比较器

低频电压比较器功能是对50 mV~1 V的低频交流信号进行整形和放大,其原理同上。

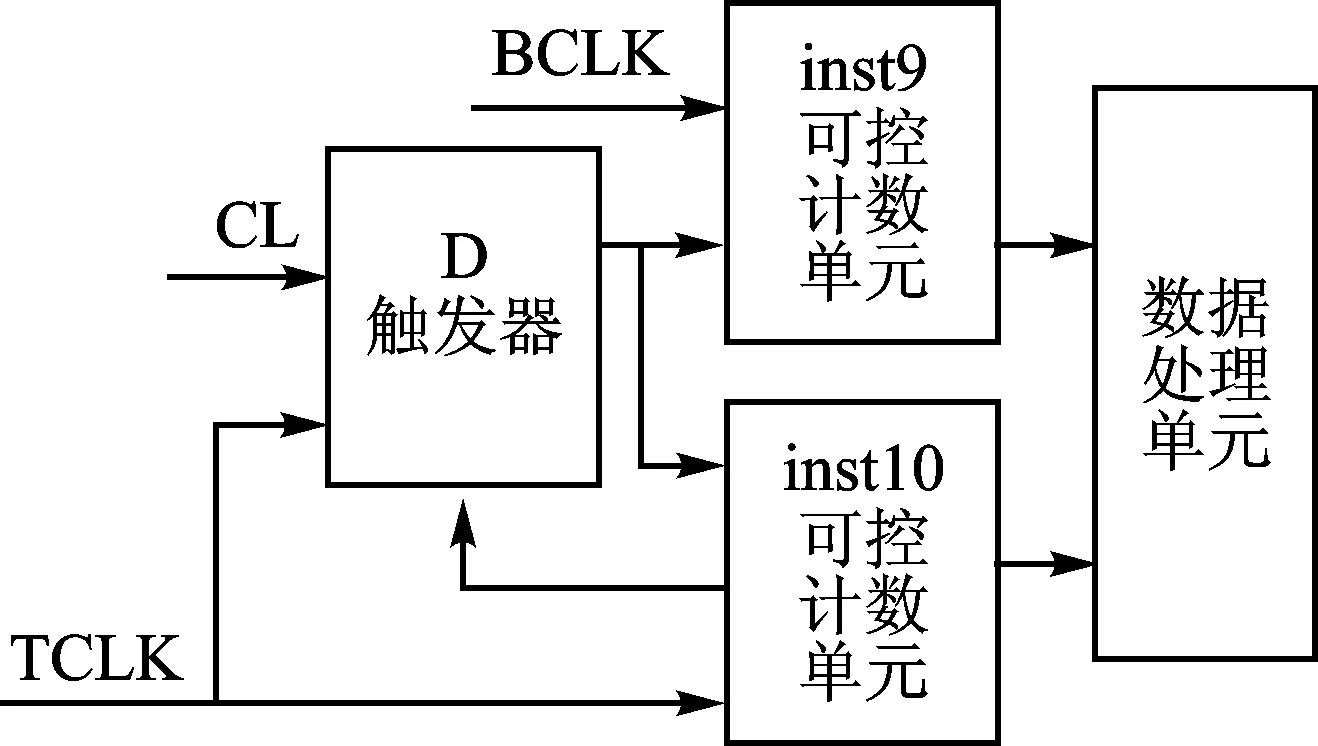

2.3频率测量电路

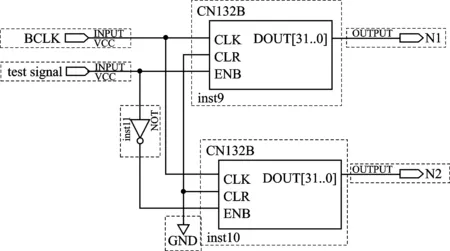

图3采用等误差测频法实现对待测信号频率的测量。预置门控信号是CL引脚,它是一个宽度为Tpr的脉冲,inst9、inst10是两个可控计数器,标准频率信号从inst9的时钟输入端BCLK输入,其频率为fcs。经过整形、放大后的被测信号从inst10的输入端TCLK输入,其频率为fx。当预置门控信号为高电平时,经整形后的被测信号上升沿通过D触发器Q端同时启动计数器inst9、inst10。inst9、inst10分别对整形后的被测信号和标准信号同时计数;预置门控信号为低电平时,经整形后的被测信号的一个上升沿将使这两个计数器同时关闭。

图3 频率的测量电路

设在一次预置门控信号为Tpr中,被测信号计数值为Nx,标准信号的计数值为Ns,则有下式成立:

Nx·Tx=Ns·Ts

即fx/Nx=fcs/Ns,于是有fx=(Nx/Ns)·fcs。

测出频率后根据公式T=1/f直接可得出周期。

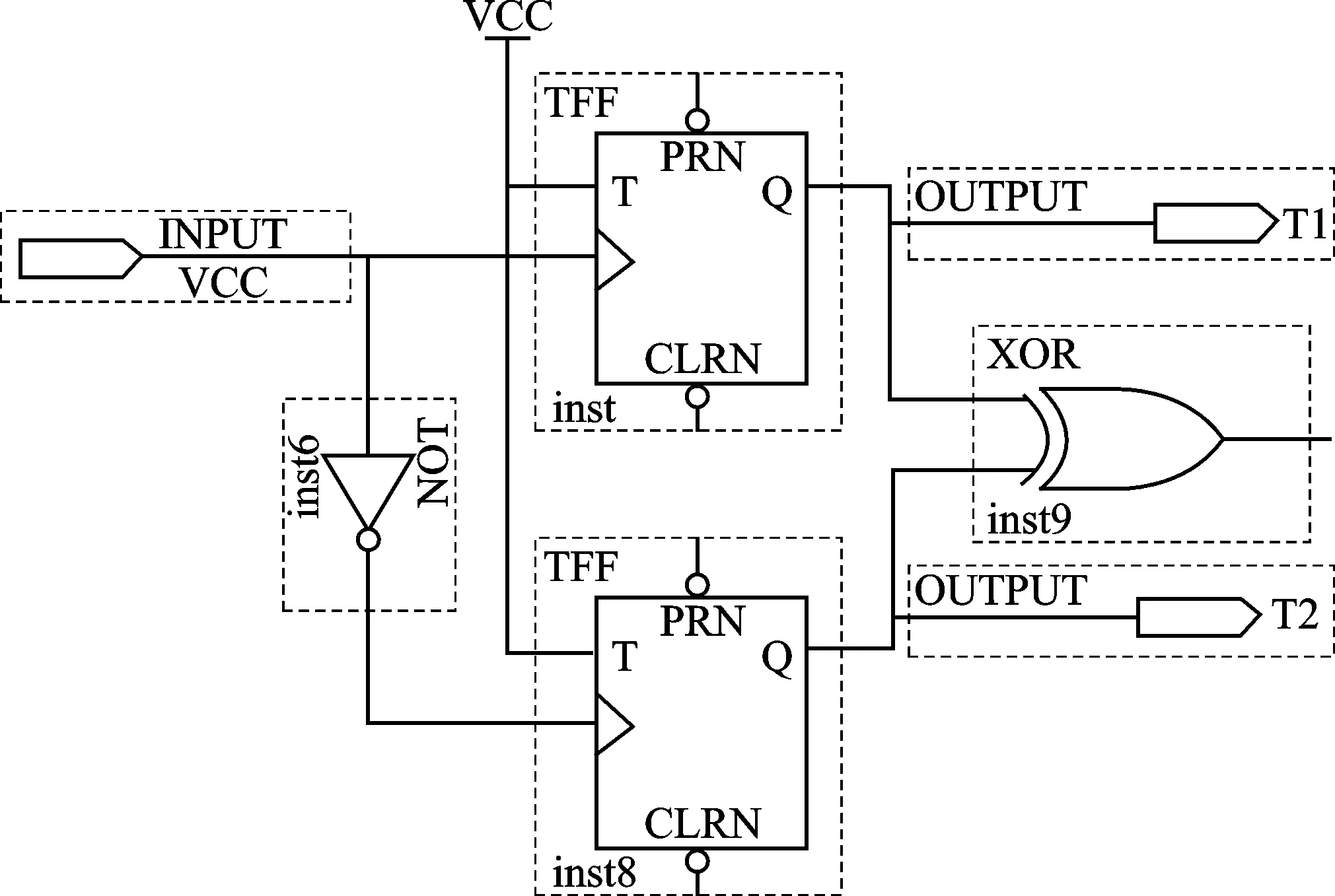

2.4时间间隔测量原理

T1和T2为两个被测的同频信号,T1或T2的上升沿到来时会触发与它相连的T触发器发生翻转,经异或门后输出的高电平即为脉宽时间t。时间测量原理图如图4所示。

图4 时间间隔测量原理图

对两路测试信号进行异或操作,再在FPGA内对异或后的信号脉冲t的宽度进行计数。其中BENA为计数器的使能信号,当BENA为高电平时计数器开始计数,当BENA为低电平时计数器停止计数。

2.5占空比测量原理

如图5所示,对占空比的测量可以通过测量正反两个脉宽的计数值来获得。设图5中inst9对正脉宽的计数值为N1,对负脉宽的计数值为N2,则周期计数值为N1+N2,于是占空比为:

k=[N1/(N1+N2)]×100%

图5 占空比测量原理

3 软件设计

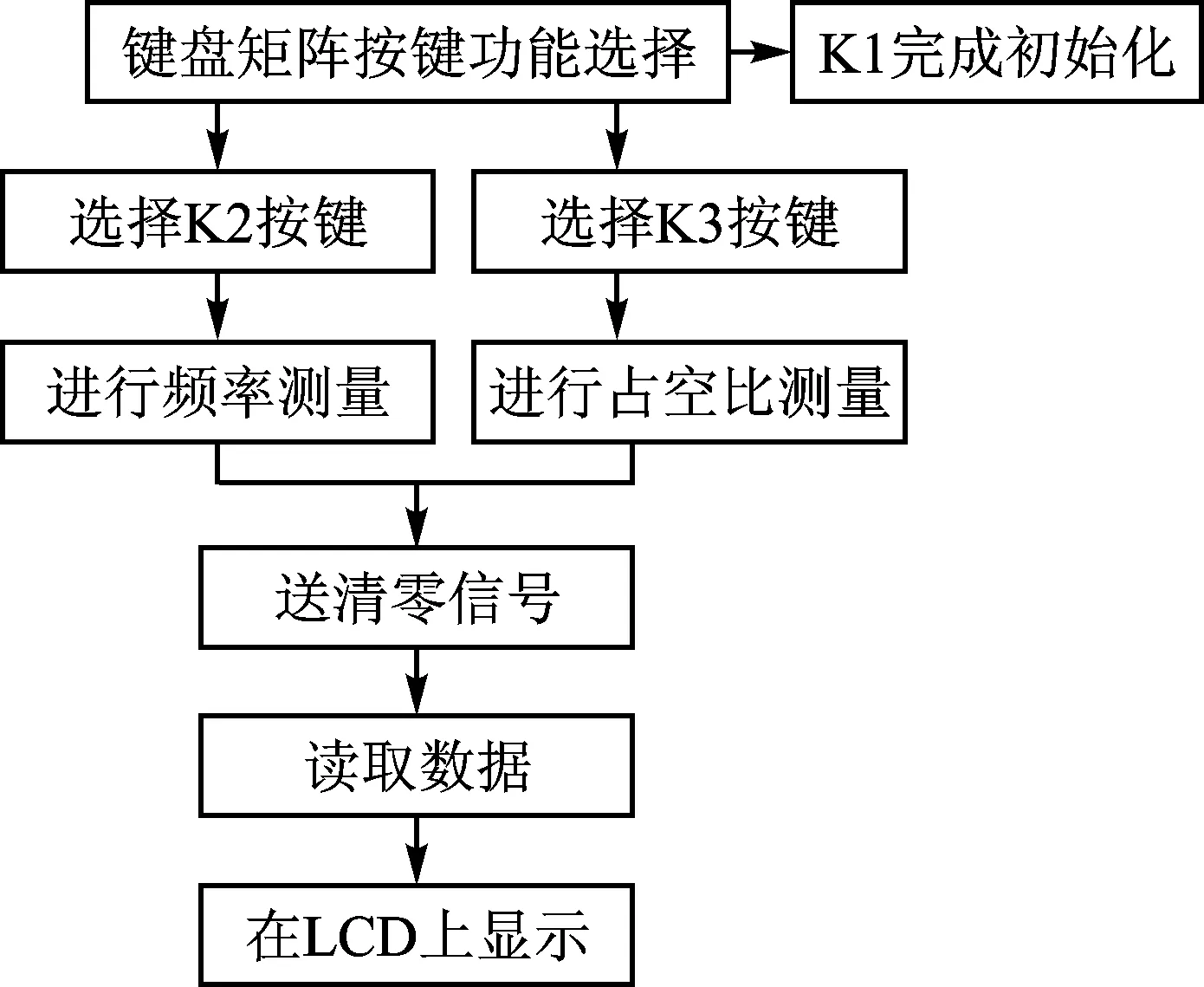

本系统主要功能由FPFA内部信号处理电路实现,软件部分主要是通过FPGA内部的51单片机软核,以及VHDL语言、C和汇编语言来实现相应的控制、数据处理和显示功能。整体软件实现流程图如图6所示。

图6 软件实现流程图

4 测试方案和测试结果

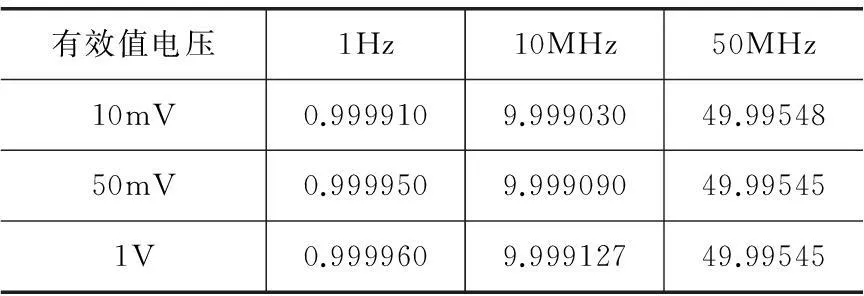

在测量有效值电压为10 mV、50 mV及1 V时,对应频率为1 Hz、10 MHz和50 MHz的测量值,从而评估仪器整体性能。

测试方案及测试条件:采用160 MHz双通道任意函数发生器、200 MHz示波器(GDS-2202A)、频率计FCA3000。

测试结果记录如表1所列。

表1 设定标准频率在不同有效电压值下的测量结果

结 语

基于FPGA设计的数字系统应用日益广泛,本文详细介绍了不同方案的比较和选择,最终设计了一个数字频率计,并完成了测量,充分体现了基于FPGA的51单片机软核在实现嵌入式系统方面的灵活性和高效性。

[1] 夏宇闻,黄然.Verilog SOPC高级实验教程[M].北京:北京航空航天大学出版社,2009.

[2] Peter J.Ashenden.Verilog 嵌入式数字系统设计教程[M].夏宇闻,夏嘉宁,译.北京:北京航空航天大学出版社,2009.

[3] 张洪润,张亚凡,孙悦,等.FPGA/CPLD应用设计200例(上、下册)[M].北京:北京航空航天大学出版社,2009.

[4] 郭天祥.C51单片机C语言教程[M].北京:电子工业出版社,2013.

[5] 阎石.数字电子技术基础[M].5版.北京:高等教育出版社,2005.

汤书森(高级工程师),主要研究方向为嵌入式系统与应用。

Digital Frequency Meter Based on 51 Microcontroller Soft Core

Tang Shusen,Li Xin,Wu Lang,Yin Cen

(College of Information Science and Engineering,Lanzhou University,Lanzhou 730000,China)

In the paper,a digital frequency meter is designed which is based on FPGA and 51 microcontroller softcore.The design achieves the frequency measurement,period measurement,time interval measurement and duty cycle measurement.The system mainly consists of three main parts:the shaping amplifier circuit,FPGA gating processing circuit and display circuit.TI TLV3051 is used to achieve shaping amplification,FPGA is used to build digital circuit to measure various parameters,and the LCD is used to display the values of the measured parameters.

FPGA;digital frequency meter;51 microcontroller soft core

TP39

A

(责任编辑:杨迪娜2015-11-02)